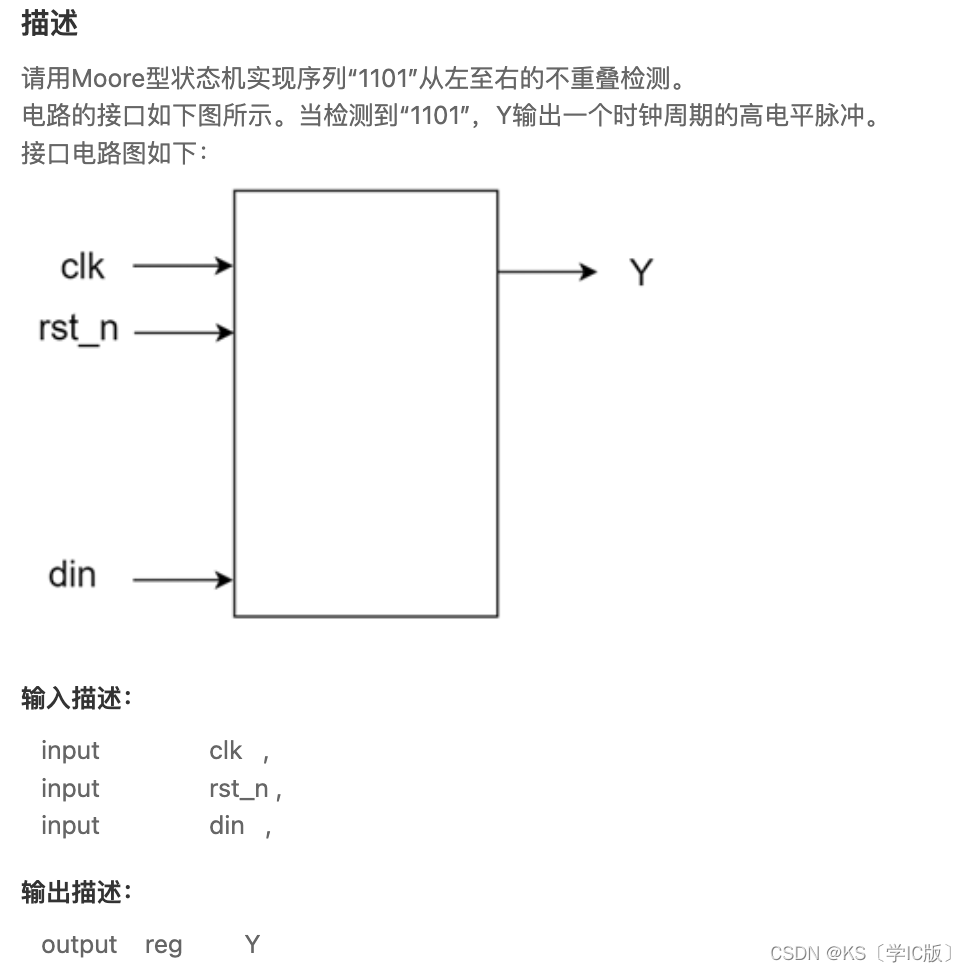

「Verilog学习笔记」序列检测器(Moore型)

发布时间:2023年12月30日

专栏前言

本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网

`timescale 1ns/1ns

module det_moore(

input clk ,

input rst_n ,

input din ,

output reg Y

);

parameter S0 = 0, S1 = 1 , S2 = 2, S3 = 3, S4 = 4 ;

reg [2:0] nstate, state ;

always @ (posedge clk or negedge rst_n)

if (!rst_n) state <= S0 ;

else state <= nstate ;

always @ (*)

case (state)

S0 : nstate = din ? S1 : S0 ;

S1 : nstate = din ? S2 : S0 ;

S2 : nstate = din ? S2 : S3 ;

S3 : nstate = din ? S4 : S0 ;

S4 : nstate = din ? S1 : S0 ;

default : nstate = S0 ;

endcase

always @ (posedge clk or negedge rst_n)

if (!rst_n) Y <= 0 ;

else if (state == S4) Y <= 1 ;

else Y <= 0 ;

endmodule

文章来源:https://blog.csdn.net/m0_54689021/article/details/135306444

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- ESP8266 PlatformIO Arduino中为墨水屏制作u8g2自定义字库

- 数据资源工具如何批量自动下载数据

- ThinkPHP为什么用PHP+Swoole协程模式部署运行

- 【C#】面向对象的三大特性,还记得吗,简单代码举例回顾

- 07-JVM调优工具详解及调优实战

- 第28节: Vue3 条件渲染

- idea中java单元测试报错

- linux 如何生成rsa,Linux 生成rsa 格式不对

- 《动手学深度学习》学习笔记 第7章 现代卷积神经网络

- 基于星辰处理器的全志XR806开源鸿蒙开发板上手体验