如何正确使用RC滤波网络

????????众所周知,最有效的滤波电路应靠近噪声源放置,滤波的作用是对噪声电流进行及时有效地阻止和转移,实际设计中,工程师经常使用高的串联阻抗(电阻、电感和铁氧体)阻止电流,并使用低的并联阻抗(电容)转移电流。通常情况下,我们期望滤波器可以对噪声信号衰减大约30~40dB,然而又必须注意不能让滤波器过于影响有用信号。

????????本文以最常见的RC滤波器为例,详细讲解该如何根据工作信号选择合适的滤波器参数。

????????RC滤波器通常会被用于载有连续时钟信号的振荡电路中,因为,根据EMC的基础理论,带有快速上升沿的连续周期信号是产生EMI问题的主要来源,因此,工程师们总是会想方设法的抑制时钟信号的边沿变化速率但又不能过于影响信号完整性,如图所示,其电阻和电容的摆放位置取决于源阻抗和负载阻抗,驱动器往往具有很低的驱动内阻,因此R需要尽可能地靠近驱动端进行放置,C作为高频噪声的低阻抗通路,应放置在R之后的输出链路中。

????????首先,一种简单易行的计算方法,就是在时钟频率基波的5~10倍处设定幅值衰减3dB的频率,通常,R会使用27~51ohm的小电阻,然后利用如下公式计算C的值:

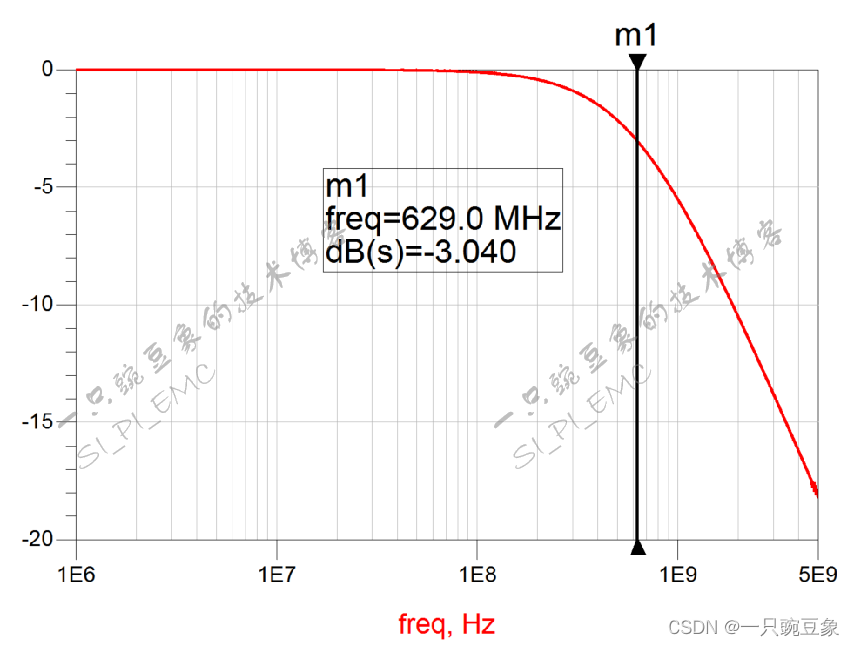

????????以时钟频率为125MHz为例,设计时,取其5倍的谐波频率=5*125=625MHz,并且,取R=33ohm,则根据上式,C≈7.72pF,如下图所示,该组合下交流信号仿真的结果,显示的-3dB的频点与计算保持一致。

????????然后,再观察下RC网络加入前后对时域信号的影响,发现,加入RC网络后,信号边沿明显减缓,初始设定为150ps,最终减缓到了570ps,但仍然保持了大约3.2ns的平顶时间,此时,就需要根据规格书中相关时序的定义,来判断这样的边沿衰减是否仍然符合设计要求。

????????最后,观察RC网络加入前后信号频谱能量的变化是否达到预期,因为,需要在满足信号时序的同时,确保滤波网络确实对能量衰减达到了设计要求。

????????对上图数据进行整理,取前7次谐波的数值进行了对比分析并发现,在625MHz之后,RC网络对于能量的抑制作用开始逐步体现出来,不要小看这减少的3dBmV,在EMI实验中,这样的改善往往对测试结果产生“天翻地覆”的影响。

????????以上都是在理想的情况下进行的数据选择,实际中,当元器件在PCB上放置时,不可避免地带来寄生参数,会影响滤波器的性能,因此,一定要减少多余的互连走线长度和通过多个过孔耦合与信号返回平面的连接,才能够减小寄生耦合以及旁路路径的阻抗,从而得到性能较好的滤波器,同时,具备精确的仿真建模能力,也会使得滤波器的设计变得更为可靠。

????????除此之外,还不得不考虑传输线的影响,如果在设计中添加了一段50ohm阻抗的长走线,对于RC滤波器来说,其结构已经发生了改变,如下图所示,C1所面对的已经不是高阻抗,而是传输线的50ohm特性阻抗,此时,滤波器不仅不能发挥其应有功能,甚至还会影响到输出端的信号质量。

????????按照上图的电路结构,进行了以下三组数据的对比,可以发现,当走线越长时,在发射端的滤波电容C值,将会给输出端的信号带来明显的电压振荡,但是,这些振荡会随着传输线效应的减小而减弱(走线长度由1000 mils变为100 mils)。

????????综上所述,RC滤波网络更适合于时钟振荡电路的优化,比如晶体振荡器,如果要用在长距离走线的时钟线路上,就必须保证不会产生明显的传输线效应。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 时序预测 | Matlab实现SSA-CNN-BiLSTM麻雀算法优化卷积双向长短期记忆神经网络时间序列预测

- C语言关键字------(2)

- docker jar包打成镜像并推送到仓库

- 逻辑回归(LR)----机器学习

- 【Java】【Stream流】排序

- 【论文笔记】3D Gaussian Splatting for Real-Time Radiance Field Rendering

- uniapp上传图片功能怎么实现?

- 这次,数据泄露的目标受害者指向了---救护车服务公司

- GBASE南大通用-CodeFirst 模式

- vue实现点击复制功能方法封装demo。