数字集成电路VLSI复习笔记2

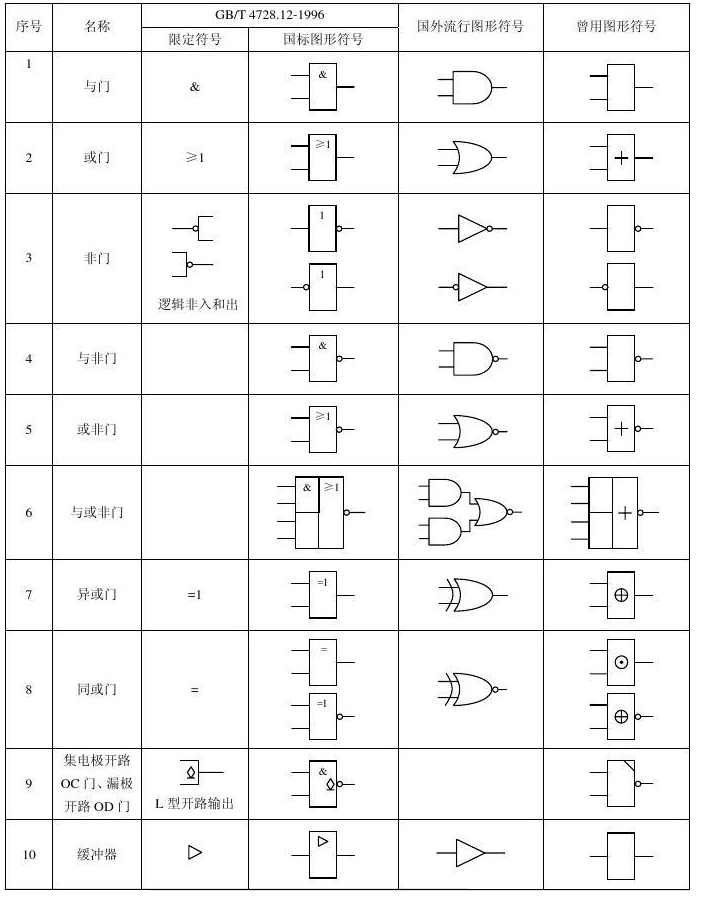

逻辑门符号

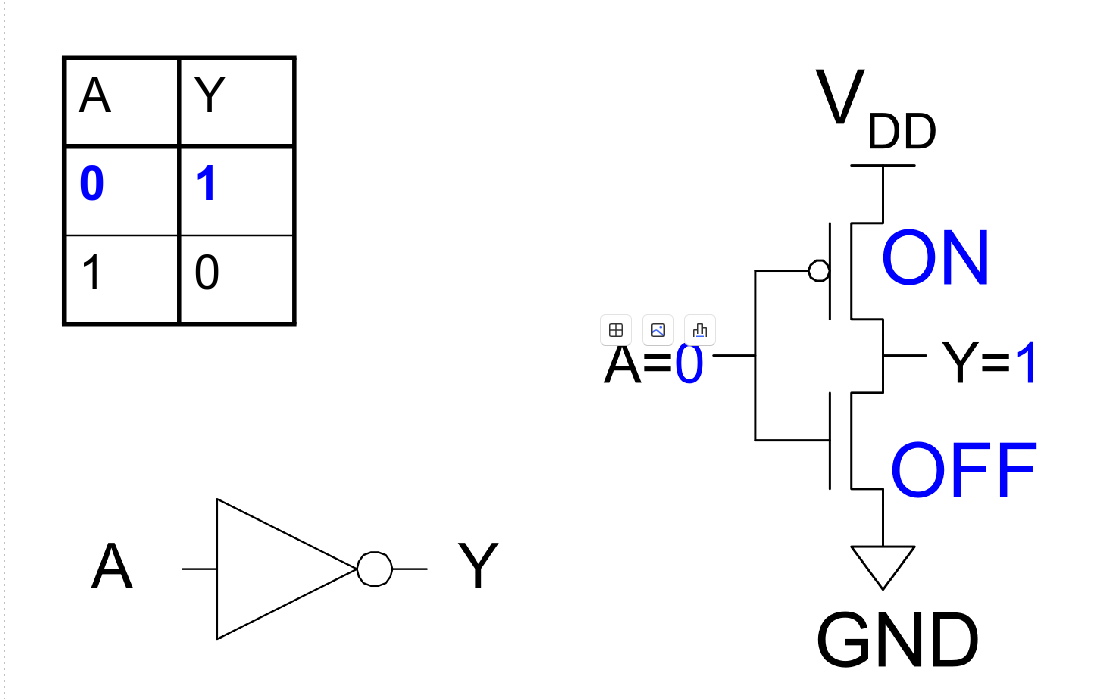

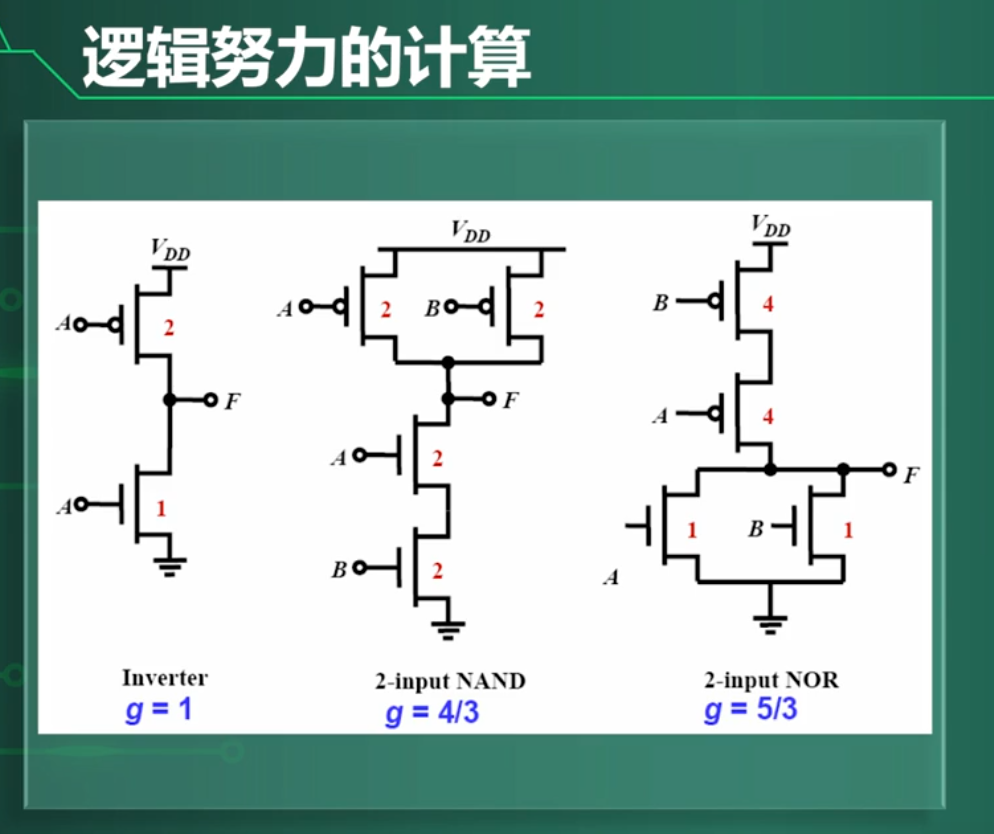

Inverter

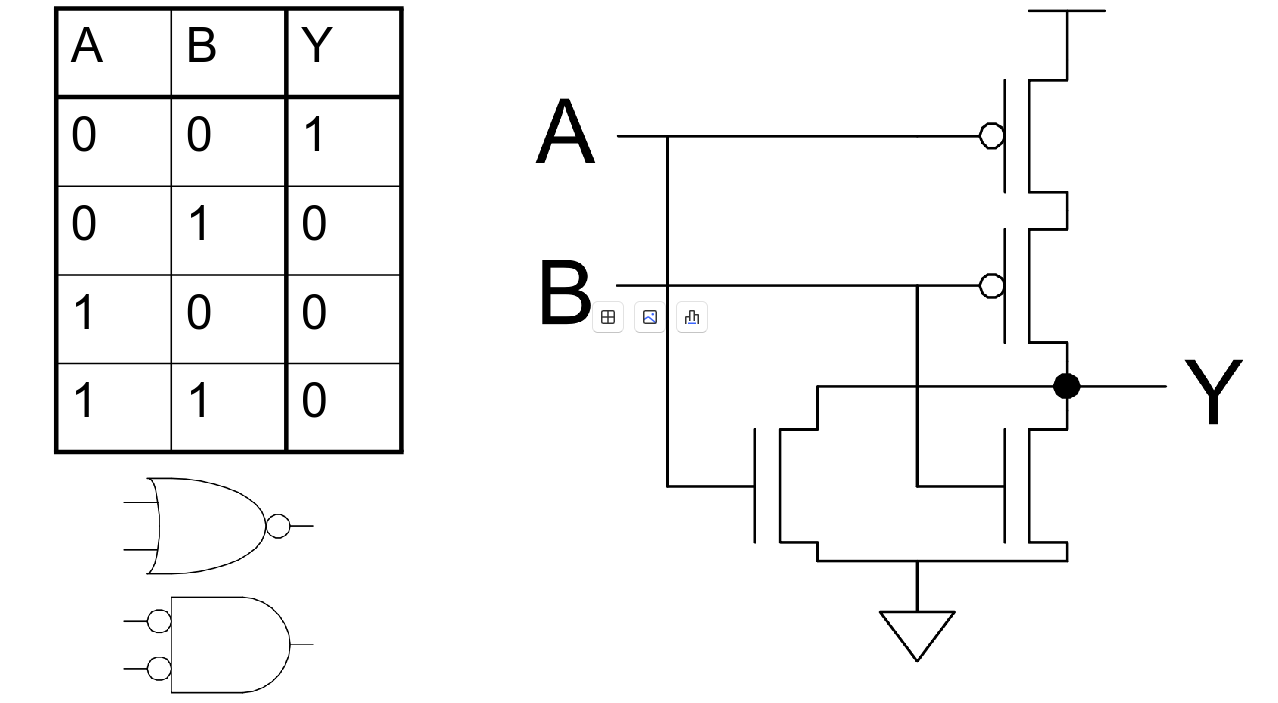

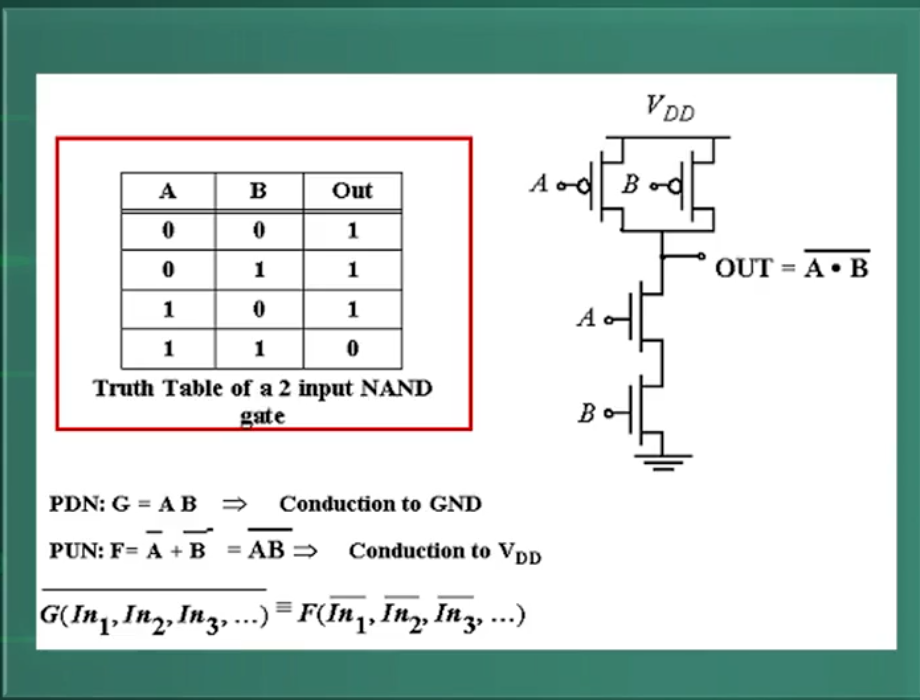

CMOS NAND Gate

CMOS NOR Gate

MOS Capacitor

nmos cutoff

Linear

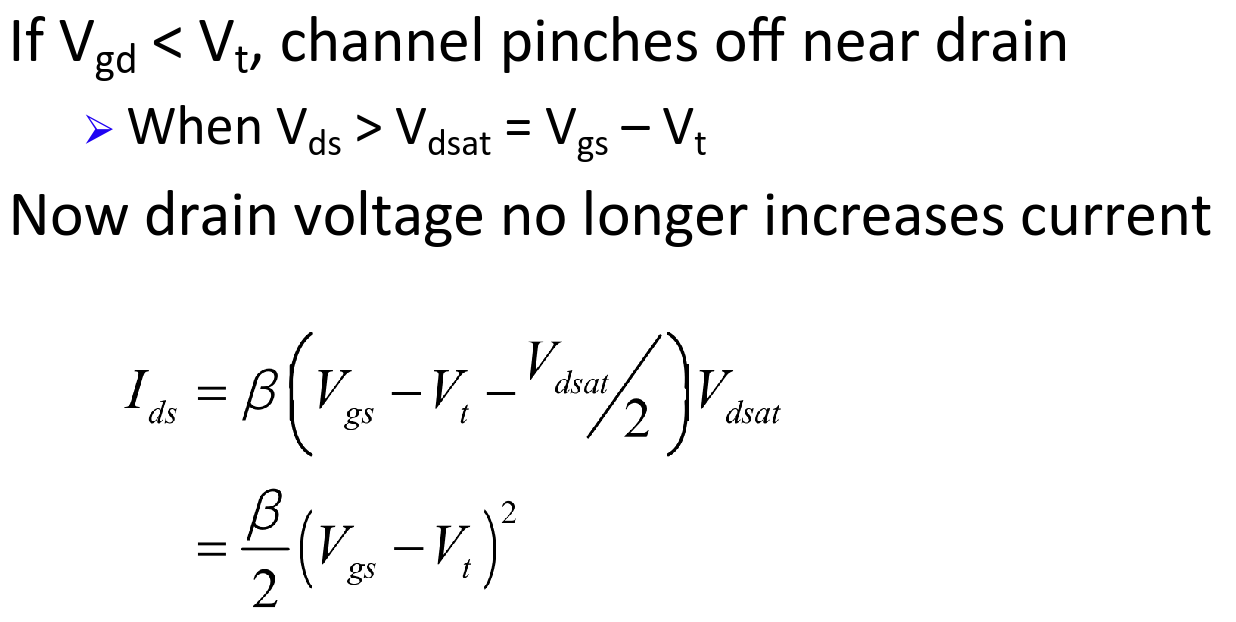

Saturation

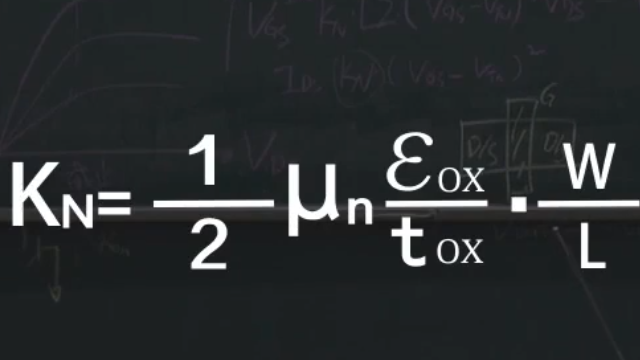

Channel Charge

Carrier velocity

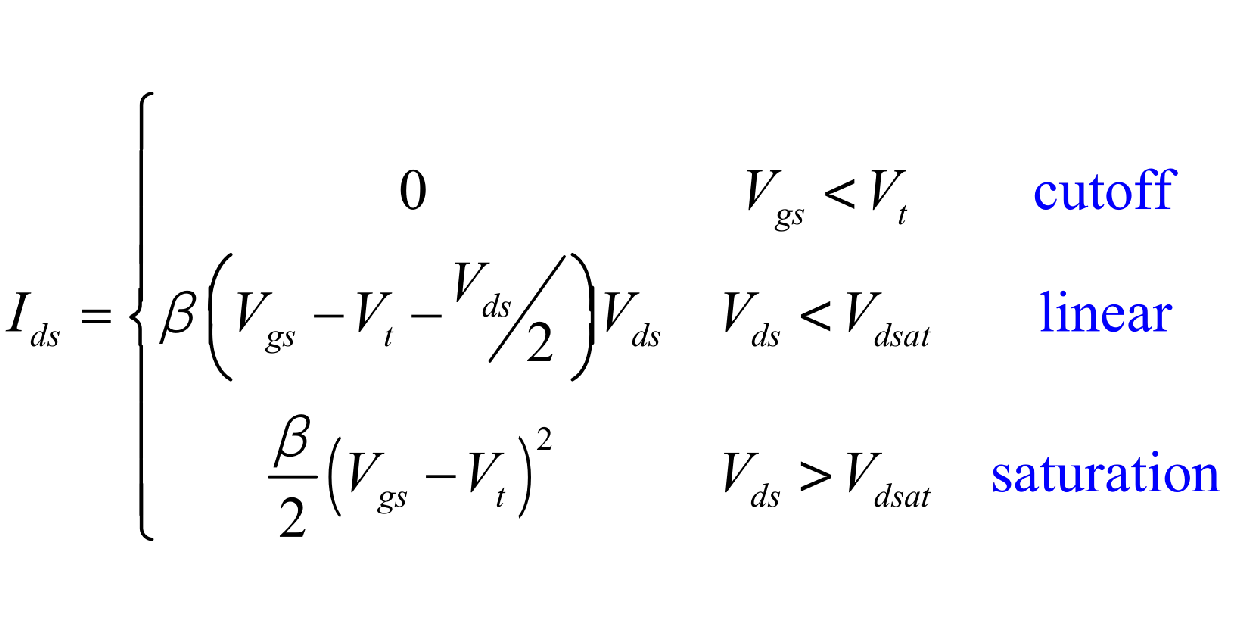

nMOS Linear I-V

nMOS Saturation I-V

Summary

nMOS Operation

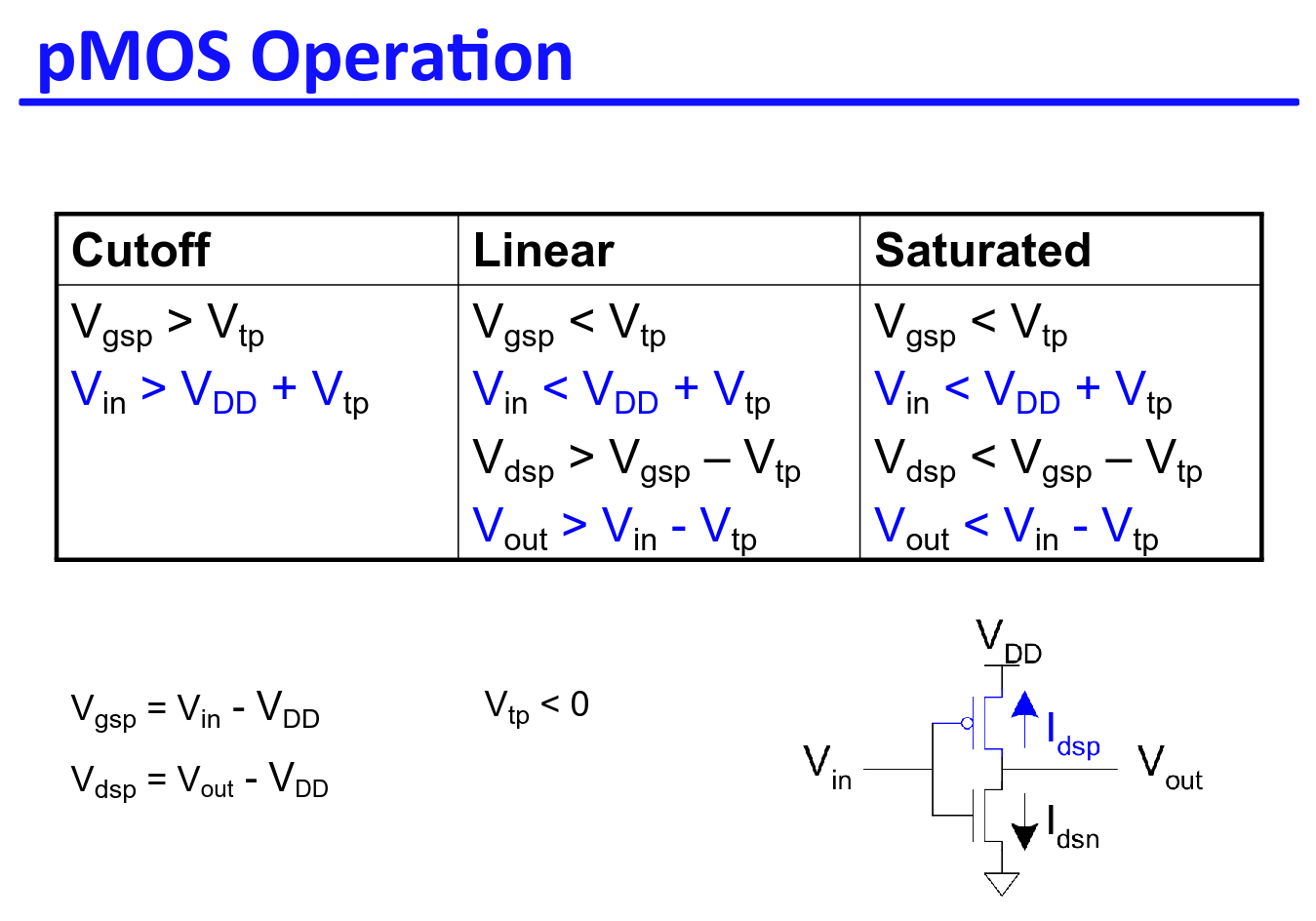

pMOS Operation

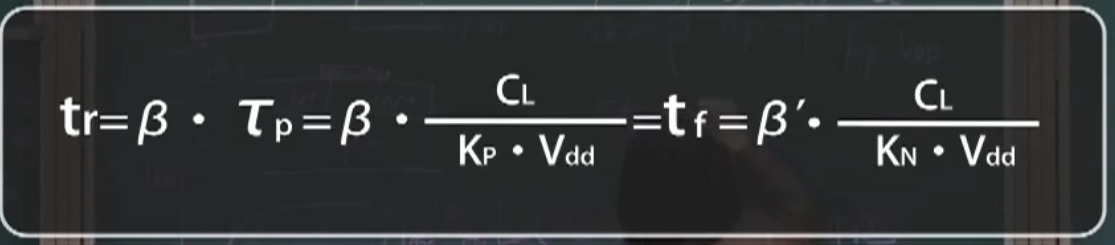

Inverter Step Response

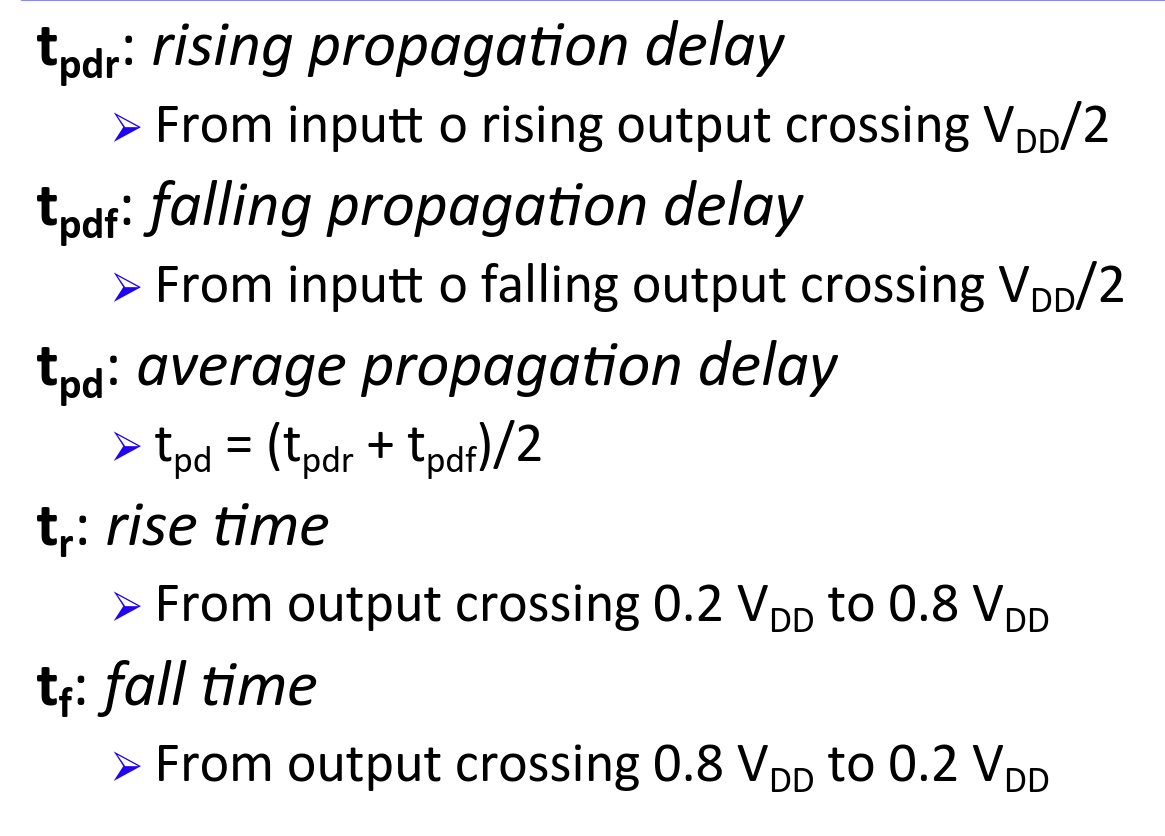

Delay Definitions

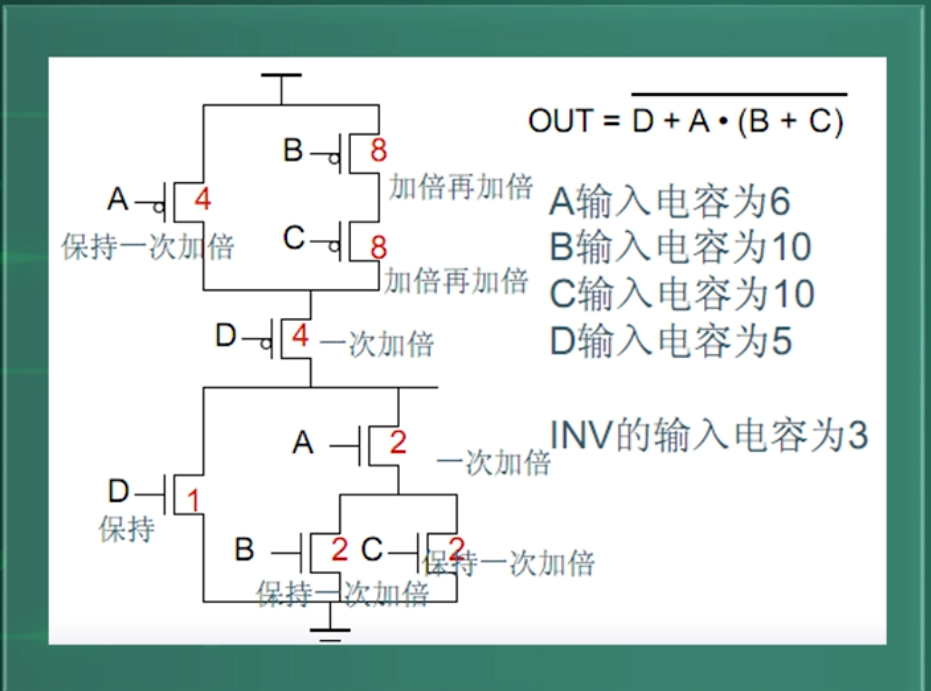

3-input NAND Caps

Elmore Delay

Estimate rising and falling propagation delays of a 2-input NAND driving h identical gates

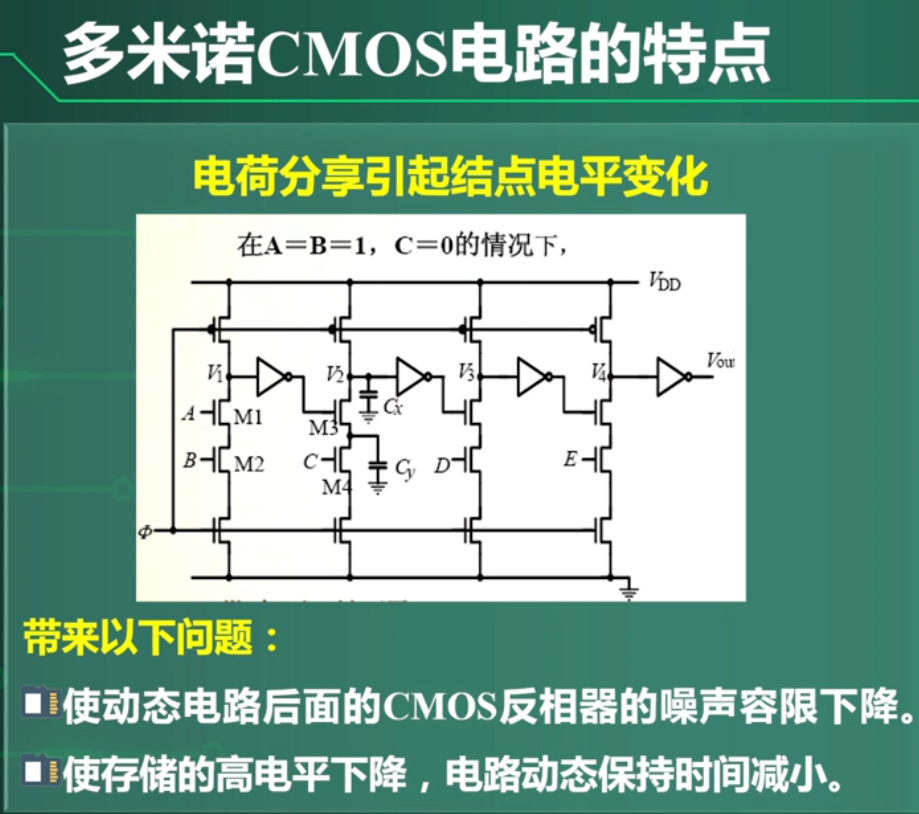

多米诺电路

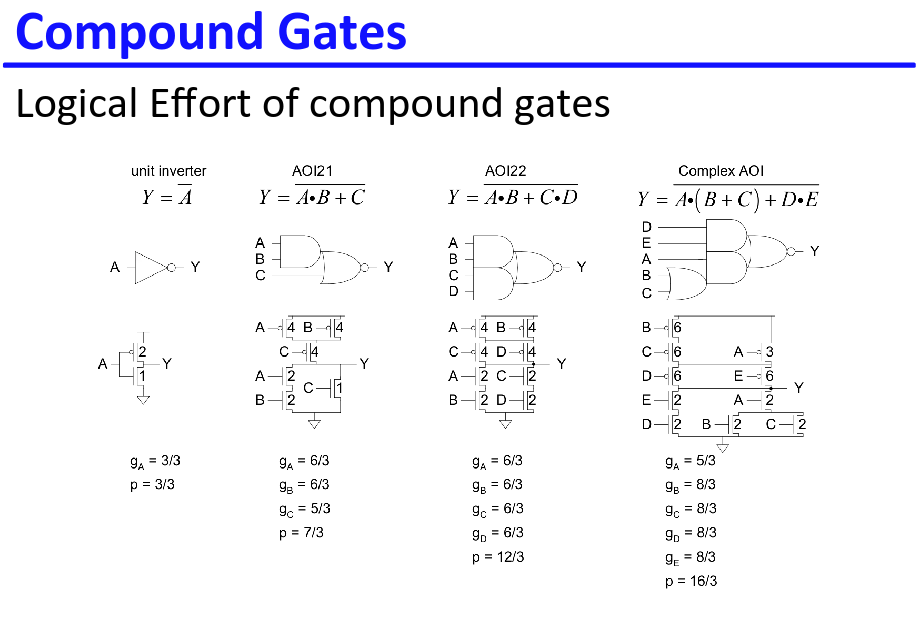

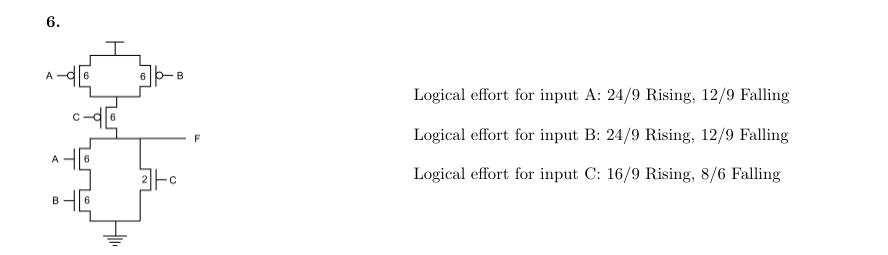

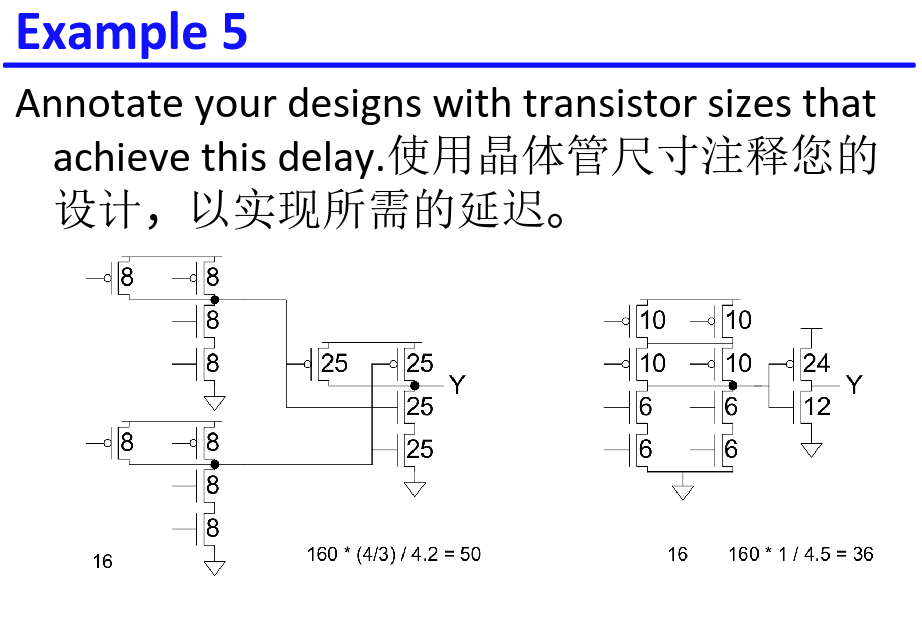

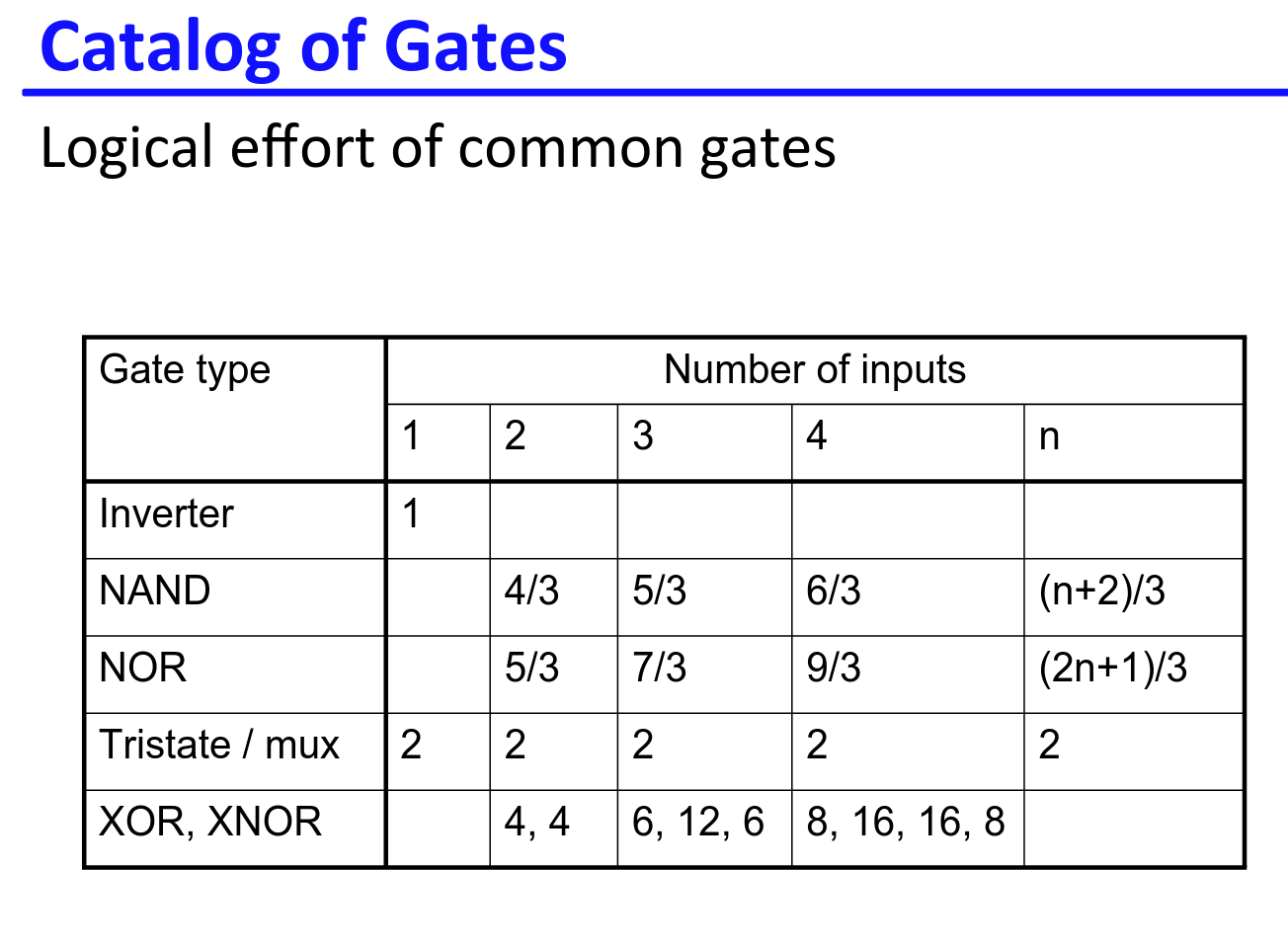

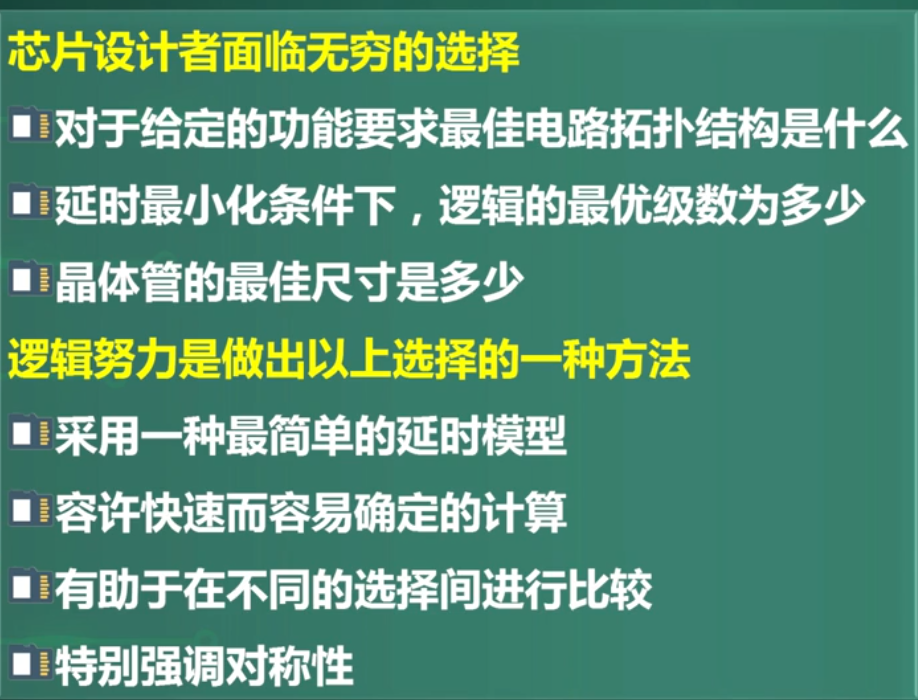

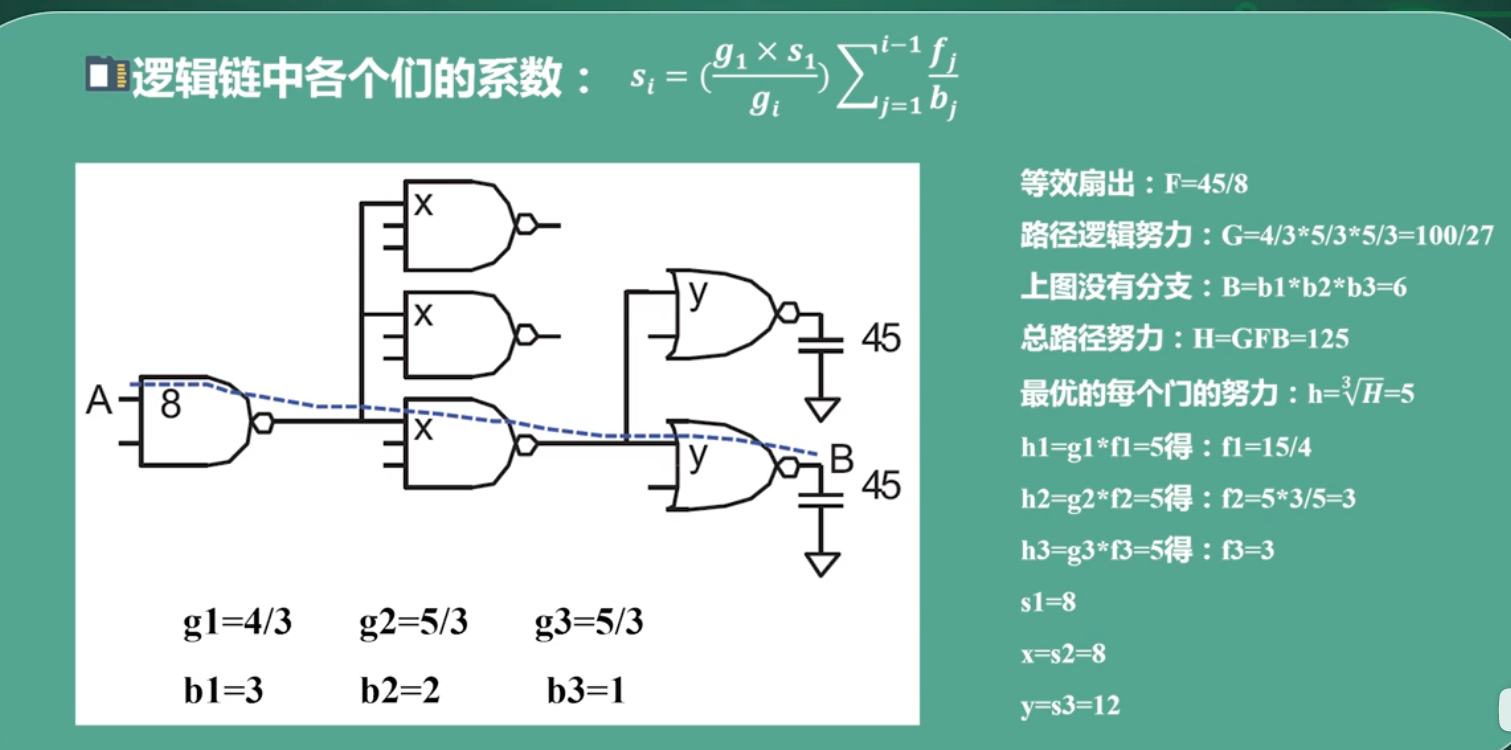

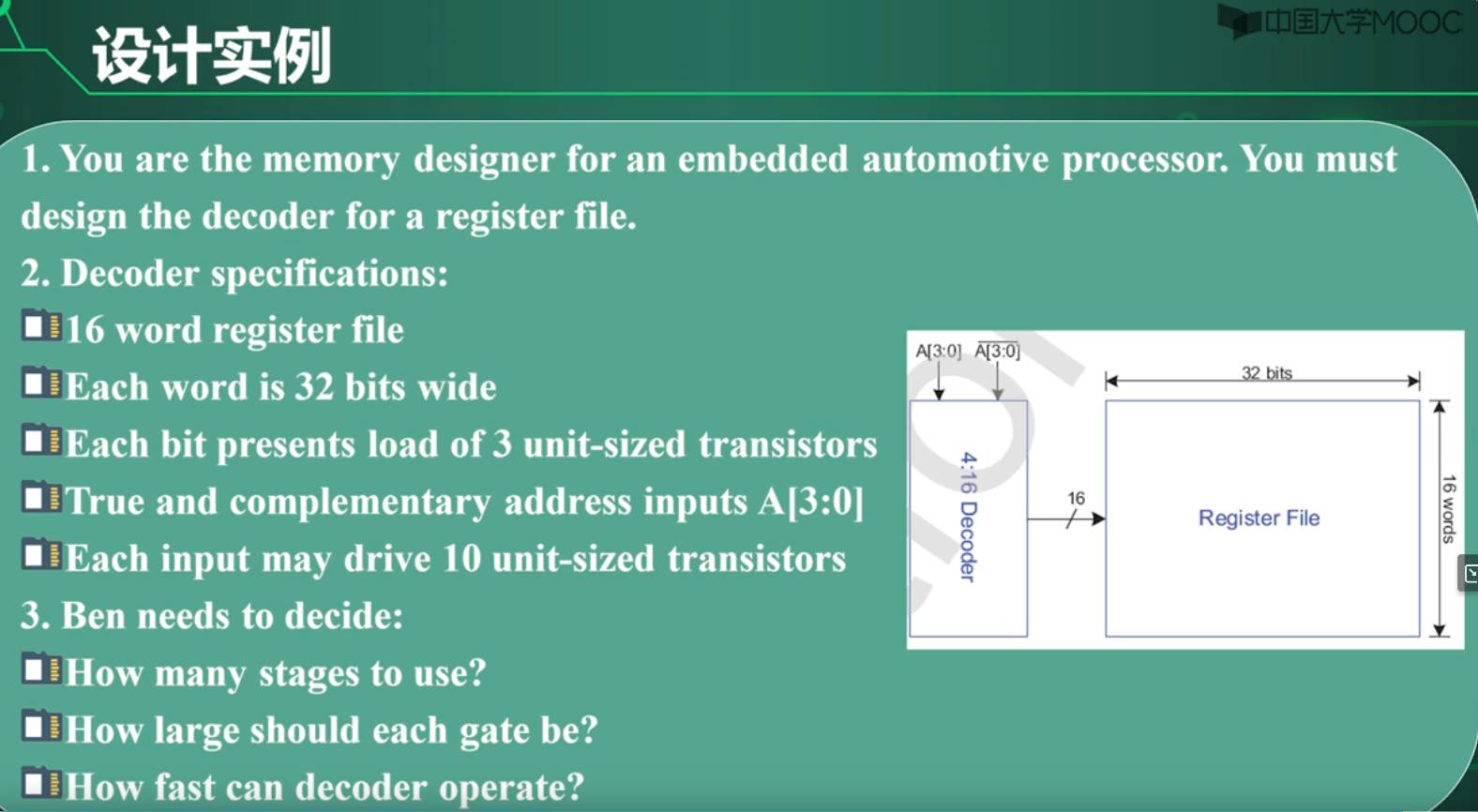

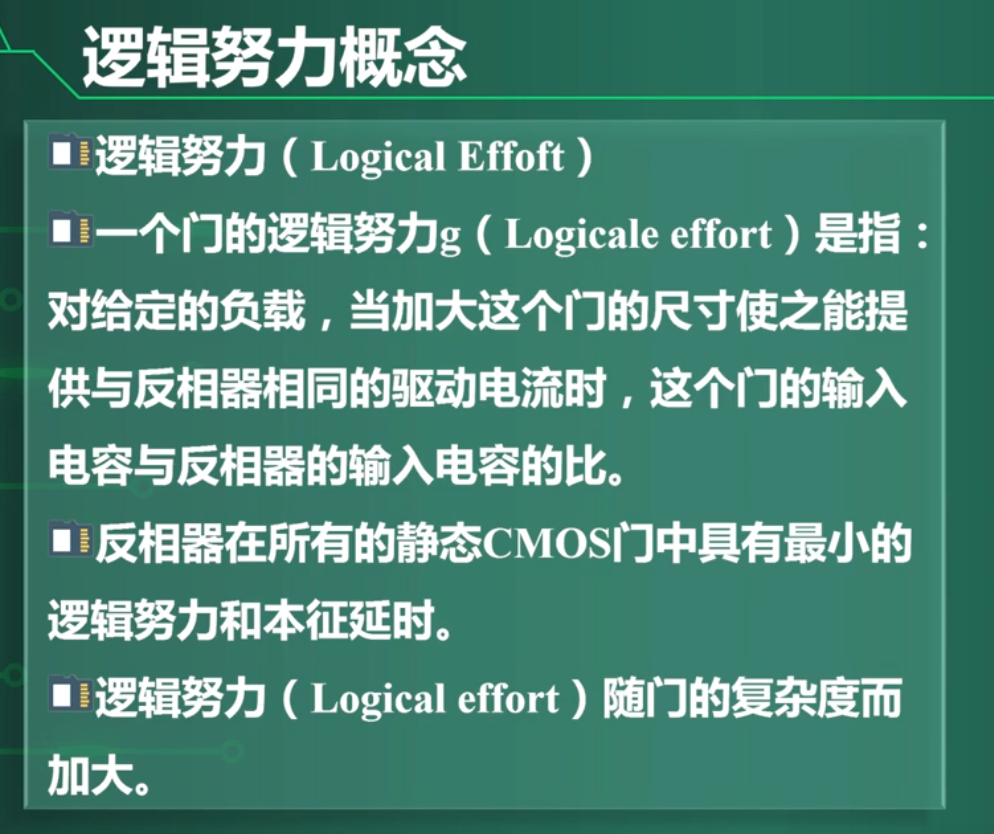

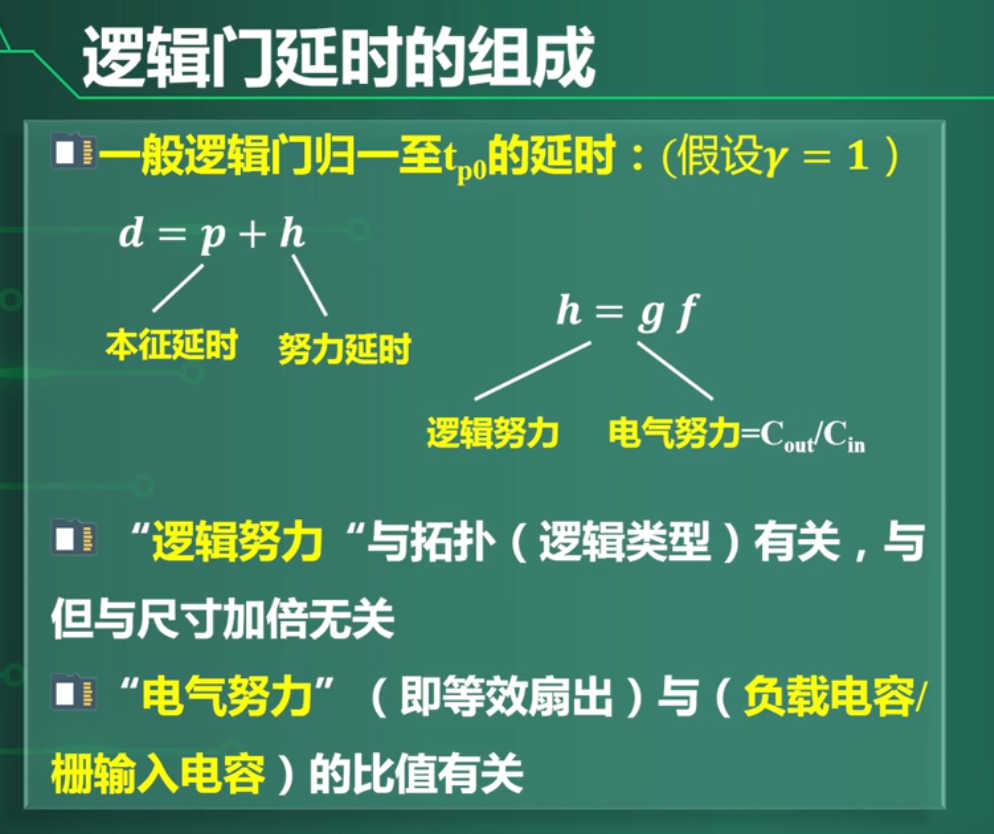

逻辑努力

Method of Logical Effort

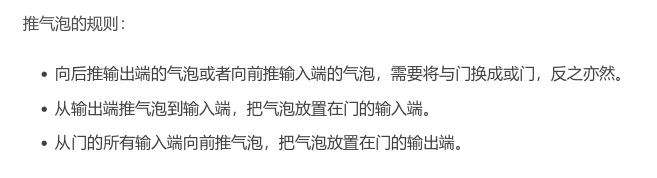

推气泡法

请简要说明动态逻辑电路输出单调性特点,对输入信号的单调特征有什么样

的要求,如果两个电路需要级联时应该如何设计两个电路的连接。(12 分)

答案:

由于动态电路具有单调降的输出电压,即在预充电之后上拉网络输出电压依靠输

出电容保持高电平输出,没有上拉充电回路(4 分);输出电压降低后不能再升

高,输入信号的电压需要单调升高的,保证动态逻辑门电路下拉网络放电仅有一

次,因此两个动态逻辑电路不能直接级联(4 分)。在一个动态逻辑电路后连接

一个静态逻辑门反相(如反相器),改变输入单调性,然后再与动态逻辑电路级

联构成多米诺电路的形式(4 分)。

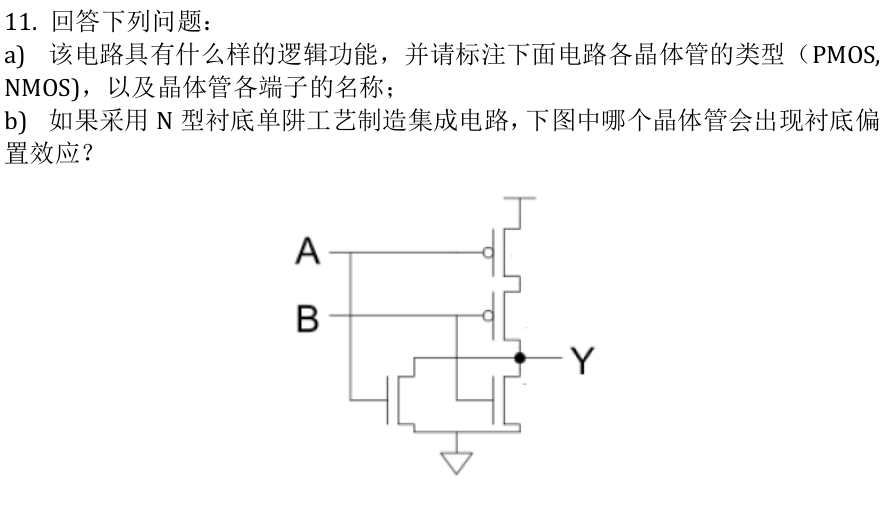

该电路具有或非逻辑功能(4 分),

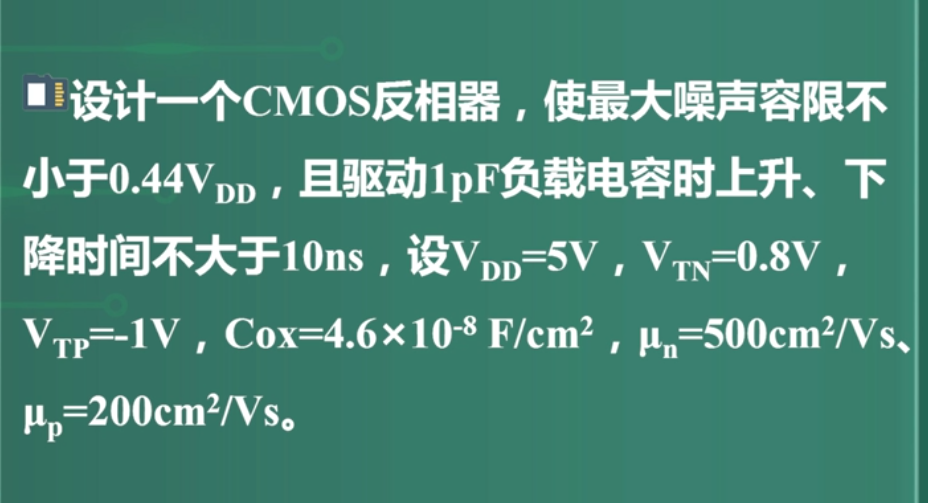

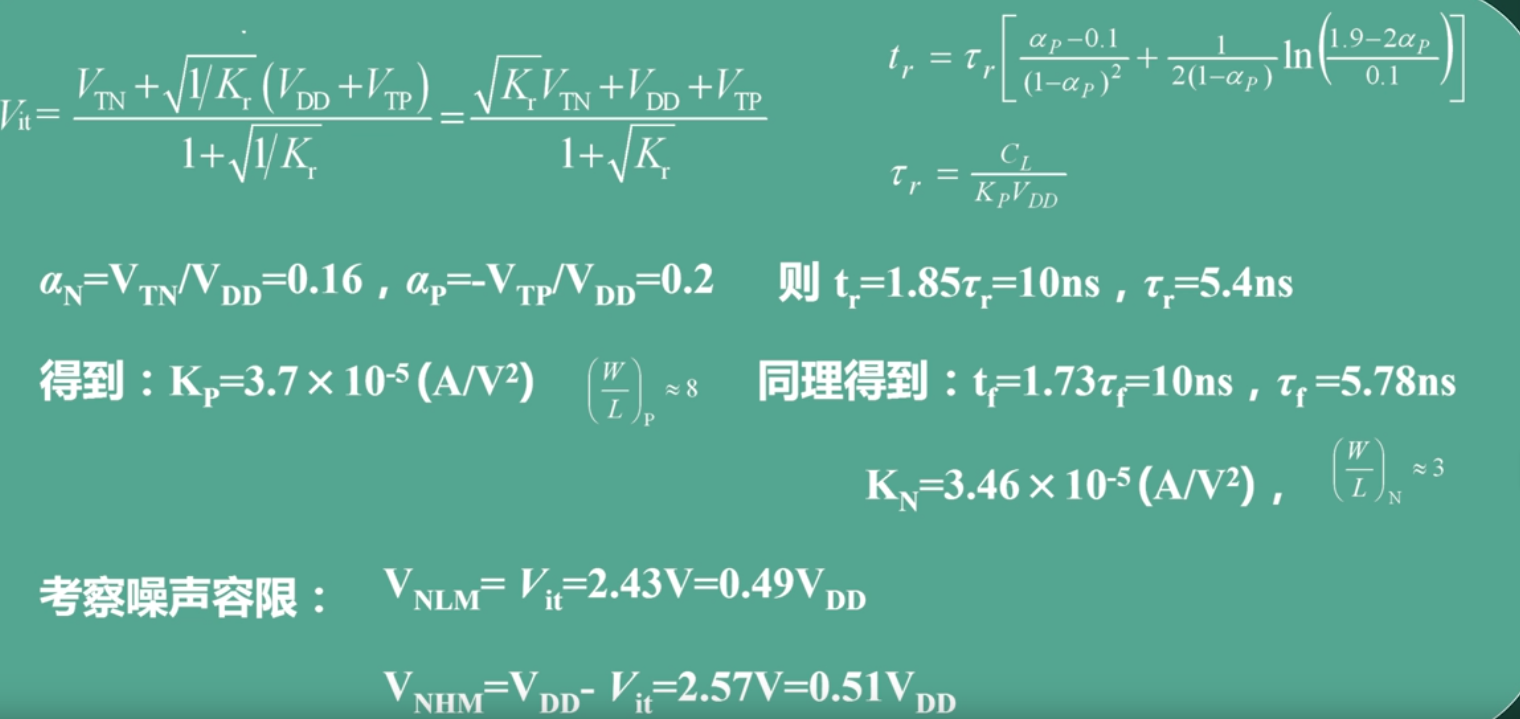

噪声容限

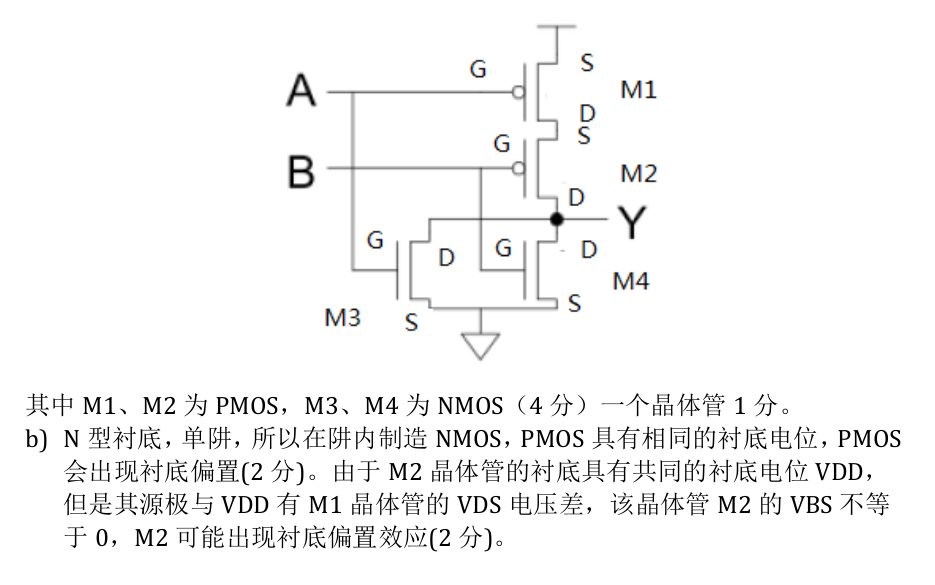

反相器的速度

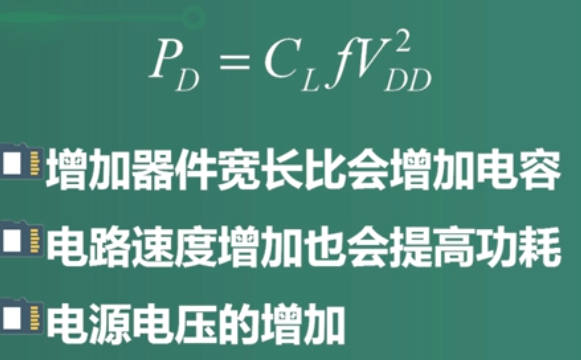

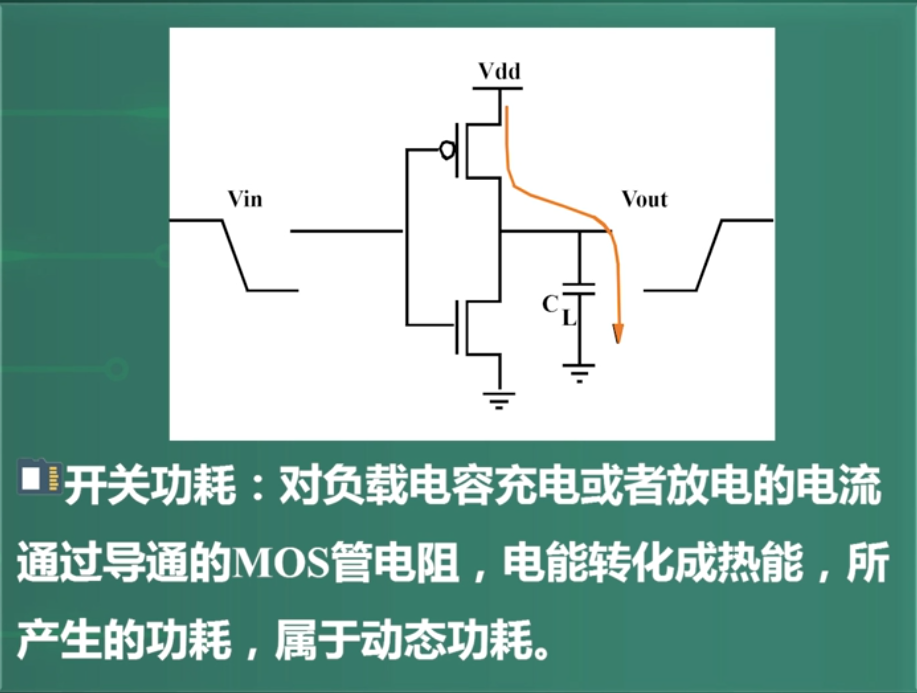

反相器功耗

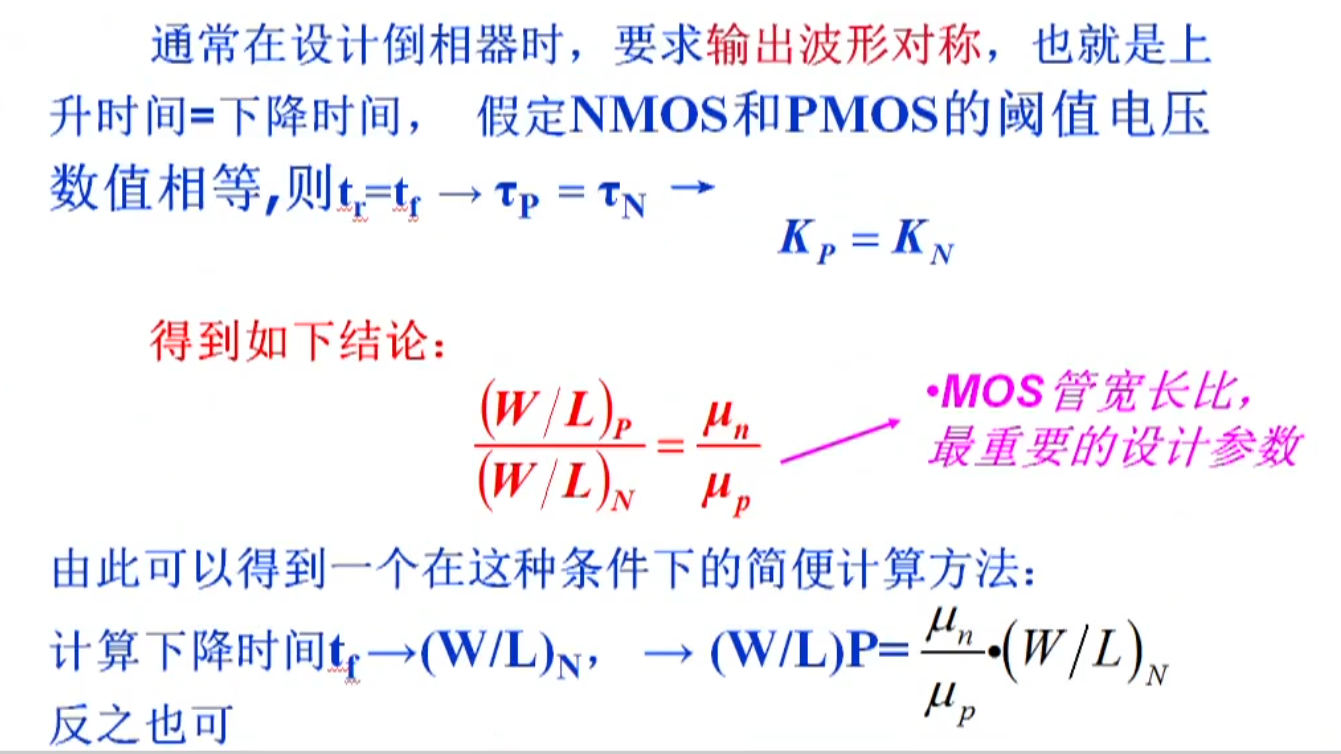

方向器设计:综合

例题

集成电路低功耗设计

集成电路为何需要低功耗?

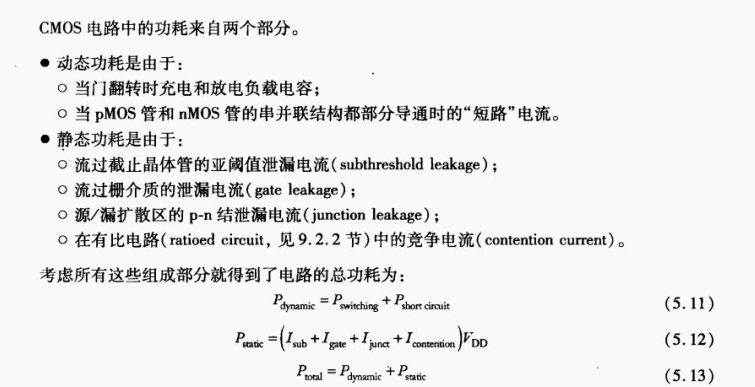

功耗来源

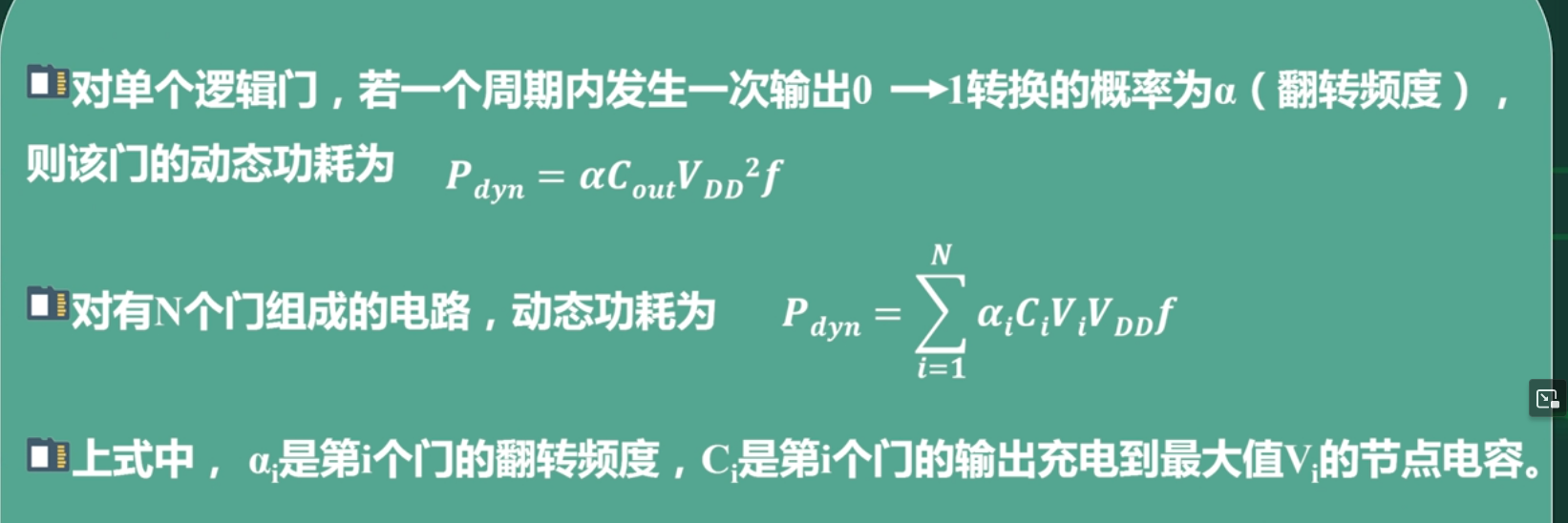

符合逻辑门动态功耗

减少漏电流-多阈值逻辑电路

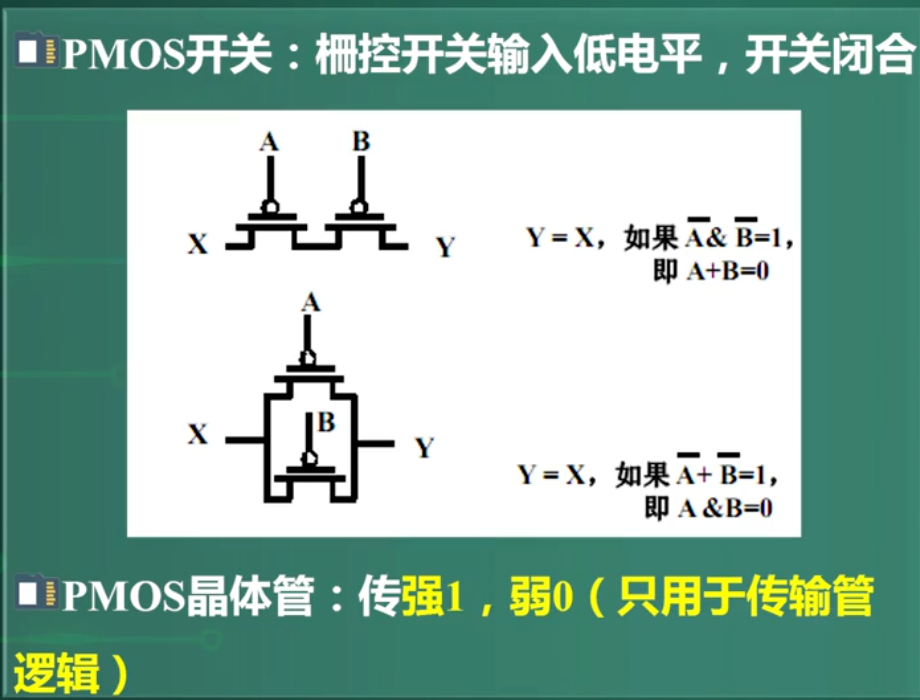

CMOS和PMOS晶体管串联和并联

与非门NAND

或非门

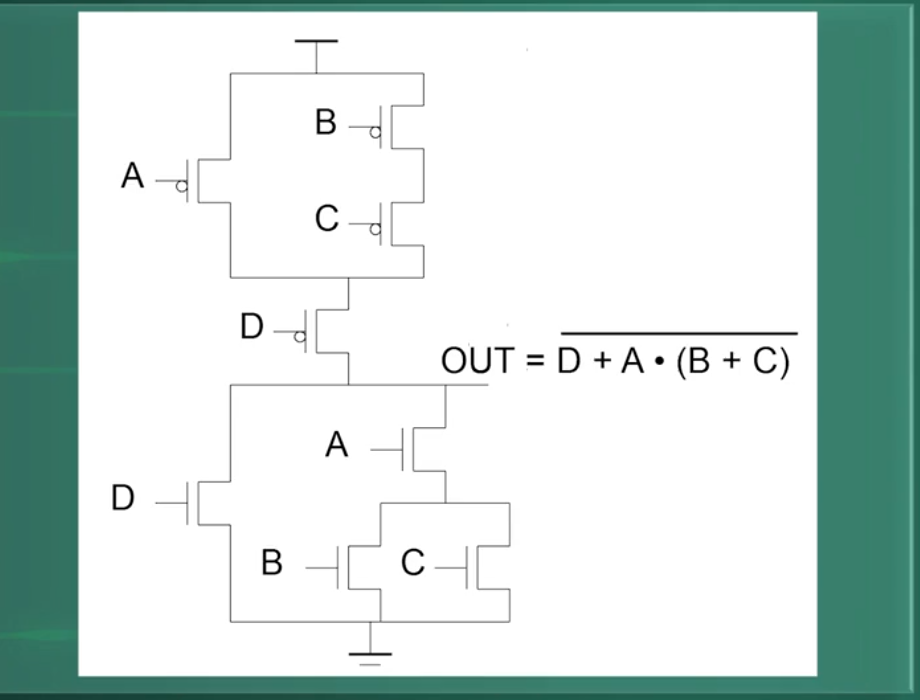

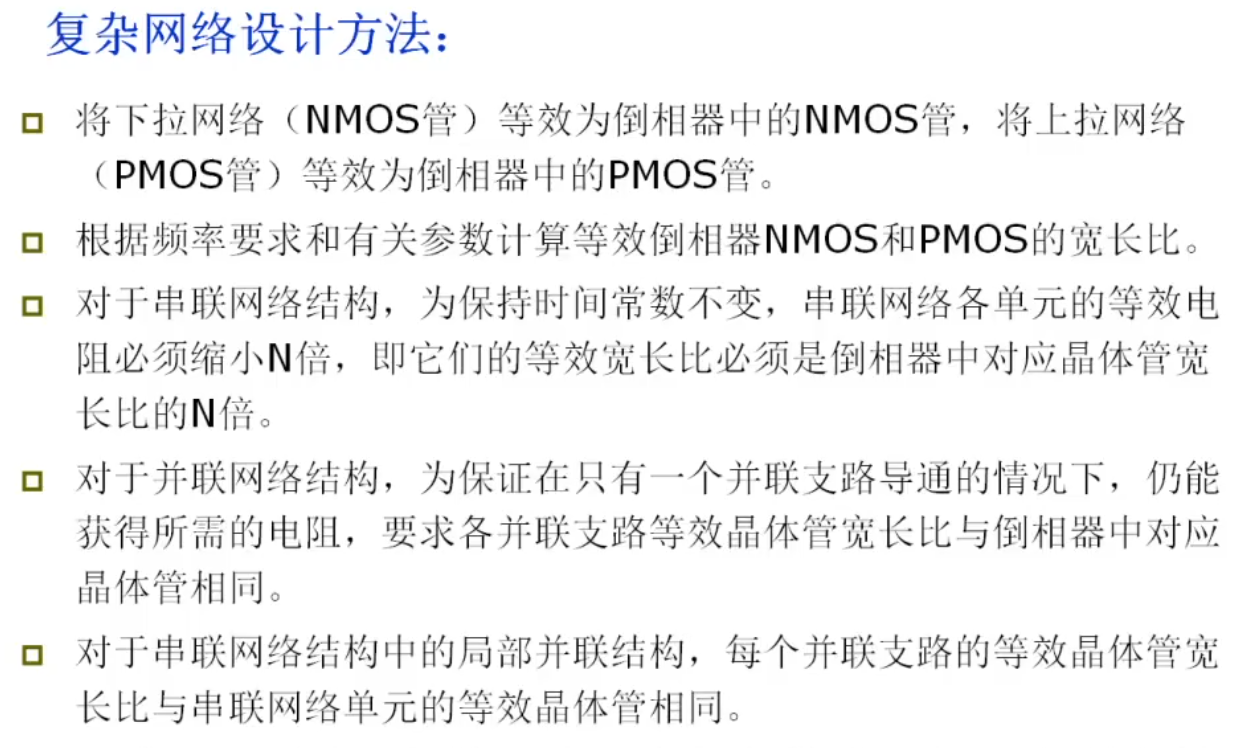

复杂CMOS门的晶体管尺寸规划

CMOS 功耗总结

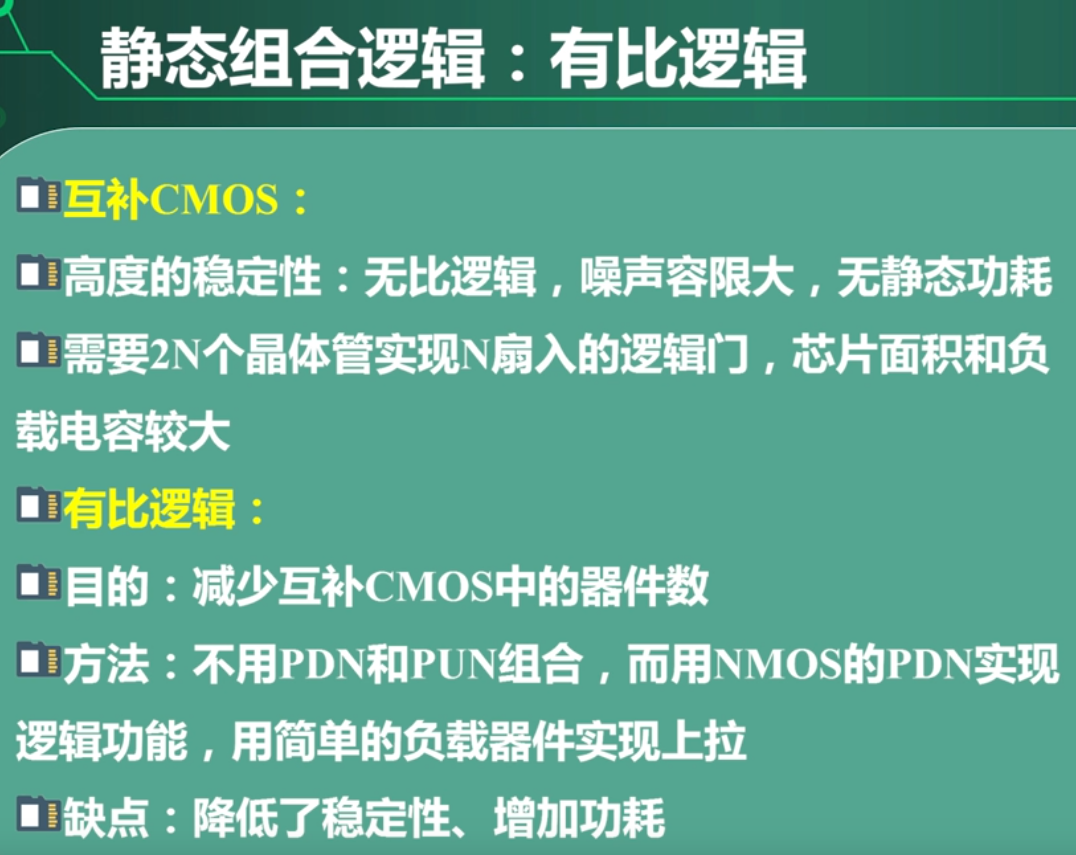

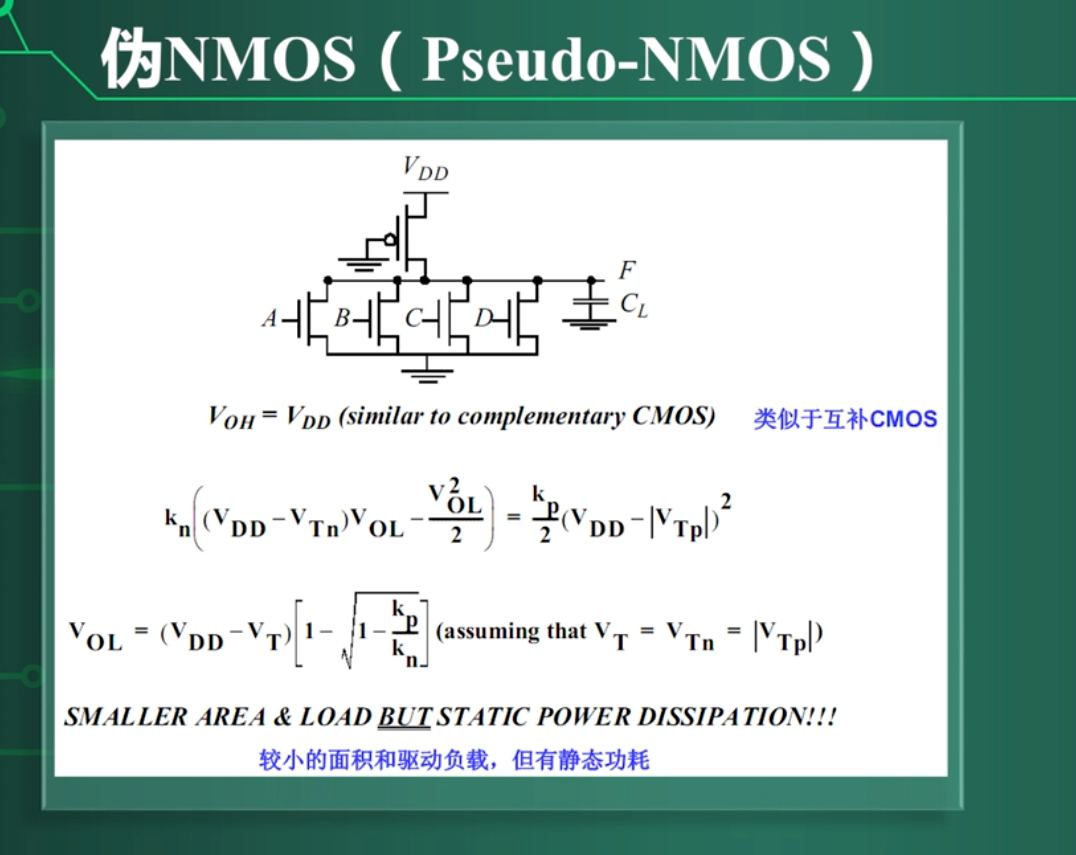

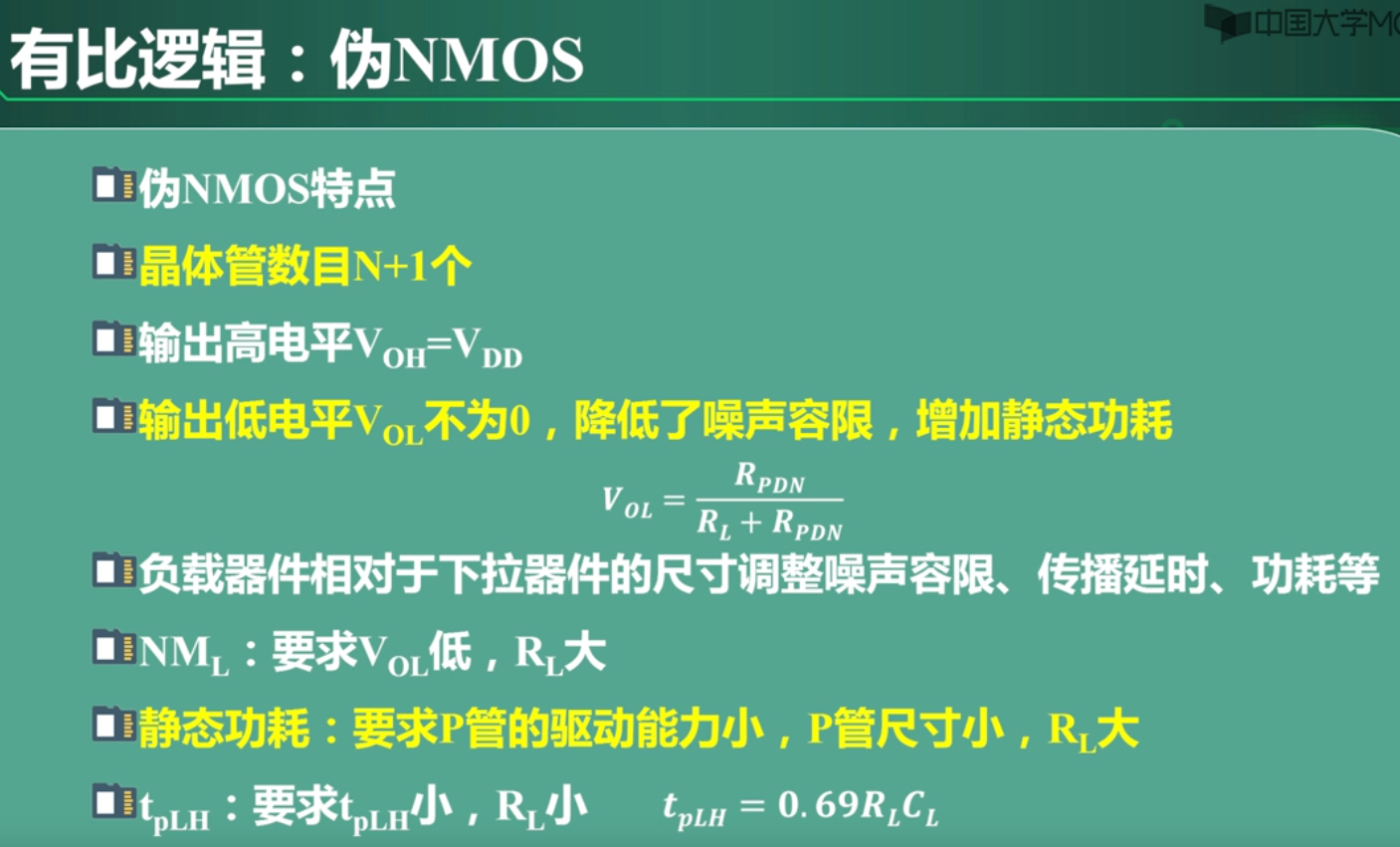

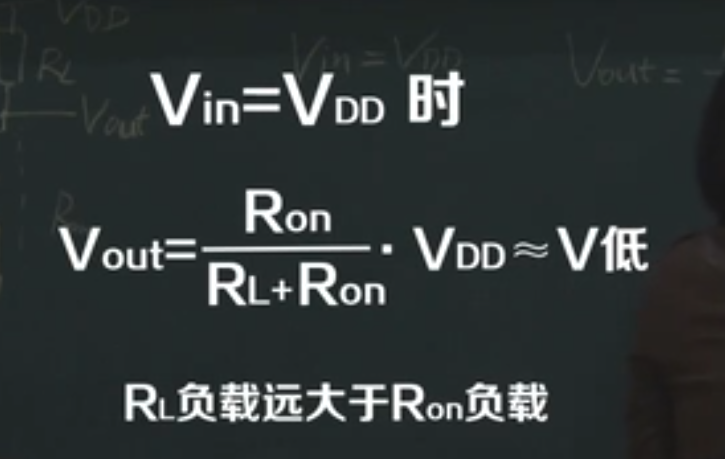

有比逻辑

Pseudo-NMOS

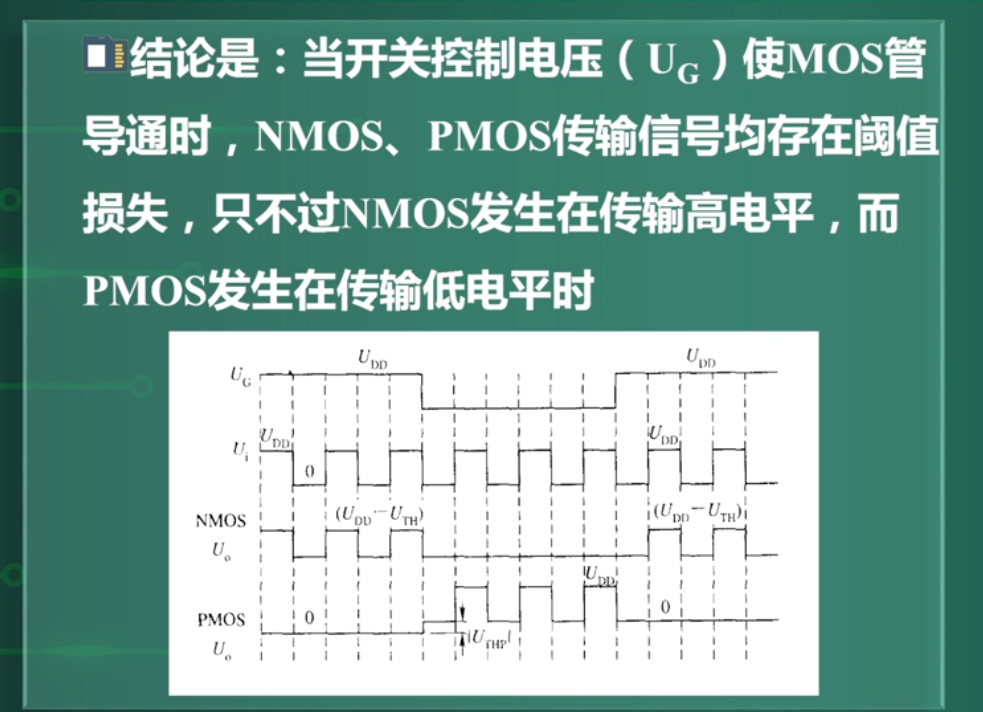

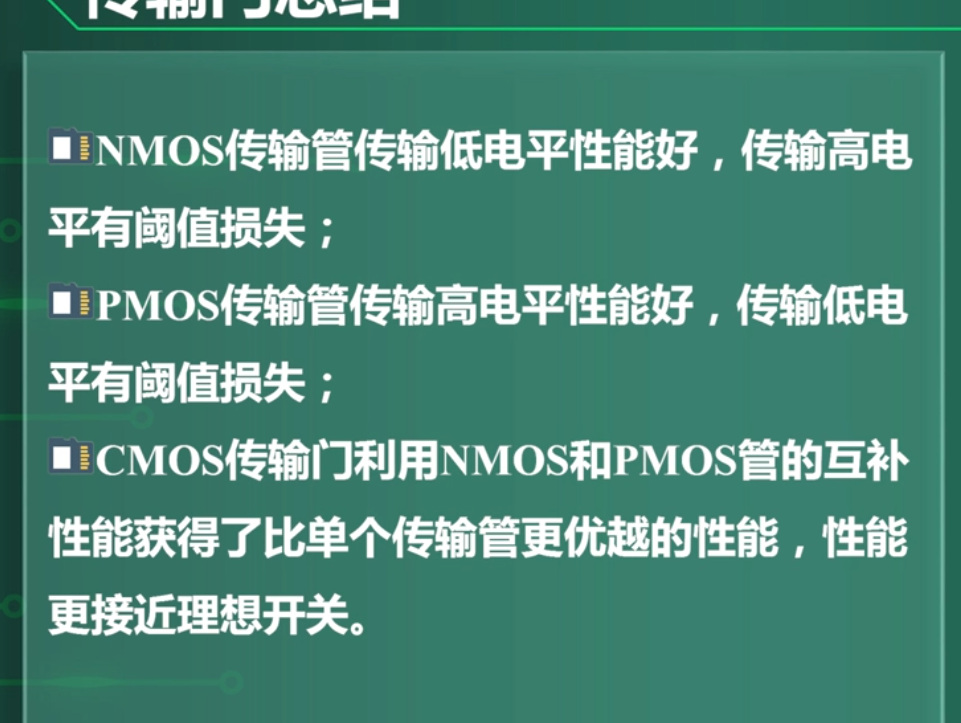

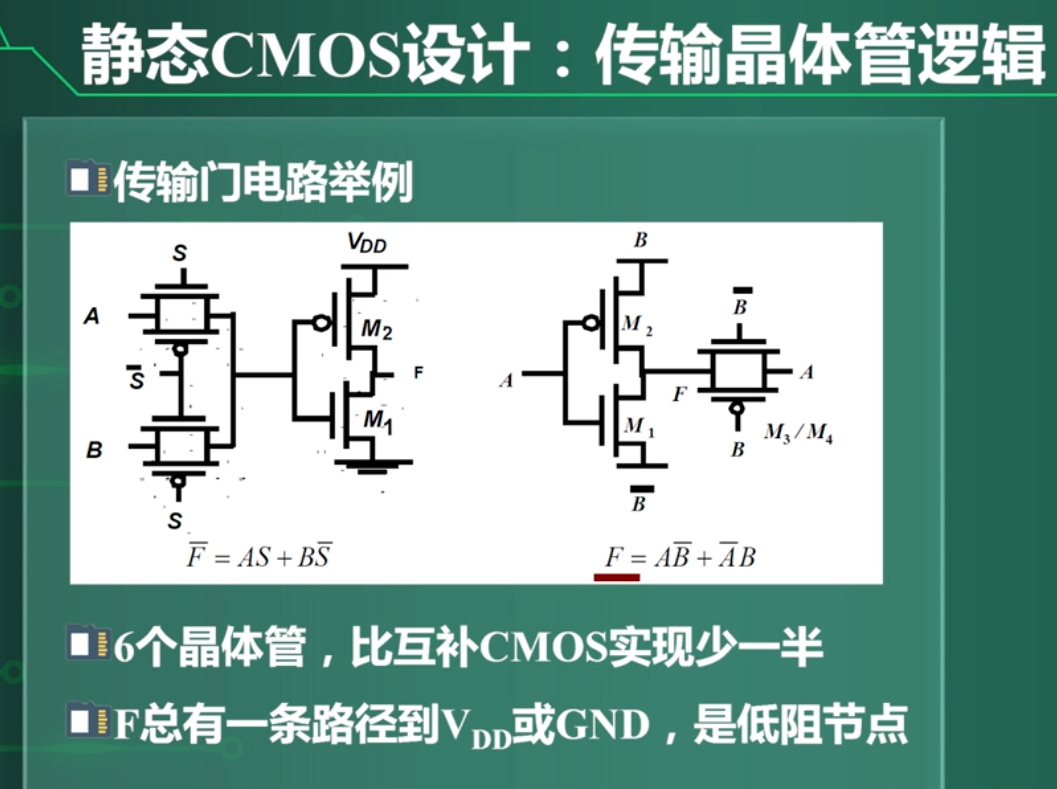

传输门

预充电求值逻辑

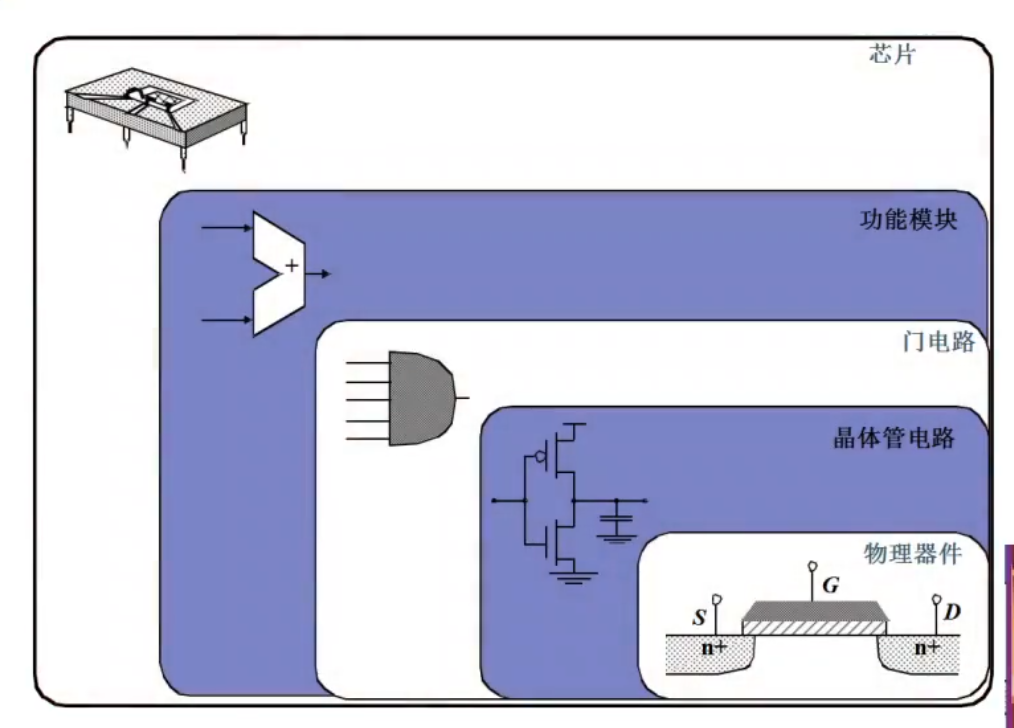

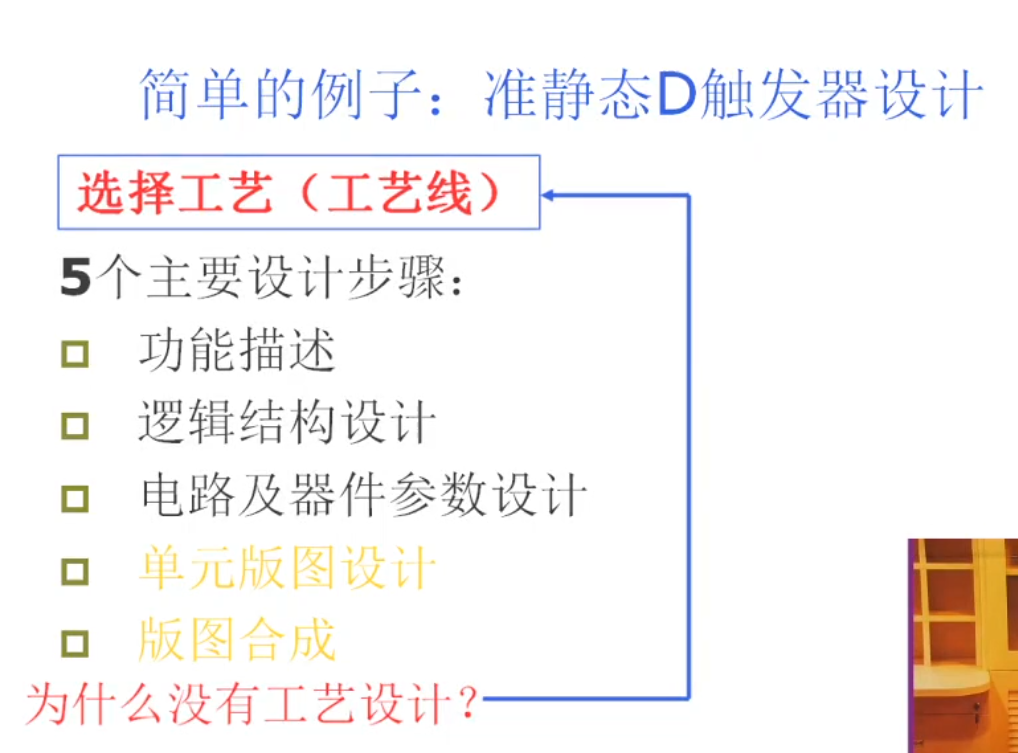

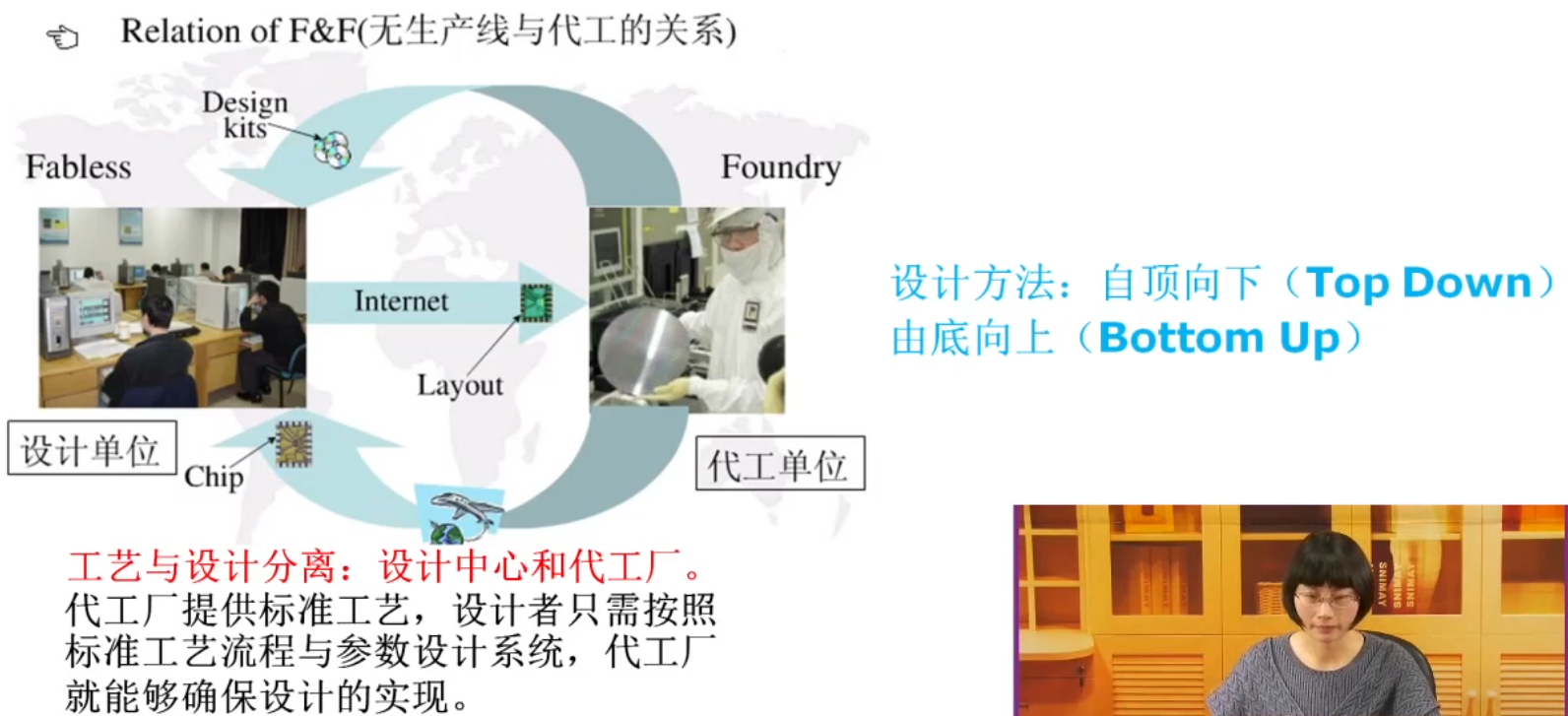

VLSI 设计方法

世界集成电路发展历程

版图设计理念

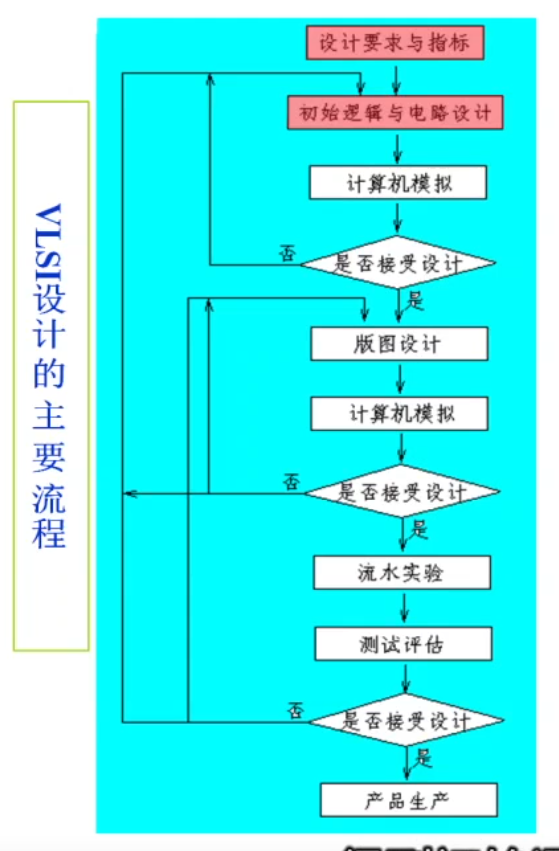

VLSI设计主要流程

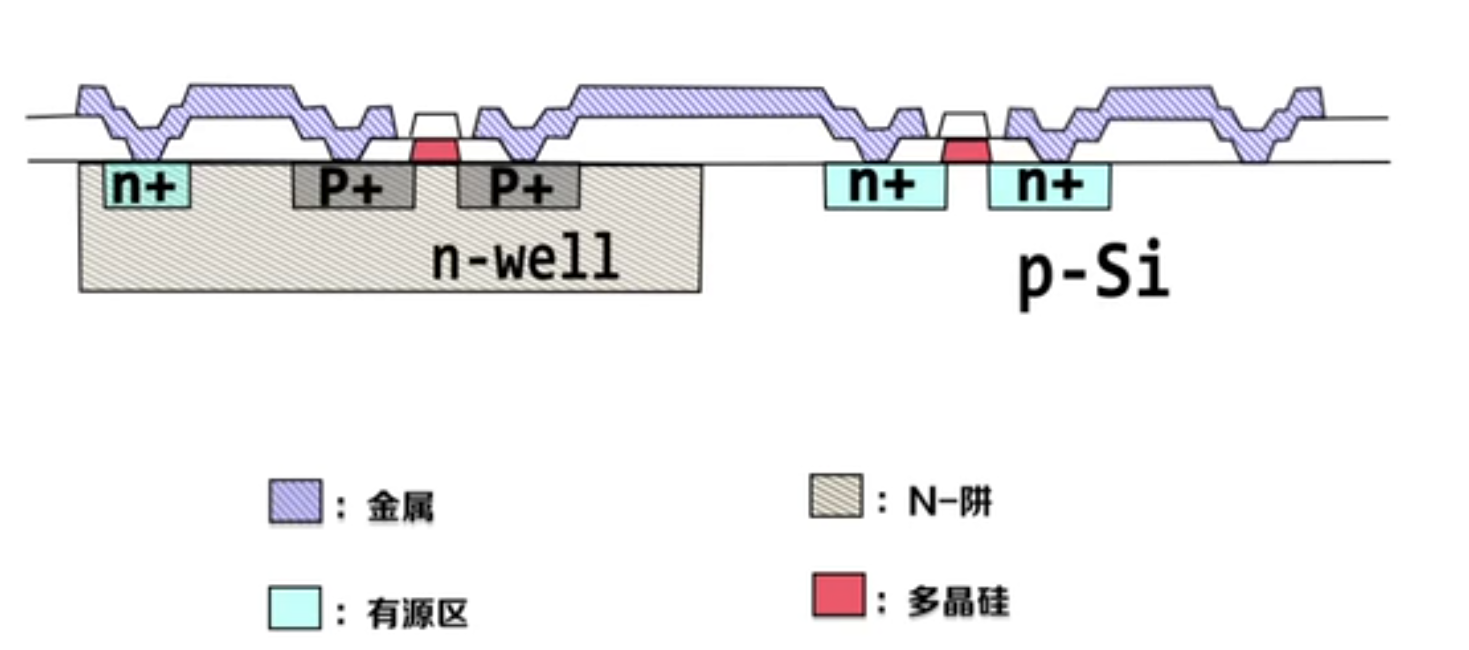

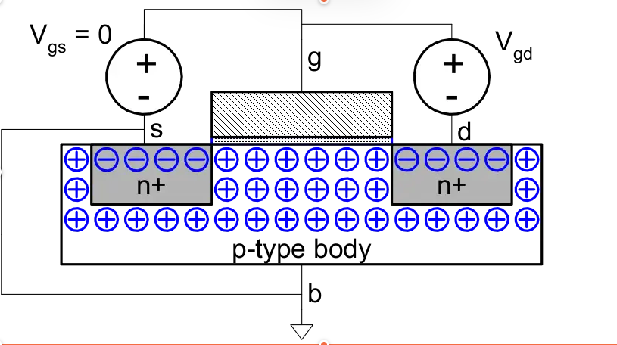

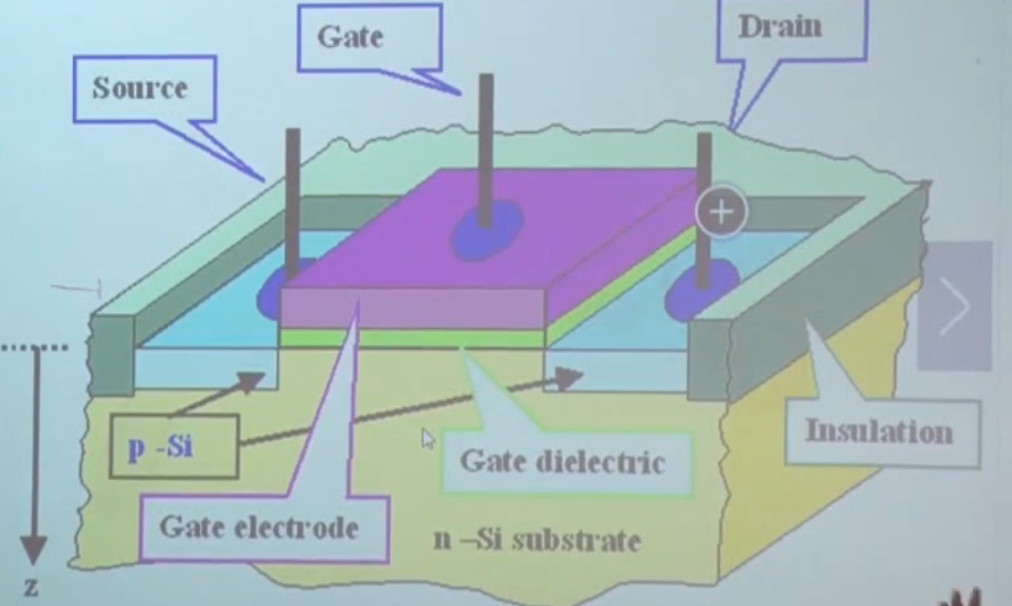

MOS晶体管结构

PN结单向导电——集成电路的基础

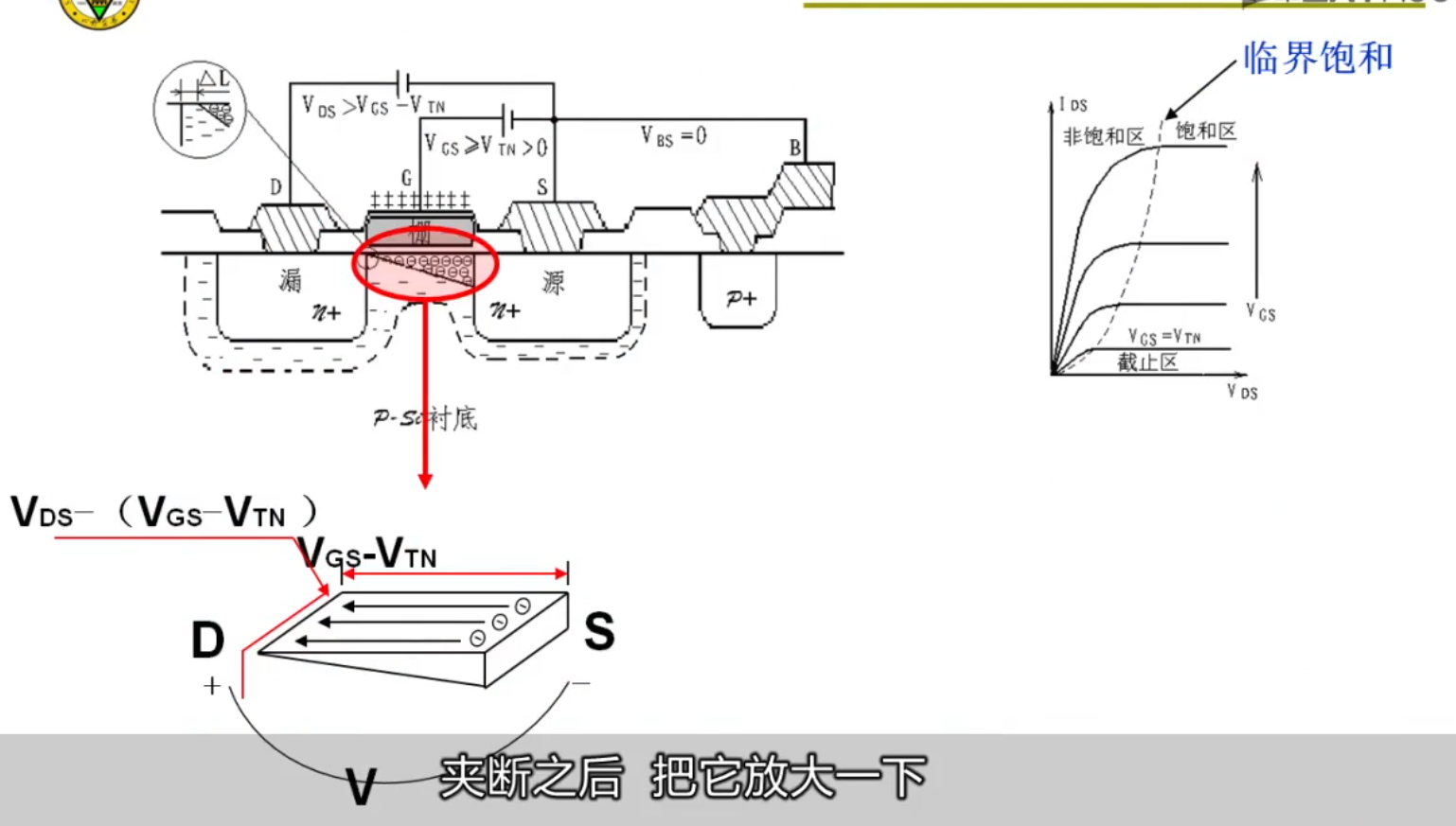

载流子是源到漏,电流是漏到源

mos 晶体管工作原理

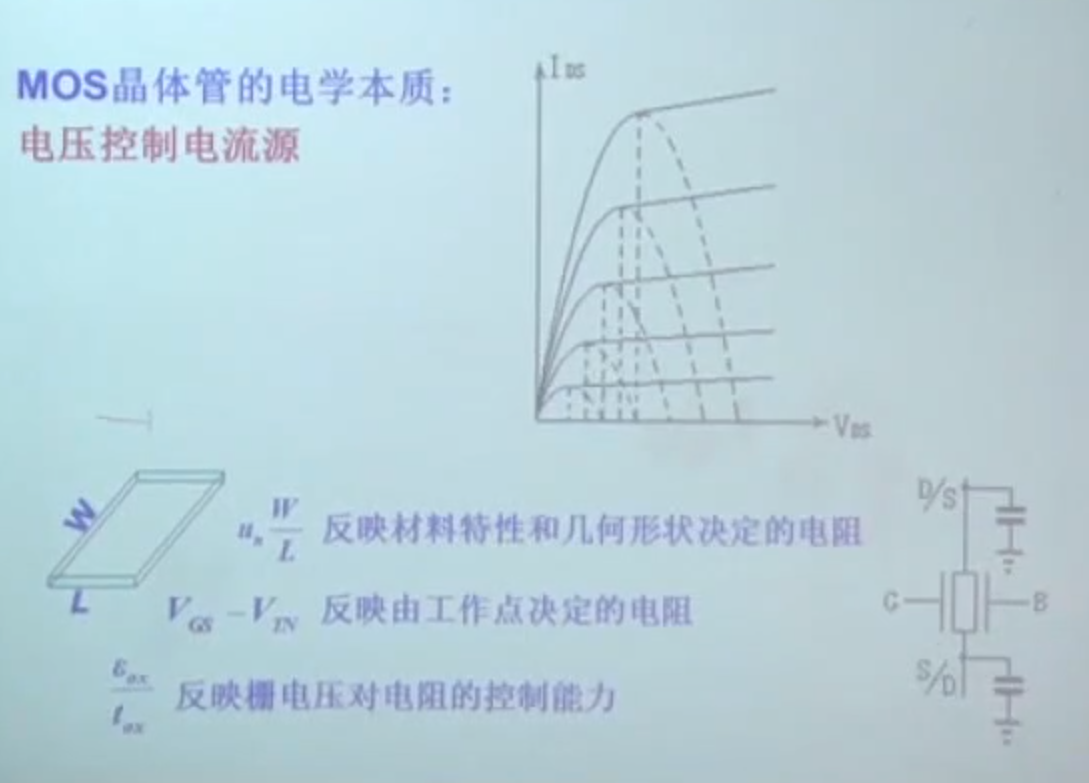

V D S ——源漏电压 V_{DS} —— 源漏电压 VDS?——源漏电压

V G S ——栅源电压 V_{GS}——栅源电压 VGS?——栅源电压

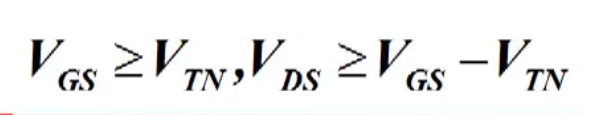

饱和区工作条件

MOS管的转移特性

- 是指 I D S I_{DS} IDS? 随着 V G s V_{Gs} VGs? 的变化关系

MOS晶体管的电学本质

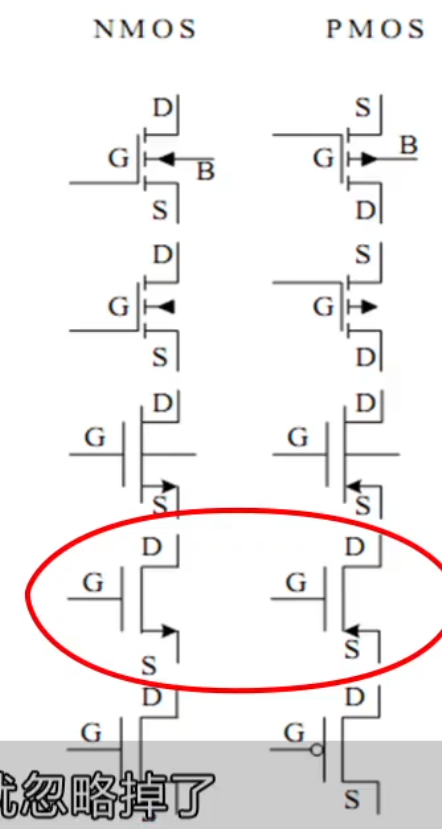

PMOS 晶体管

两类MOS晶体管

MOS管符号

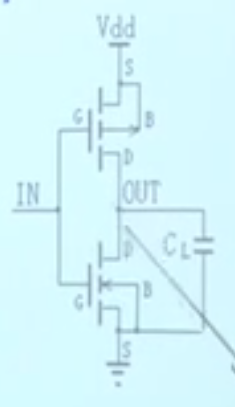

CMOS结构及其优势

CMOS反相器设计

PMOS 高电平是源,低电平是漏;

所以两个漏极相连

静态分析

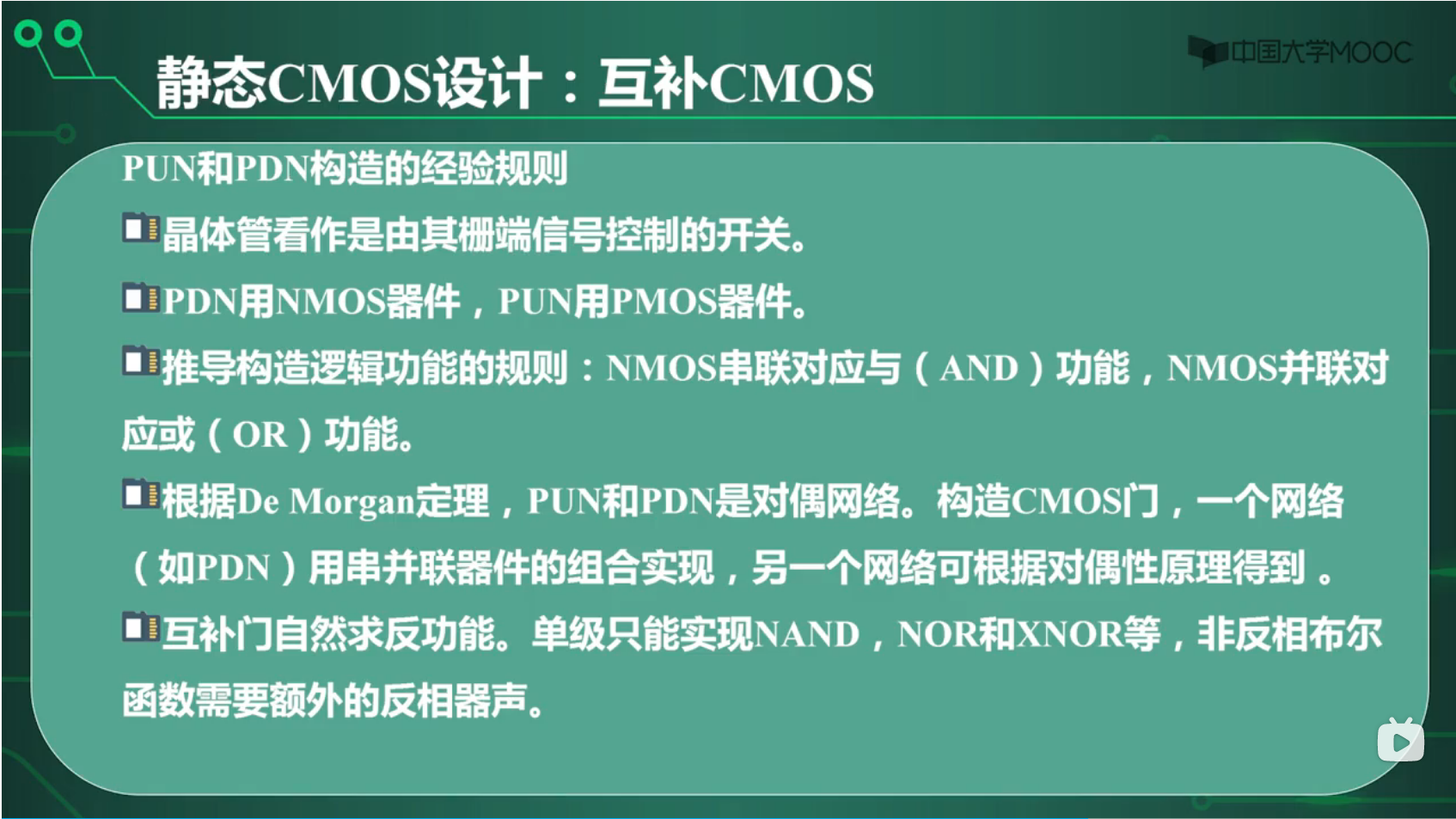

CMOS逻辑门构造

与非门设计方法

nmos 为1,pmos为2。

异或门和同或门

传输门

源和漏之间可以传

源和漏是不分的,只有人分析的时候才分

三态门

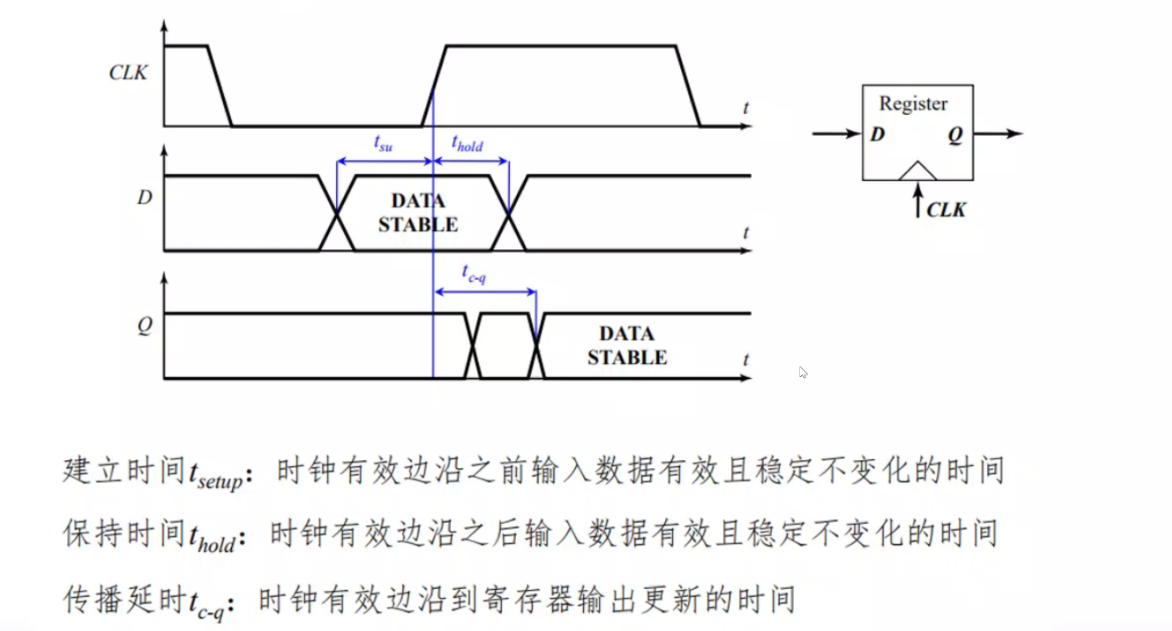

时序逻辑

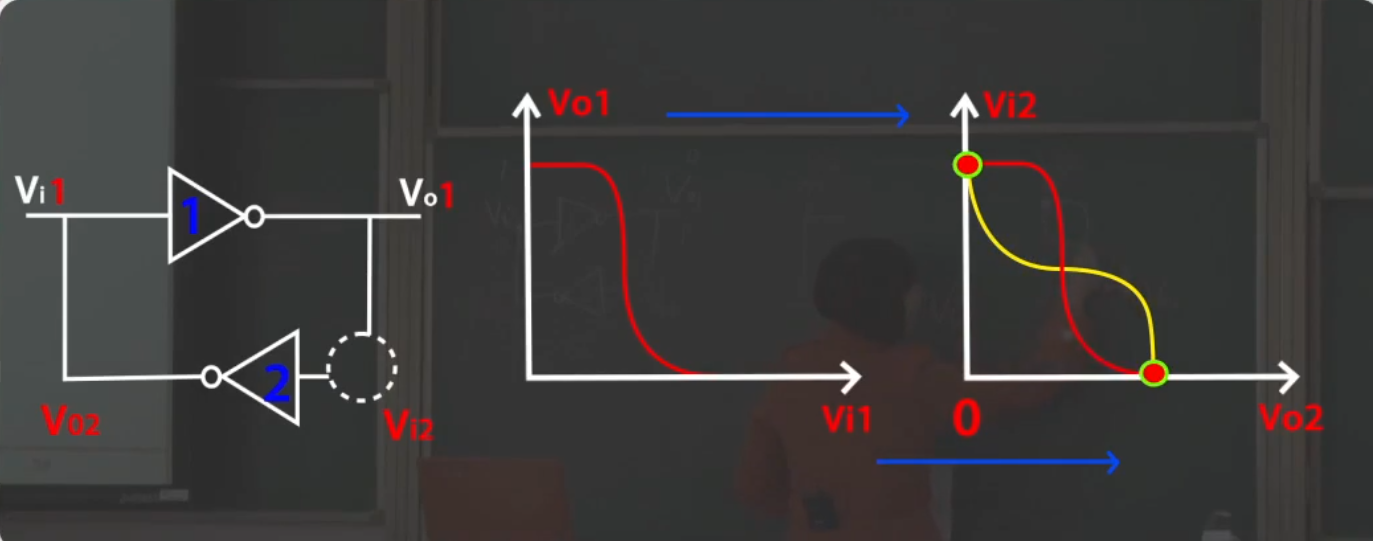

如何锁存信号-正反馈

D 触发器

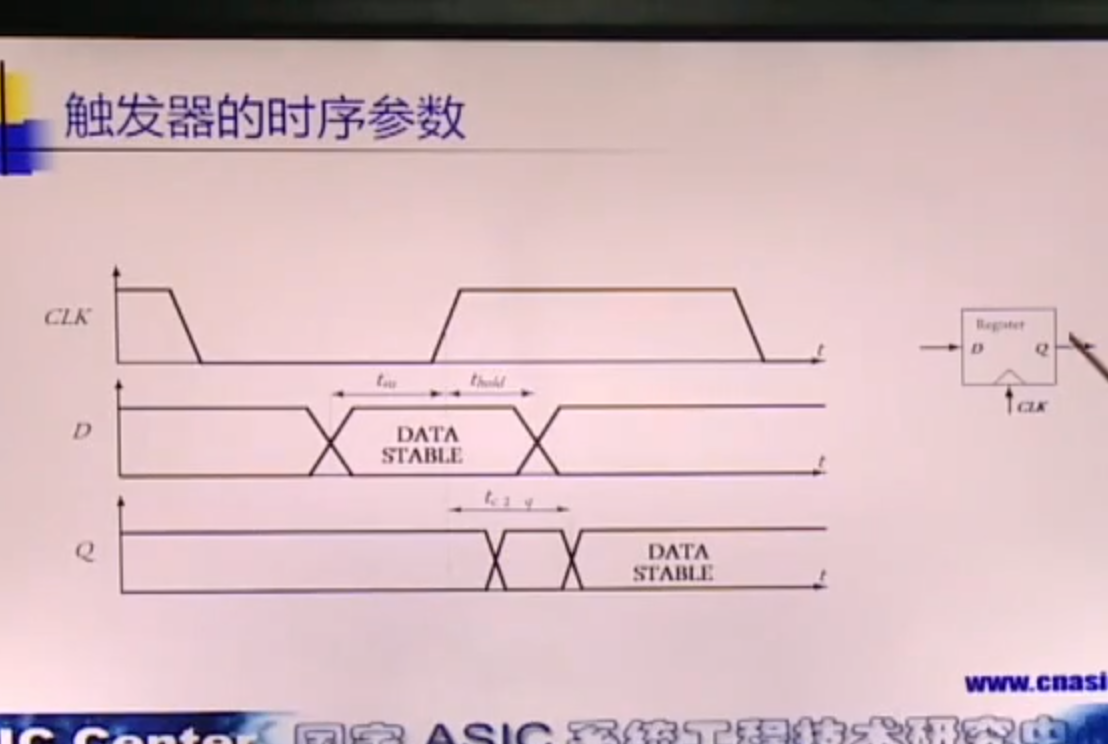

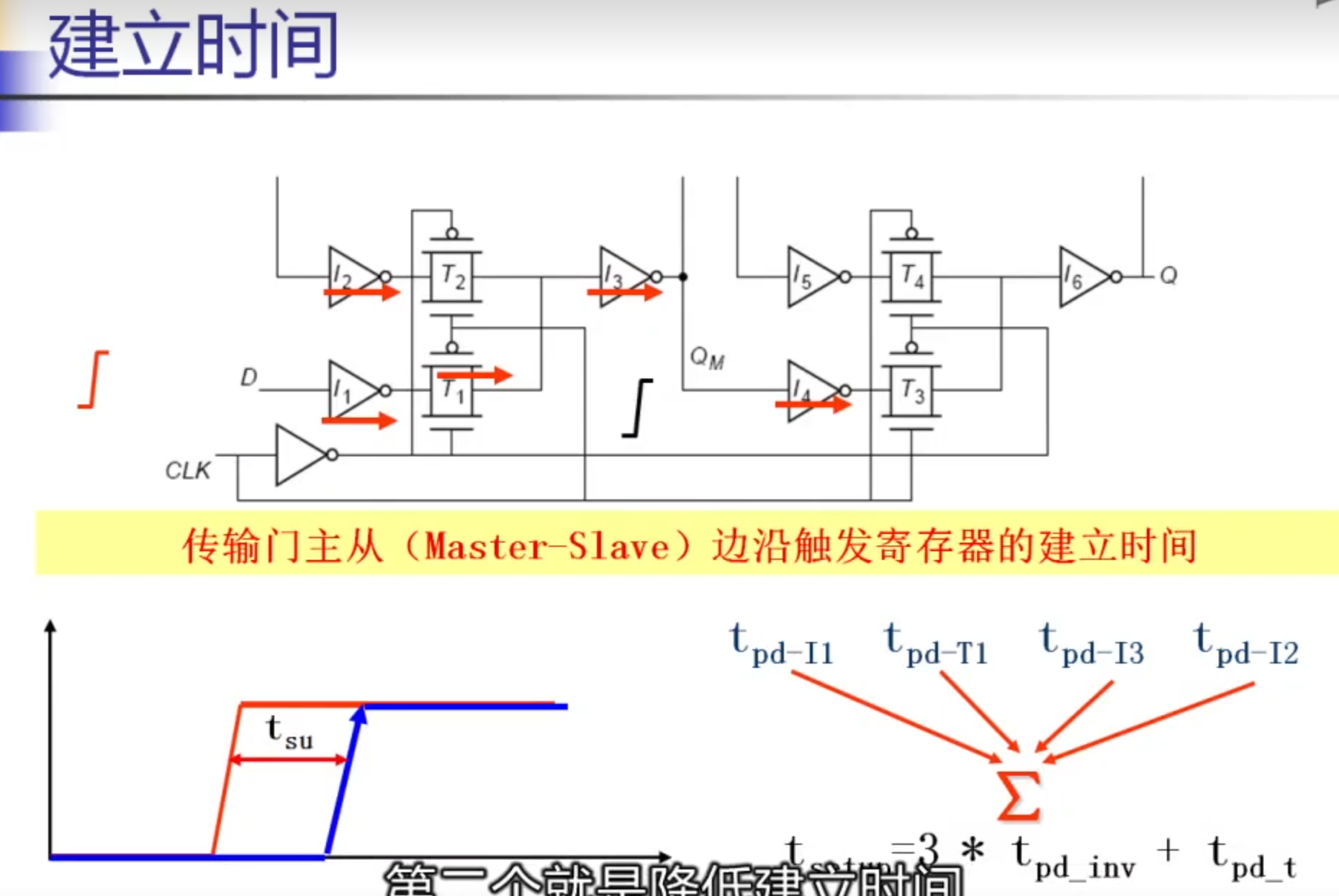

触发器的时序参数

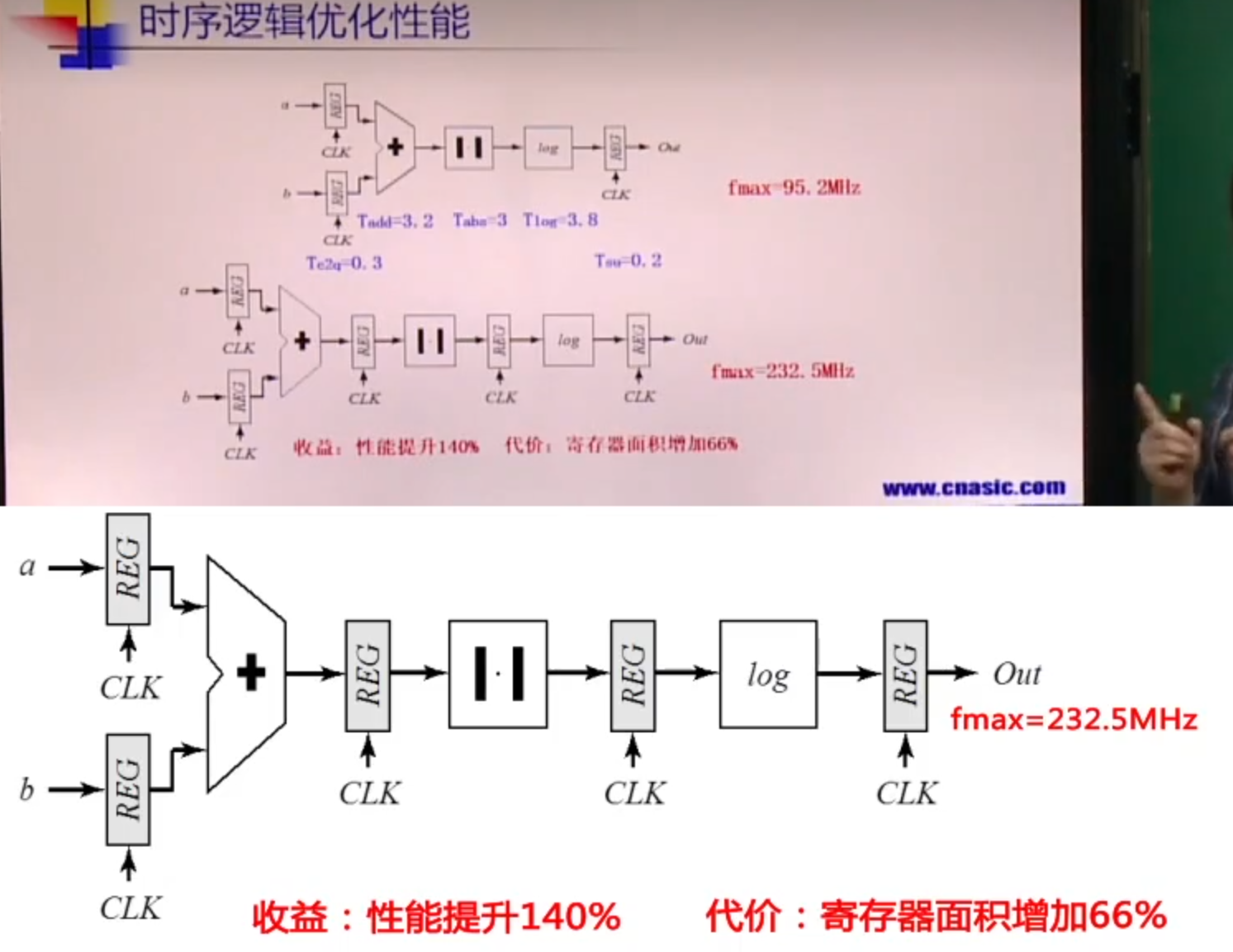

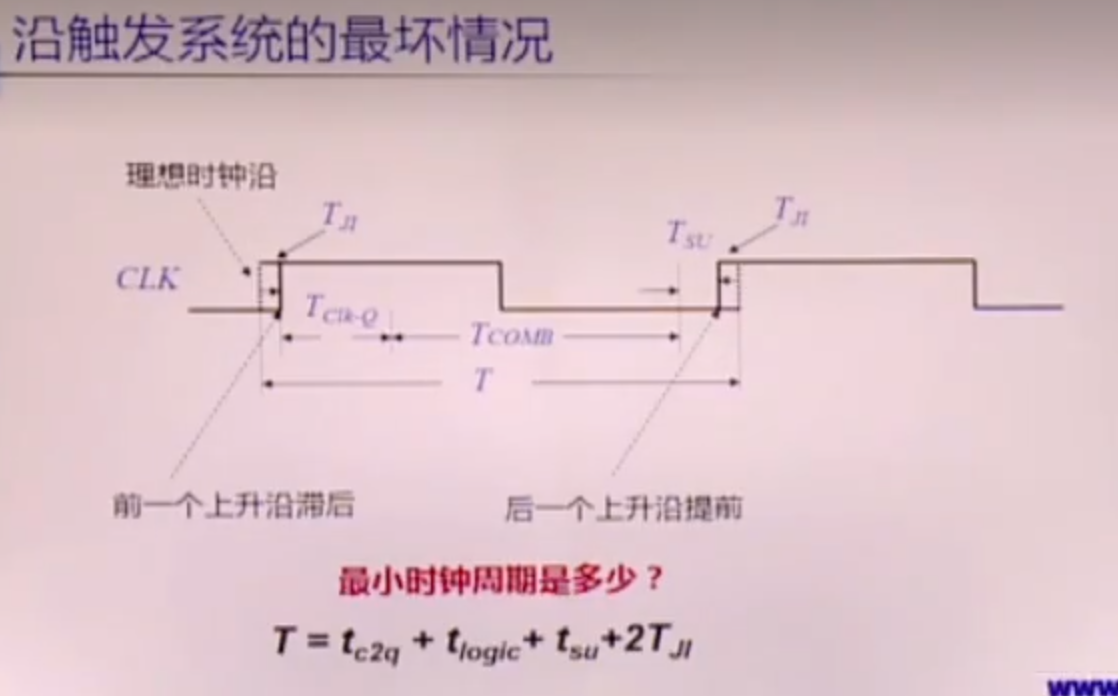

时序逻辑的性能优化

时序逻辑的功耗优化

静态功耗和动态功耗-电容充放电。

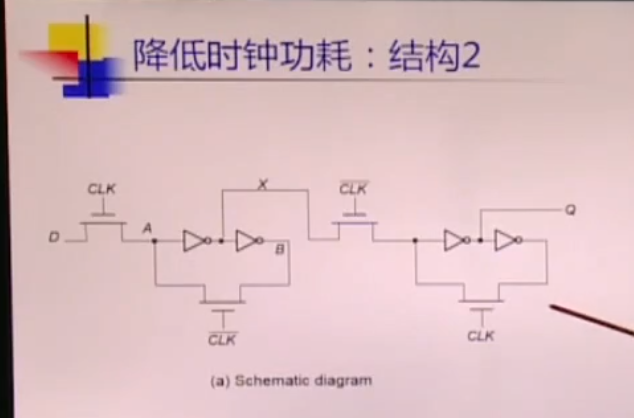

降低时钟的负载

跟主从式结构区别——反馈环路

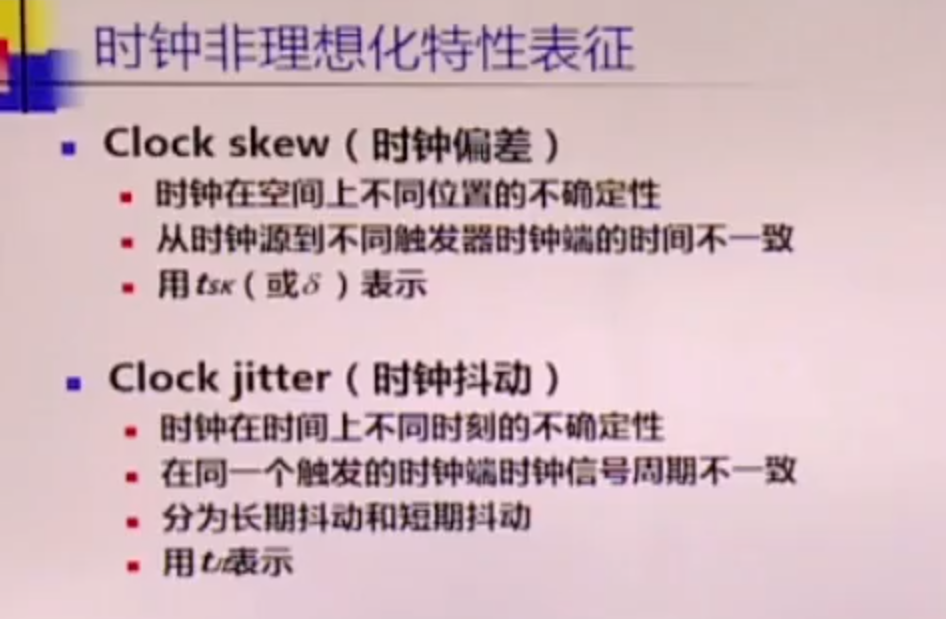

偏差和抖动对电路的影响

抖动一定使性能下降

正的偏差可以使性能上升,反之下降 。

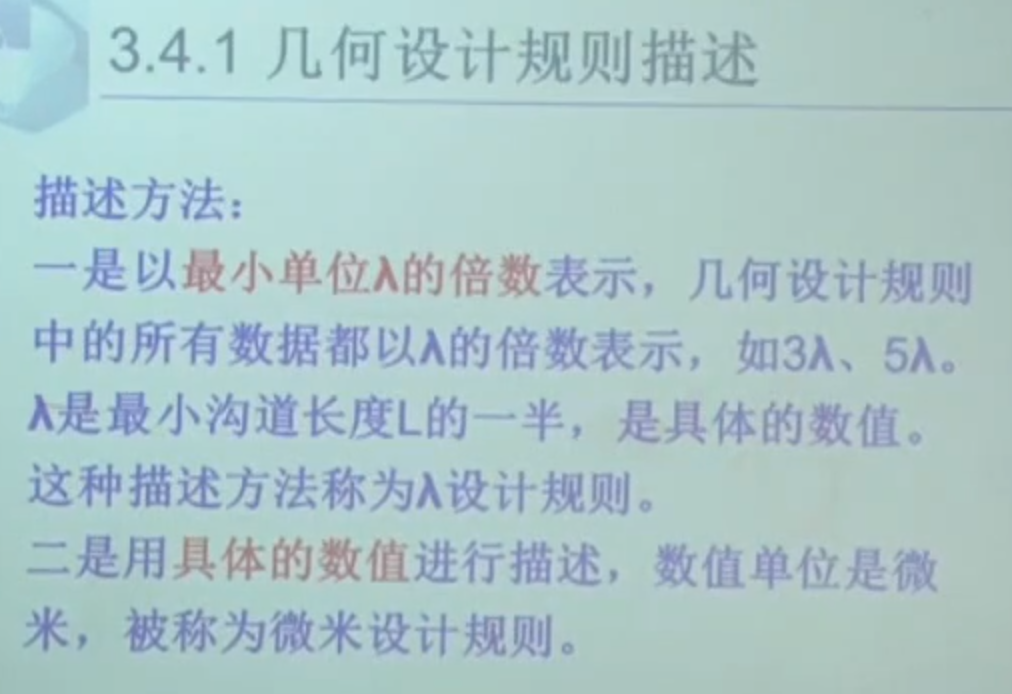

工艺与设计接口

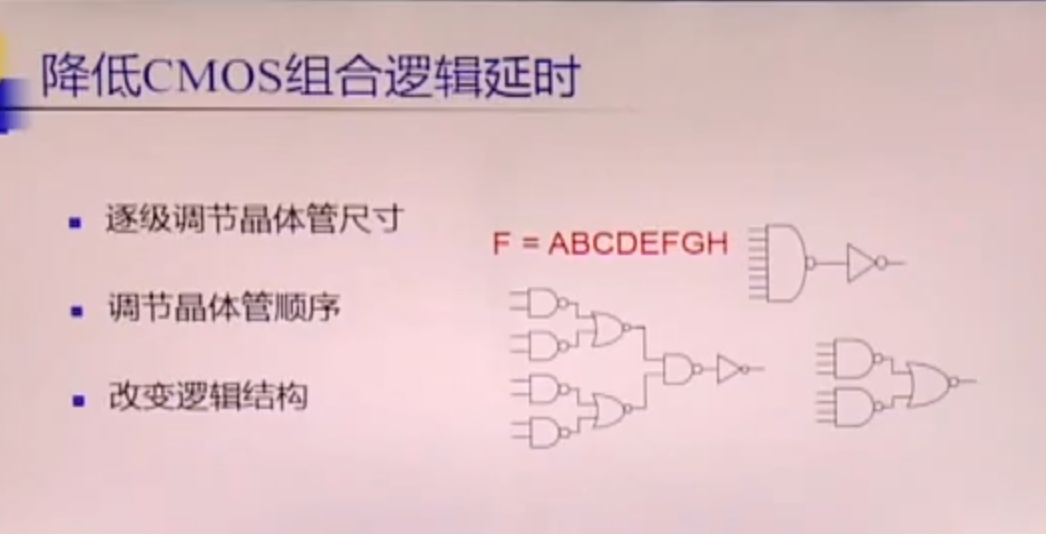

逻辑努力

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!