闩锁效应(Latch-up)

闩锁效应(Latch-up)原理解析

什么是闩锁效应(Latch-up)?

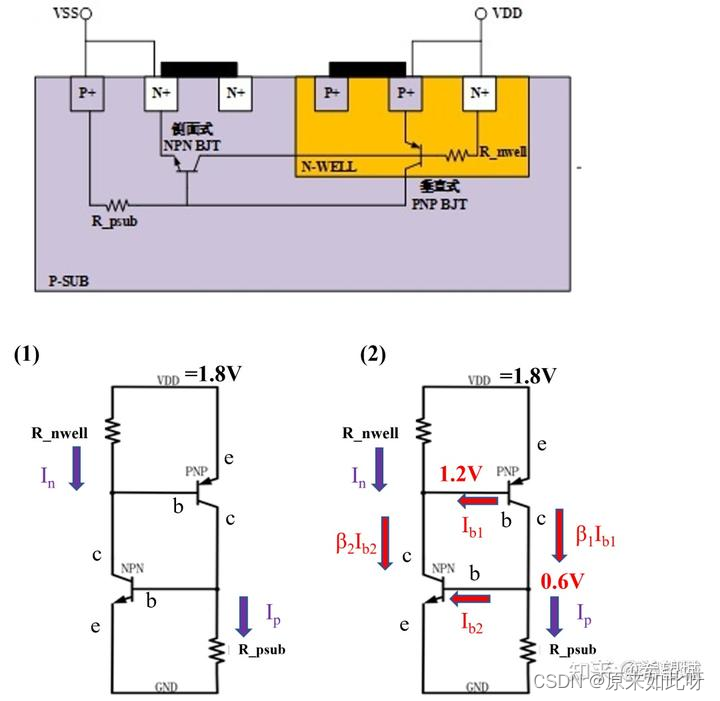

在CMOS N阱设计中,实际上是由于CMOS电路中基极和集电极相互连接的两个PNP和NPN双极性BJT管子(下图中,侧面式NPN和垂直式PNP)的回路放大作用形成的,在两个管子的电流放大系数均大于1时,电流在这两个管子构成的回路中不停地被放大,从而导致管子承受的电流过大而烧毁芯片的一种现象。

产生原理

状态一:假设在N阱或者Psub中由于外界的原因产生了载流子注入,电流分别为In和Ip, 且In* R_nwell=0.6,Ip*R_psub=0.6(假设PN结的导通电压<0.6)。

状态二:在所设压降下(有大电流产生),PNP的基极电位为1.2V, 集电极电位为0.6V, NPN的基极电位为0.6V, 集电极电位为1.2V,此时PNP和NPN的发射结都反偏, 集电结都正偏。从而两个BJT管子可进行电流放大,PNP产生了基极电流Ib1, 则集电极电流IC1=β1Ib1, NPN产生了基极电流Ib2, 则集电极电流IC2=β2Ib2。在近似状态下,Ib1=β2Ib2,Ib2=β1Ib1,因此在后面的循环中,NPN的集电极电流作为PNP新的基极电流进行电流放大,PNP的集电极电流作为NPN新的基极电流进行放大。多次循环之后,电流会被持续放大。

等效电路相当于形成一个正反馈电路(两个BJT的放大系数乘积>1),一旦有压降将PNP管导通,则会最终产生由两个BJT联合放大的电流,NPN和PNP管的支路电流不断循环叠加,达到芯片无法承受,自行停止运行或烧毁。

产生原因

①外部电流进入,例如ESD;

②大尺寸的数字输出反向器;

抑制方案

①源头解决,添加guard ring设计,降低Rwell和Rsub的电阻值,减小压降;阻止载流子进入BJT管;

②尽量让nmos和pmos隔的远一些,使侧面式NPN BJT管子的基区变厚,两个BJT的放大系数乘积<1;

③Substrate contact和well contact应尽量靠近source: 缩短了Rwell和Rsub的电阻的长度,减小了其电阻值

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!