EDA期末突击

发布时间:2024年01月09日

。数模

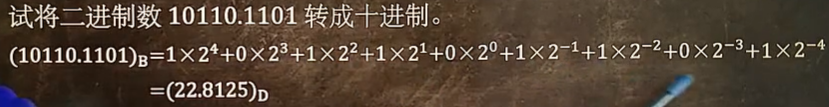

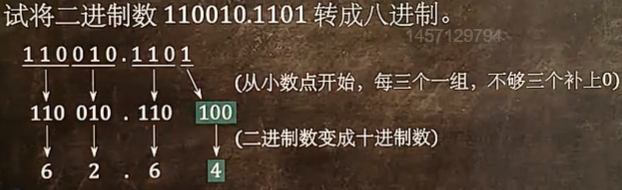

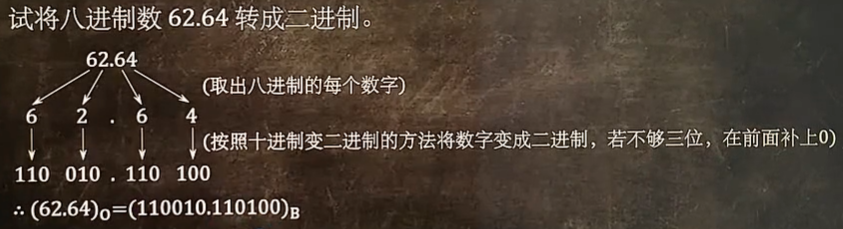

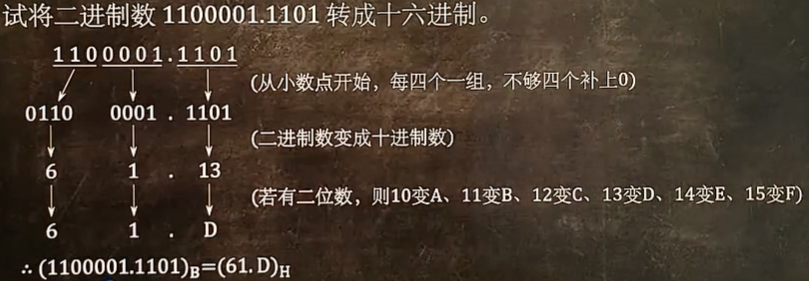

1.1 进制转换

八位补码计算

1.2 化简函数

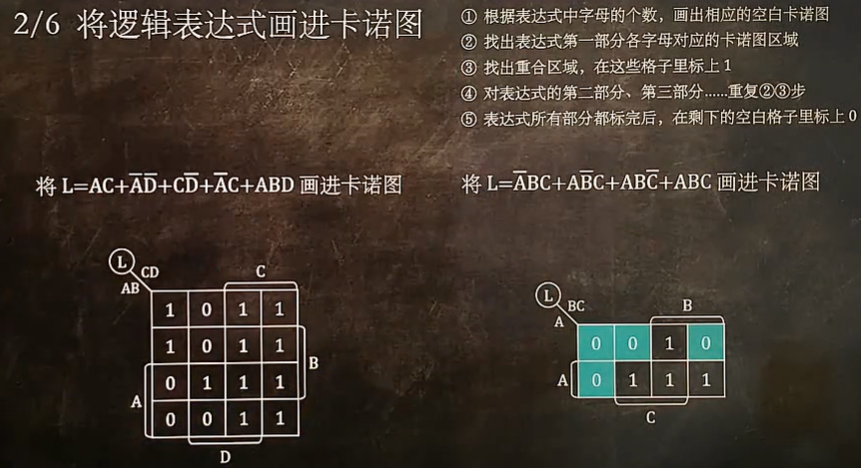

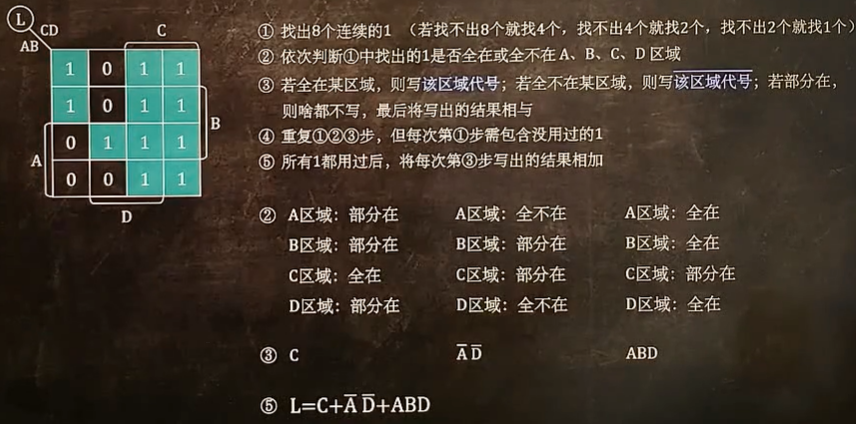

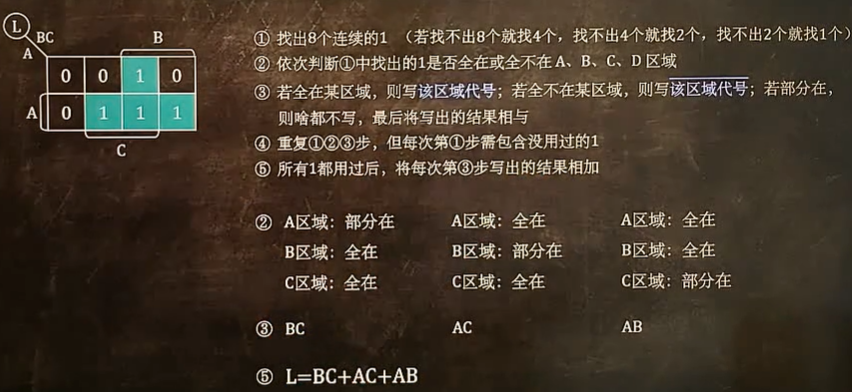

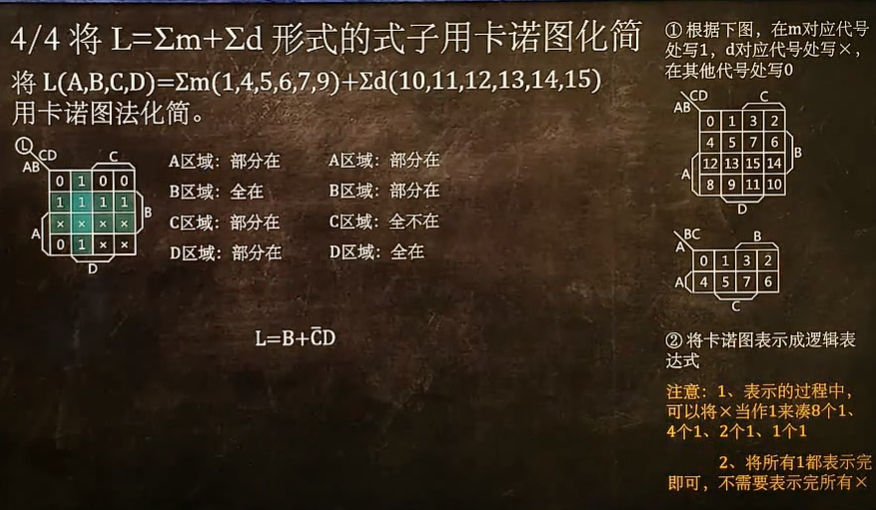

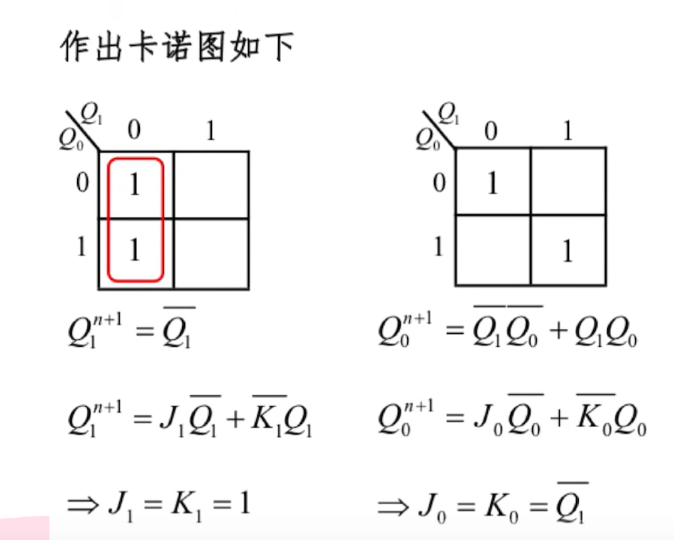

卡诺图

卡诺图另类的化简

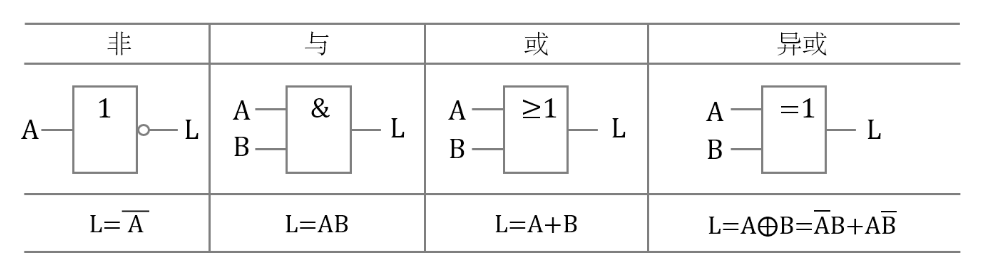

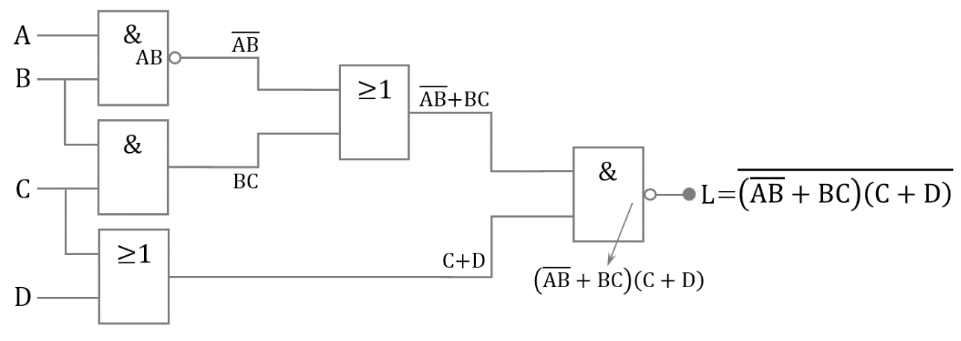

1.3 逻辑图

看逻辑图

写表达式

列真值表,写出标准与或式

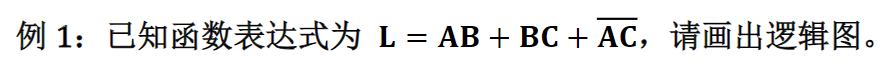

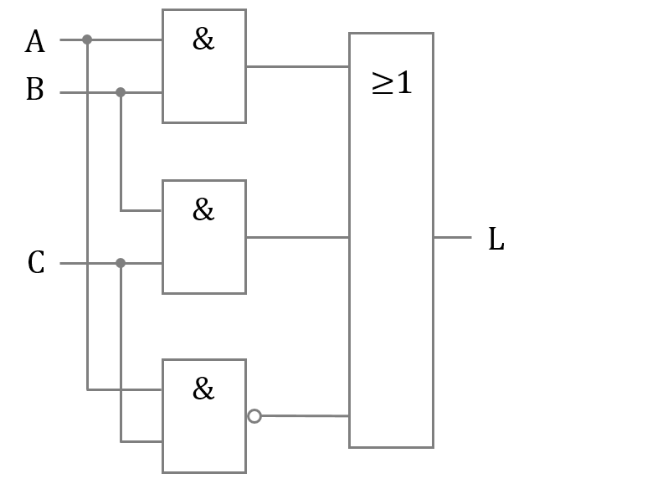

画逻辑图

————————————————

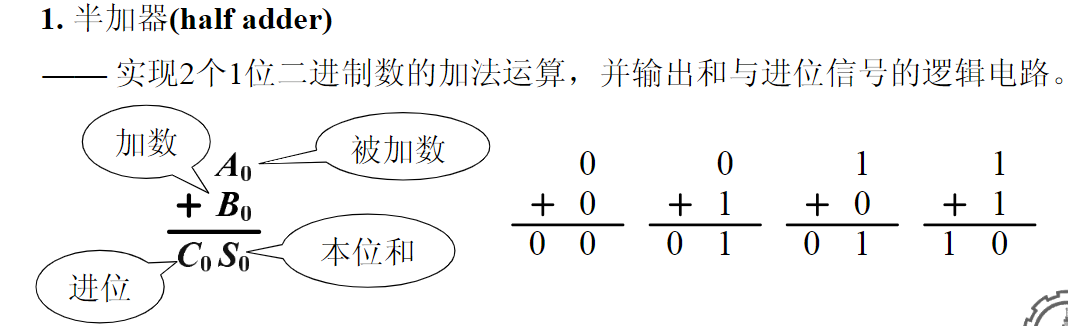

1.4 加法器

半加器

全加器

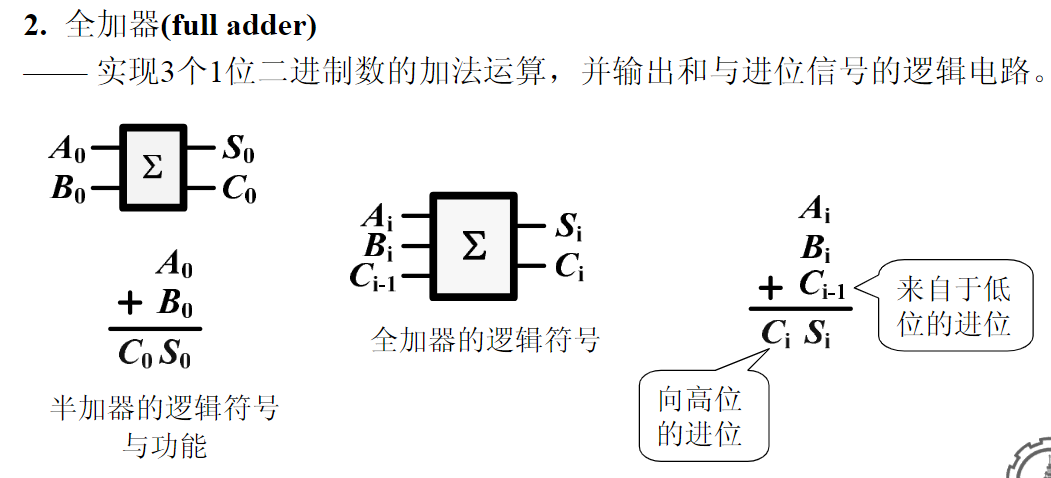

1.5 触发器

——————————————

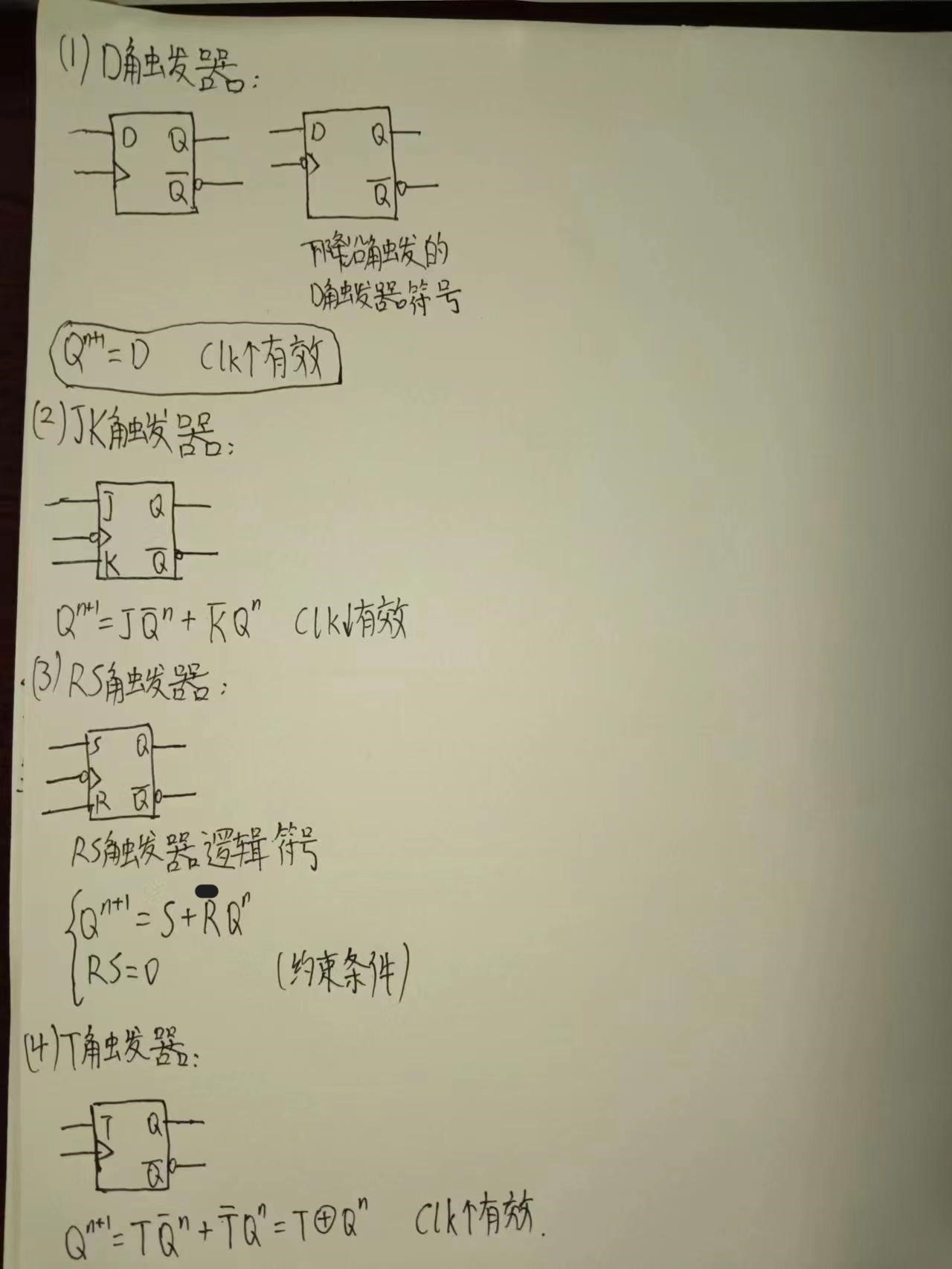

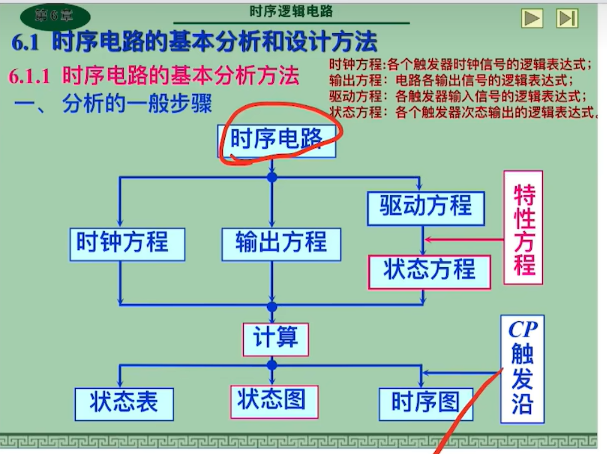

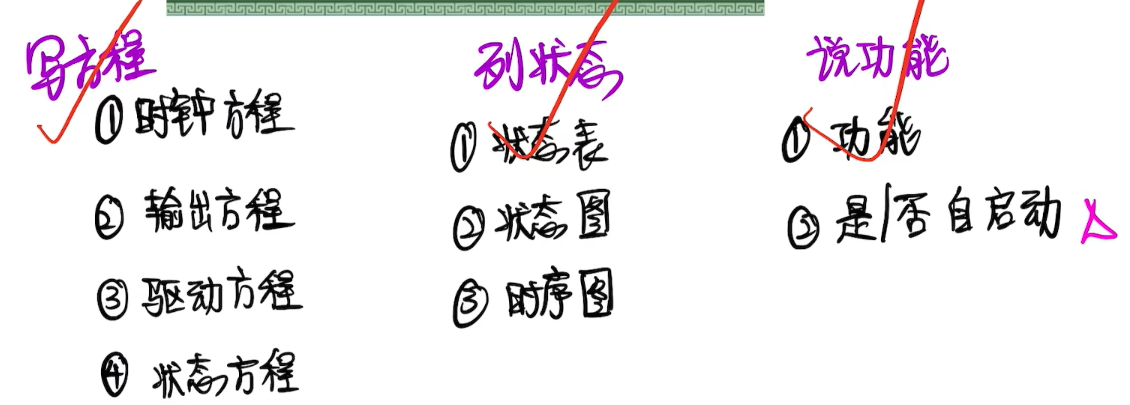

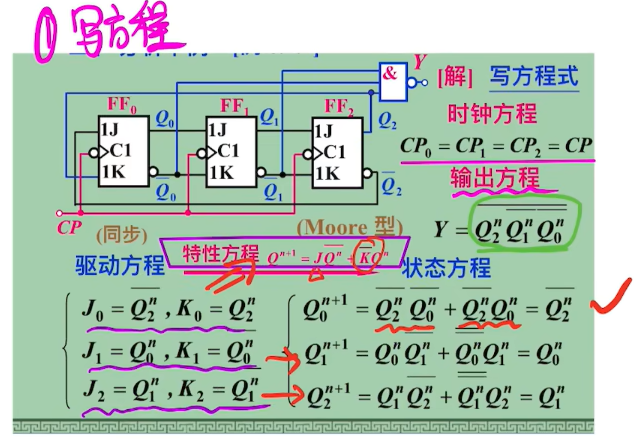

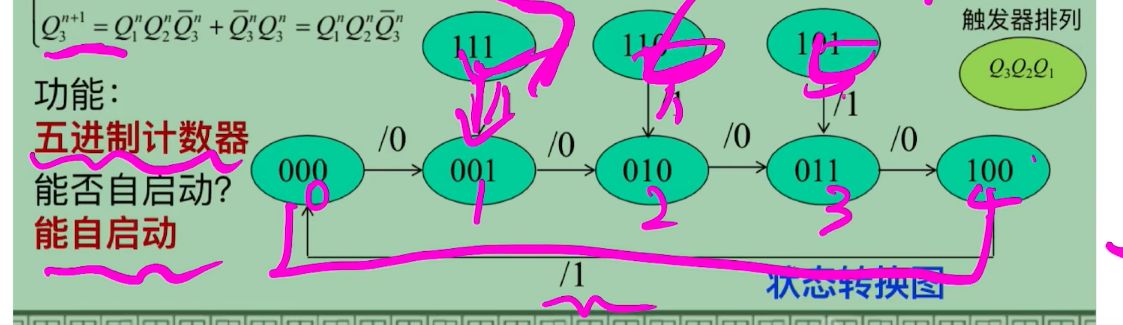

1.6 分析时序电路

——————————

————————————————

————————————————

1 2

2

3

4

5

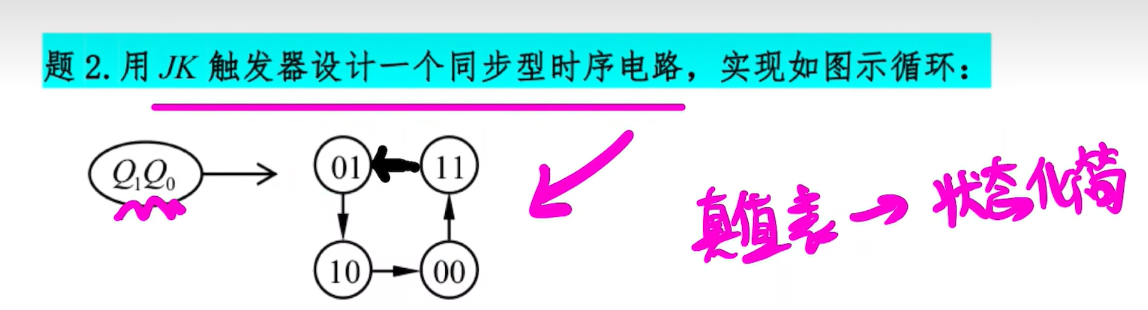

1.7 设计时序逻辑电路

——————————————

例题1

1

2

3

4

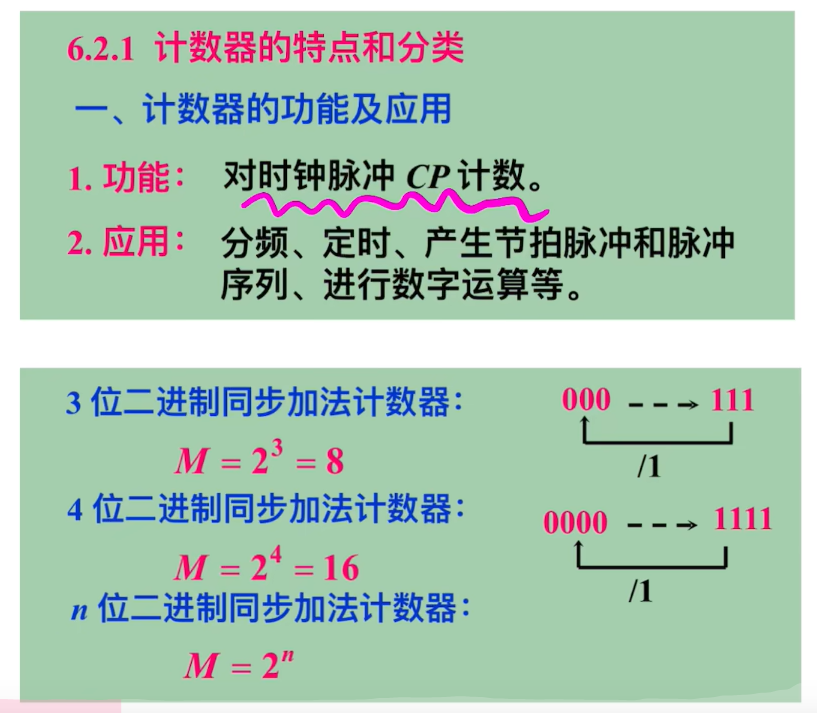

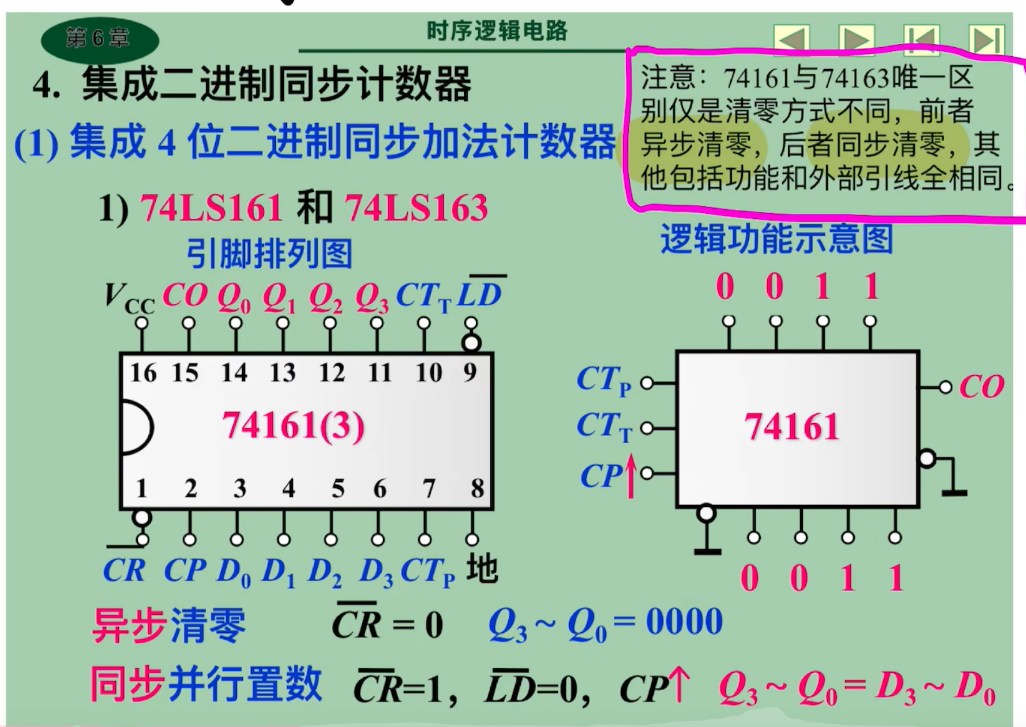

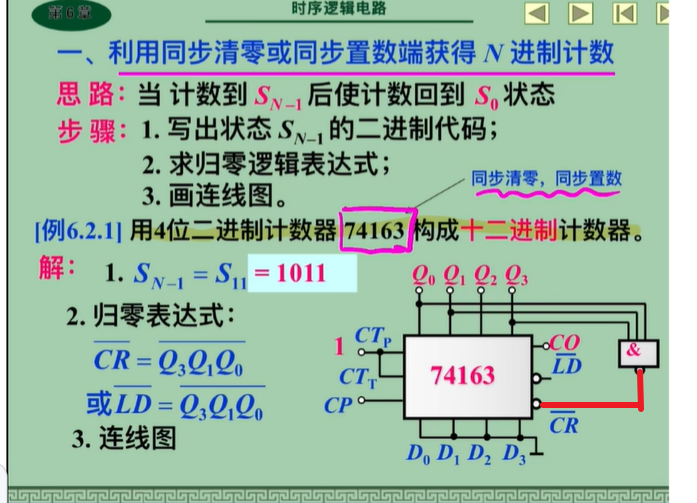

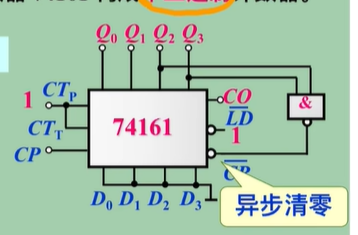

1.8 计数器

———————————————

——————————————

。EDA

1.1 小知识点

reg和wire

reg 主要用于存储状态,而 wire 主要用于信号传递和连接

分配语句的左侧必须是网络类型(例如wire),而过程赋值的左侧(在always 块中)必须是变量类型(例如reg)

always

在Verilog中,always @(*) 是一种敏感列表(sensitivity list)的方式,用于表示该部分的代码块应当在任何敏感信号发生变化时执行。这通常用于组合逻辑,其中输出应该根据输入的任何变化而变化。

有两种类型的always块相关:

- 组合:

always@(*)// 对所有输入信号的变化都敏感 - 时钟:

always@(posedge clk)// 在时钟信号的正边沿上执行的逻辑

#negedge

Verilog 中有三种类型的赋值:

连续赋值(赋值 x = y;)。只能不在过程内部时使用(“始终阻止”)。

程序阻塞赋值:( x = y; )。只能在程序内部使用。

过程非阻塞赋值:( x <= y; )。只能在程序内部使用。

在组合的always块中,使用阻塞赋值。在时钟始终块中,使用非阻塞分配

initial

初始化模块

parameter

用于定义常量值的关键字

文章来源:https://blog.csdn.net/m0_74317362/article/details/135322758

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- Aminooxy-PEG8-acid,2055013-68-6,氨氧基-八聚乙二醇-酸

- Anaconda安装(最新图文版)

- python微博爬虫情感分析可视化系统 舆情分析 python 大数据 TF-IDF算法 Flask框架 毕业设计(源码)?

- 实现分布式锁:Zookeeper vs Redis

- 浅析兼容性测试主要过程

- threejs(18) - 地图模型加载

- 基于卷积神经的车牌识别系统

- CCLinkie转Modbus RTU网关为电力行业带来新机遇。

- 手机无人直播的兴起

- mysql的索引原理