vivado 输出延迟

输出延迟

set_output_delay命令指定输出端口相对于设计接口处的时钟边缘。

当考虑应用板时,此延迟表示以下各项之间的相位差:

1.数据从FPGA的输出封装引脚通过板传播到另一个设备,以及

2.相对基准板时钟。

输出延迟值可以是正的,也可以是负的,这取决于相对的时钟和数据相位在FPGA之外。

使用输出延迟选项

尽管-clock选项在SDC标准中是可选的,但Vivado Design需要它套件工具。

相对时钟可以是设计时钟,也可以是虚拟时钟。

输出延迟命令选项包括:

?最小和最大输出延迟命令选项

?时钟下降输出延迟命令选项

?添加延迟输出延迟命令选项

最小和最大输出延迟命令选项

-min和-max选项为最小延迟分析(保持/删除)和最大延迟分析(设置/恢复)。如果两者都不使用,则输出延迟值适用于两个最小值和最大。

时钟下降输出延迟命令选项

-clock_fall选项指定输出延迟约束应用于定时路径由相对时钟的下降时钟沿捕获。如果没有此选项,Vivado IDE默认情况下仅假设相对时钟的上升沿(在设备外部)。不要将-clock_fall选项与-rise和-fall选项混淆。这些选项指的是数据边缘而不是时钟边缘。

添加延迟输出延迟命令选项

在以下情况下,必须使用-add_delay选项:

?最大输出延迟约束已经存在,并且

?您希望在同一端口上指定第二个最大输出延迟约束。

对于最小输出延迟约束也是如此。此选项通常用于约束相对于一个以上时钟边沿的输出端口,例如DDR中的上升沿和下降沿接口,或者当输出端口连接到使用不同时钟的几个设备时。

set_output_delay命令选项的使用

以下示例介绍了set_output_delay命令选项的典型用法。对于有关输出延迟约束方法的其他信息,请参阅中的此链接《FPGA和SoC的超快设计方法指南》(UG949)。

输出延迟示例一

此示例定义了相对于先前定义的sysClk的min和的输出延迟最大分析。

输出延迟示例二

此示例定义了相对于先前定义的虚拟时钟的输出延迟。

输出延迟示例三

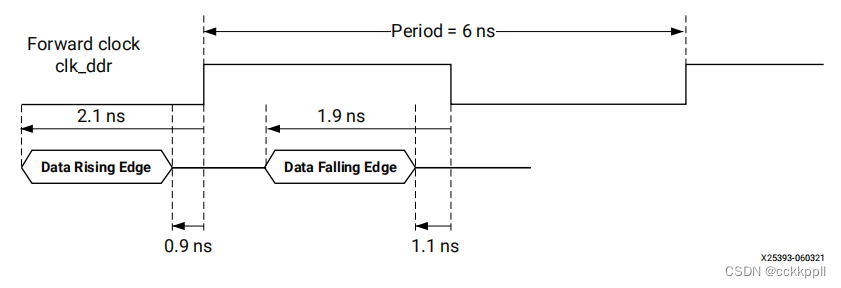

此示例指定相对于DDR时钟的输出延迟值,该值为min的不同值(保持)和最大(设置)分析。

此示例根据的上升沿和下降沿启动的数据创建约束设备外部的clk_ddr时钟,到对两者都敏感的内部触发器的数据输出上升和下降时钟边沿。

输出延迟示例四

此示例指定STARTUPE3内部引脚(UltraScale+设备)对从结构到STARTUPE3的路径进行计时。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 使用Spring Boot操作Redis、ES、MongoDB举例

- Java 数据结构篇-实现 AVL 树的核心方法

- 【重学C语言】二、前期准备和第一个C程序

- 从零开始了解Figma:全面介绍这款设计工具,让你熟练运用!

- 常见的排序算法---快速排序算法

- Java设置session过期时间的几种方法(亲测有效)

- 【C语言】动态内存管理之4个内存函数`malloc`,`free`,`calloc`和`realloc`深度了解

- 勒索病毒:原理与防御

- 如何安装T4显卡的驱动

- 第三方软件测试机构提供哪些测试服务和测试报告?