Quartus II使用小技巧

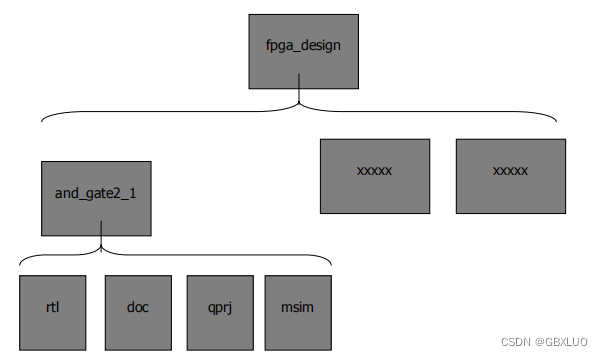

工程结构:

在建立完某项设计的文件后,依次在其里面新建四个文件夹,分别为:rtl、qprj、msim、doc。

rtl文件夹用于存放设计的源文件。

doc文件夹用于存放设计的一些文档性的资料。

qprj文件夹用于存放quaruts 工程以及quartus生成的一些过程性文件。

msim文件夹用于存放仿真文件。

如何查看一个Quartus工程用的是什么版本呢?

用notepad++打开工程名.qsf文件,查看最后一次打开使用的版本即可。

工程名.qsf文件部分内容如下:

set_global_assignment -name ORIGINAL_QUARTUS_VERSION 21.4.0

set_global_assignment -name PROJECT_CREATION_TIME_DATE "22:28:56 ?JANUARY 09, 2024"

set_global_assignment -name LAST_QUARTUS_VERSION "21.4.0 Pro Edition"

快捷键:

| Ctrl+L | Start Copilation | 开始全局编译 |

| Ctrl+K | Start Analysis & Synthesis | 开始分析与综合 |

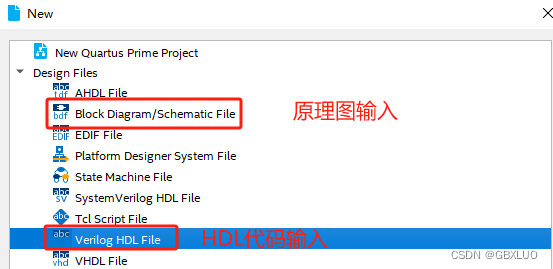

输入设计有三种:

HDL代码输入、原理图输入、原理图和HDL代码混合输入。

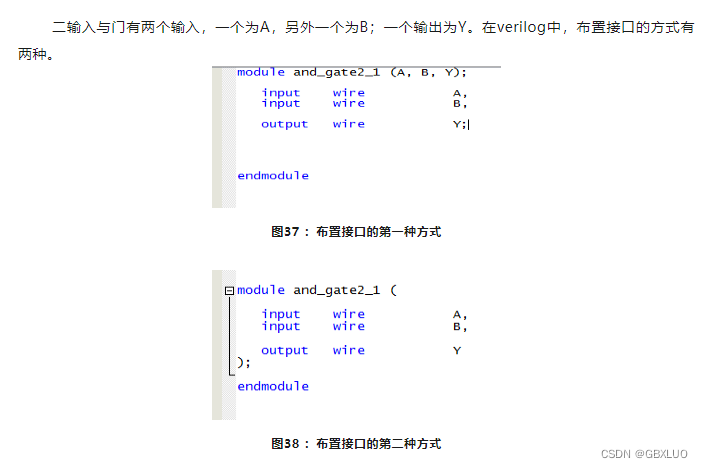

Verilog布置接口的两种方式:

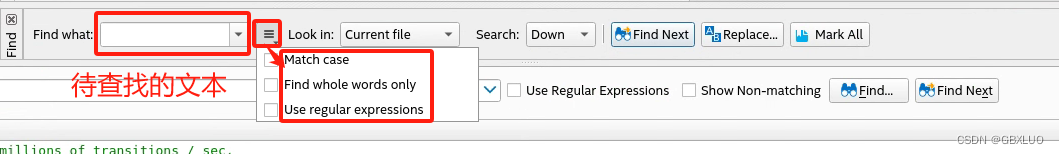

使用Quartus21.4自带编辑器查找变量:

快捷键:Ctrl+F

弹出Match case:匹配大小写

Find whole words only:只显示完全相同的文本

Use?regular expressions:使用正则表达式

Quartus可以直接打开的文件类型

qpf、stp1.stp、sof文件均可直接拖到桌面Quartus图标上,从而Quartus直接打开该文件。

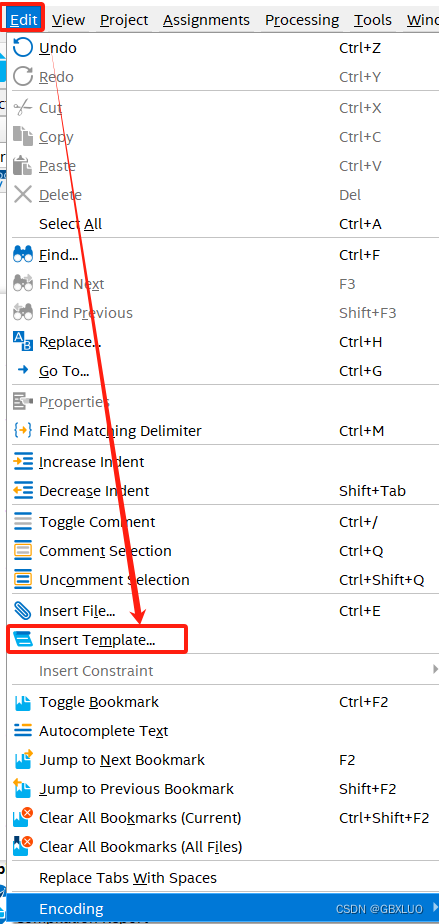

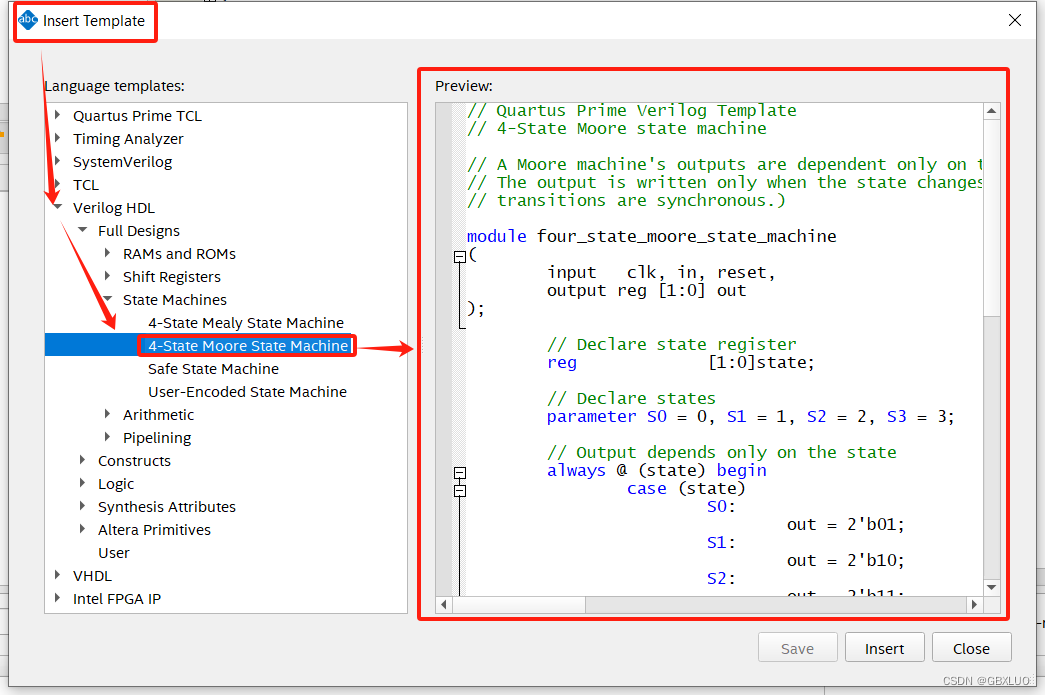

在Quartus中Using Verilog Templates(Verilog模板)

在打开Quartus自带的文本编辑器的情况下,在文本编辑器中左键单击确定位置,Edit > Insert Template > Verilog HDL,选择自己想要添加的模板。

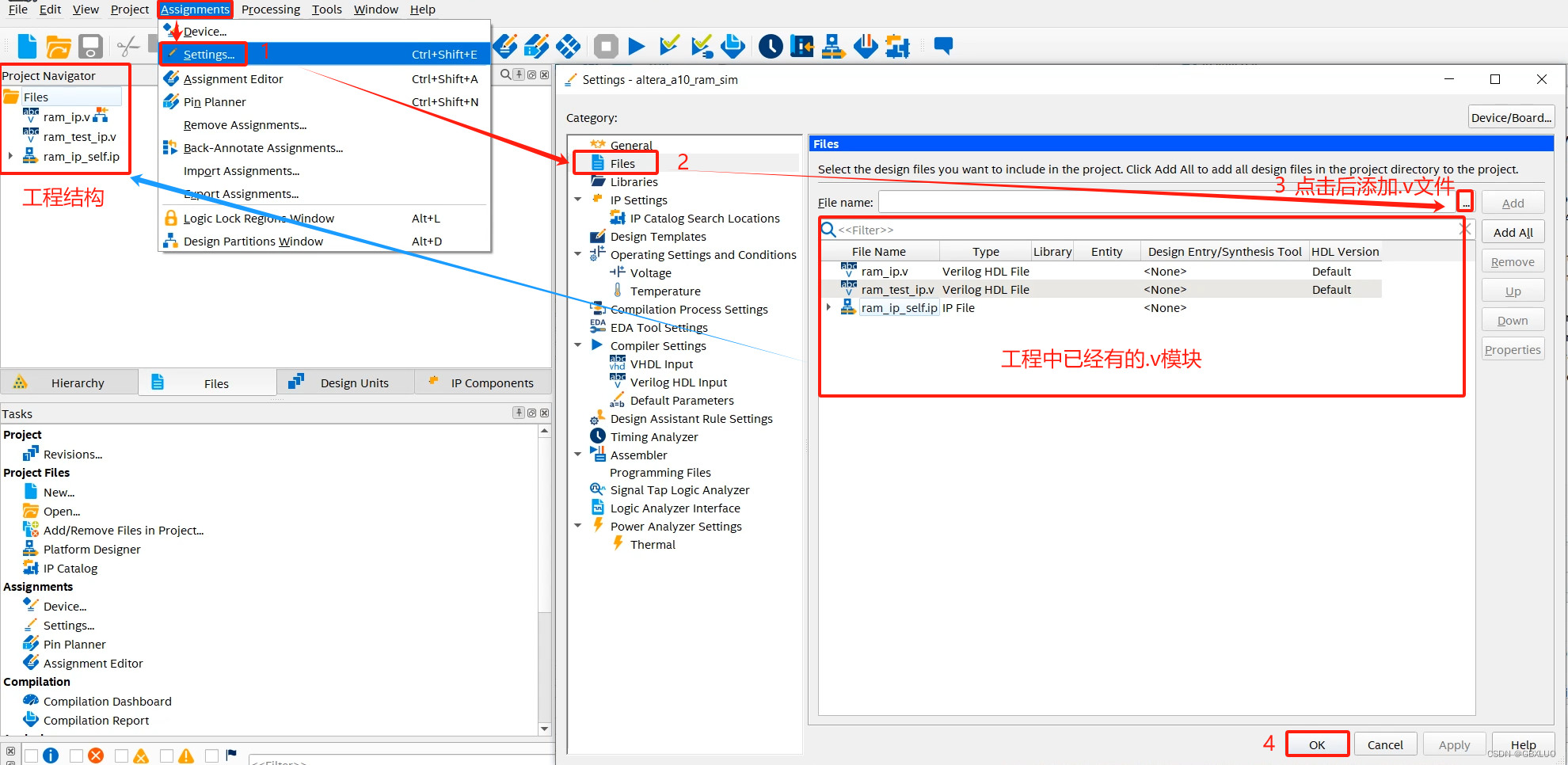

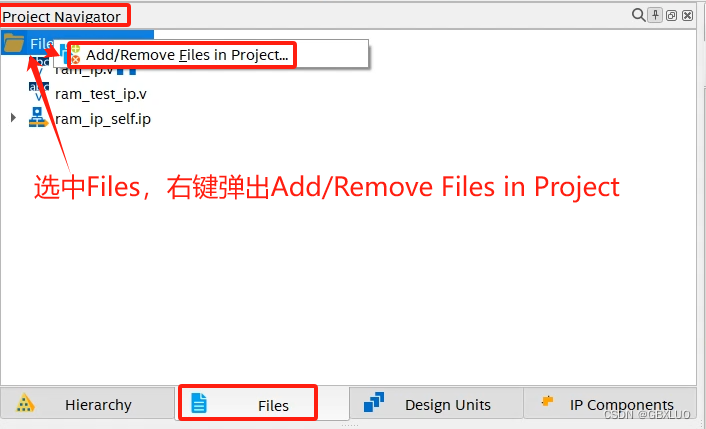

Adding Design Files to a Project

方法一:

Assignments > Settings > Files > 点击File name 右边的...,添加.v文件。

方法二:

Project Navigator > 左键单击选中Files窗口?> 右键单击 Files弹出Add/Remove Files in Project

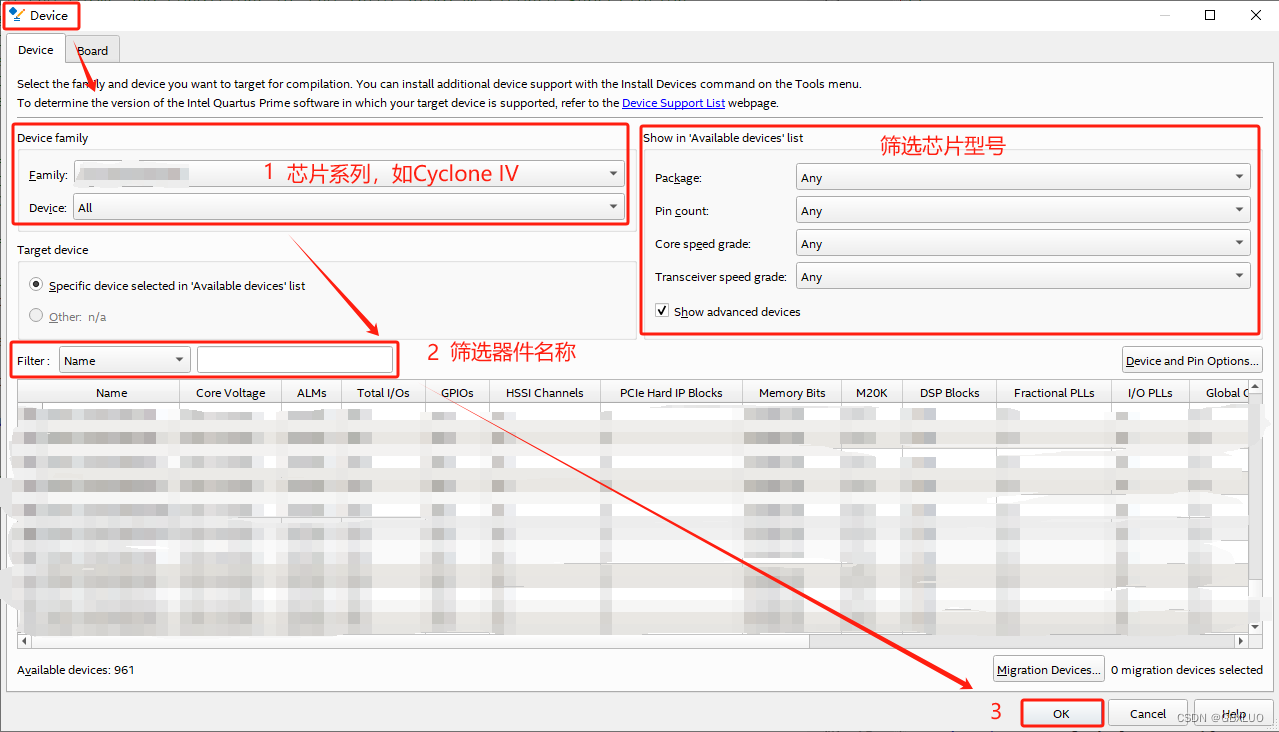

新建Quartus工程时选的芯片不对,需要重新选择:

Assignment 》Device,在弹出的Device弹窗中选择号想要的芯片后点击OK即可。

常用方法:选择芯片系列后,在Filter中输入完整器件型号,确认芯片后点击OK即可。

两个同版本Quartus工程可以共用同一个stp1.stp文件

有两个Quartus工程:q_pfj_1.qpf与q_prj_2.qpf,其中q_prj_2.qpf是q_prj_1.qpf的衍生工程,两个工程想要在Signal Tap Logic Analyzer中观察的信号一样,直接将q_prj_1.qpf中已经设置好的stp1.stp挪到q_prj_2.qpf工程中,替换掉q_prj_2.qpf中原来的stp1.stp文件,即可在q_prj_2.qpf中的Signal Tap Logic Analyze抓取相同的信号。

但是注意换了stp1.stp的要q_prj_2.qpf工程要重新编译才能生效。

多个工程同理;

为什么会有多个工程?

因为服务器以及Quartus可以同时打开多个工程,而每个工程验证的方向不一样,因此会存在临时在Signal Tap Logic Analyzer中新增一些观察信号,这时笨办法是重复将其他工程一样设置一遍,省事的办法是直接copy已经设置好的stp1.stp到目的工程目录下覆盖即可。

可以在qsf文件中设置stp文件:

set_global_assignment -name SIGNALTAP_FILE stp1.stp

合并两个相同Quartus版本的工程:

1、将prj_1整个文件夹copy到prj_2的prj_2中;

2、修改prj_2的prj_2.qsf,添加prj_1的ip与.v文件,以及添加prj_1中有,而prj_2中没有设置的引脚约束等;

prj_2.qsf添加ip文件:

set_global_assignment -name IP_FILE ../fifo/fifo_test.ip

prj_2.qsf添加ip的约束文件(不是所有的ip都有sdc约束文件):

set_global_assignment -name SDC_FILE ../fifo/fifo_test.sdc

prj_2.qsf添加qip文件:

set_global_assignment -name QIP_FILE ../self_fifo/self_fifo.qip

prj_2.qsf添加qsys文件:

set_global_assignment -name QSYS_FILE ../hdmi_example/aux_mux.qsys

prj_2.qsf添加tcl脚本文件:

set_global_assignment -name TCL_SCRIPT_FILE ../rtl/FPGA_number.tcl

prj_2.qsf添加system_verilog.sv文件:

set_global_assignment -name SYSTEMVERILOG_FILE ../fifo/fifo.sv

prj_2.qsf添加verilog.v文件:

set_global_assignment -name VERILOG_FILE ../rtl/led_test.v

note:QIP文件里的内容是典型的脚本格式,如上。

3、很重要的一步,将prj_1中的顶层文件例化到prj_2中的顶层文件中

4、分析与阐释,先检查错误

5、全编译,生成sof文件验证

注意:以qar的形式打包prj_2工程得到一个prj_2.qar的文件,该文件内部的prj_1文件夹下仅有ip与.v模块,不能再使用Quartus软件打开prj_1.qpf工程了,因为解压后的prj_2_restored文件夹下的prj_1文件夹内已经没有了prj_1.qpf。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- python venv 虚拟环境创建激活和pip包管理和 包版本依赖文件 requirements.txt 使用指南

- 2023 年精选:每个 DevOps 团队都应该了解的 5 种微服务设计模式

- BASE64DecodedMultipartFile.base64ToMultipart的使用

- Nmap端口扫描

- 112.Qt中的窗口类

- 力扣第 375 场周赛 解题报告 | 珂学家 | 区间合并+组合数学

- LVS+Keepalived 高可用群集

- Ubuntu Desktop 22.04 设置 ssh 超时时间

- 一天吃透消息队列面试八股文

- LeetCode精选算法200题------(1)266.回文排列