数字IC实战后端项目| 必须掌握的28个SoC低功耗项目经验!

吾爱IC社区第四期低功耗四核A7顶层Top Hierarchical的数字IC后端设计实现训练营将于2024年2月份开班!考虑到今年经济大环境,为了保证广大学员的学习效果和就业率,本次只招募10个学员,真正做到超小班教学。有需要的同学,可以尽快私信小编,进行预约报名。当然实际发现参加这个训练营的学员大部分都是往期学员和已经参加工作的数字IC后端工程师。在这里感谢大家的支持和认可!

企业5年左右的数字后端工程师都不一定有机会接触到这类项目。服务器使用时间为2.5个月!而且包学会!

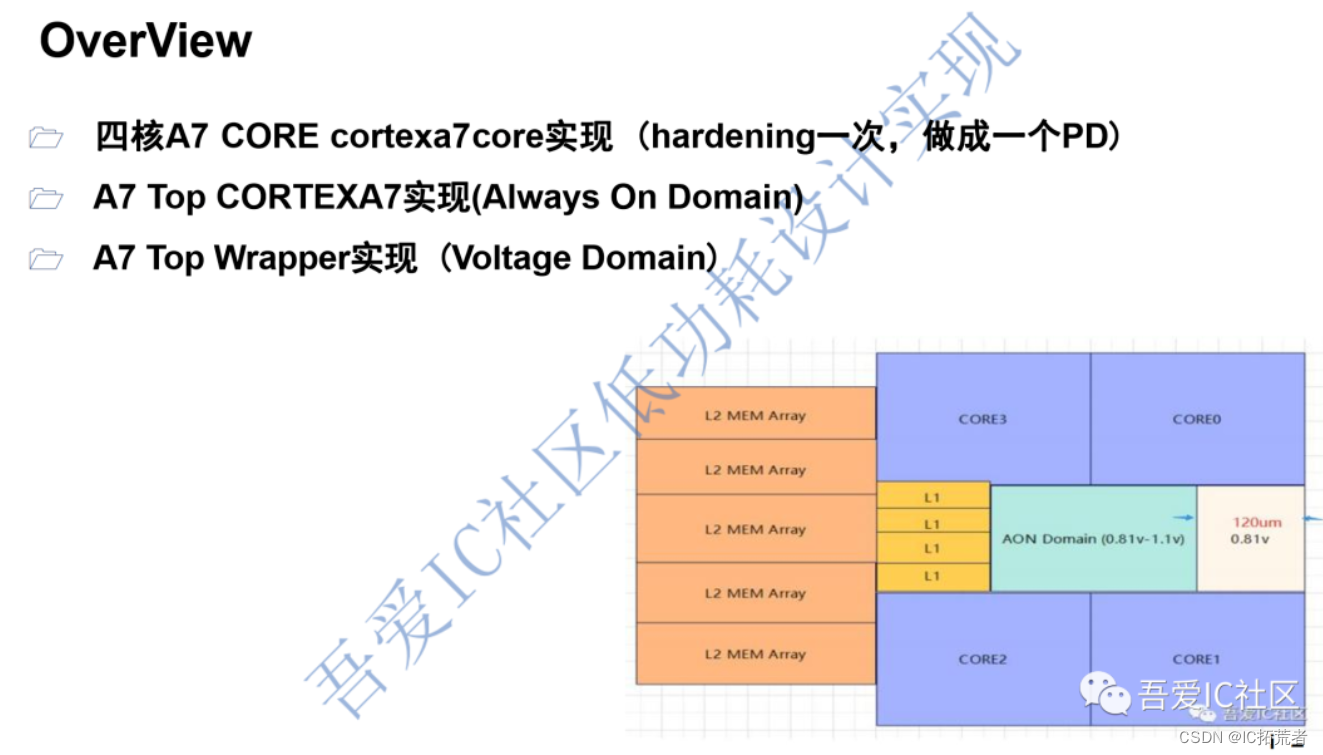

实战项目:基于TSMC 28nm低功耗四核A7 Top Hierarchical Flow的物理实现

主时钟频率:>= 1.1GHz ssg0p81v125c +rcworst125c

设计规模:110万instance (包含若干个子模块和顶层设计)

Power Domain数量:4个

Voltage Domain数量:2个

实现方式:Hierarchical Flow +Low Power Flow

项目成果:Timing Signoff Timing Clean,DRC,Antenna,LVS clean,Redhawk IR Drop符合Signoff要求

涉及EDA工具: Innovus,Starrc,PrimeTime,Calibre和Redhawk

授课形式: 直播授课+实践课+每日问题解答+远程协助。(每周直播两次,每次近2小时)

讲师:吾爱IC社区星主本人

带子模块的IO 接口时序优化

在职场中,真的没有什么天赋异禀的人,更没有天生的技术大佬,只不过他们更加勤奋,更加追求进步,时时刻刻都在学习吸收新的知识,有日拱一卒的工匠精神。只是他们把大家平时用来刷视频,玩游戏,社交的时间拿来学习充电了而已。小编做为一线12年后端经验的后端工程师,身边真的有不少20年左右的技术大牛,他们每个人都非常勤奋,努力,周末的时间大部分都是用来学习的!

通过这个高级IC后端训练营实战项目课程的学习,大家可以学习掌握积累到如下数字IC后端实现的技能和经验。

1)熟练掌握数字后端设计实现层次化Hierarchical Flow设计实现全流程

全面解析Hierarchical Flow和传统Flatten Flow的区别,通过项目实战来诠释Hierarchical Flow同Flatten Flow在数字IC后端实现中的不同做法。

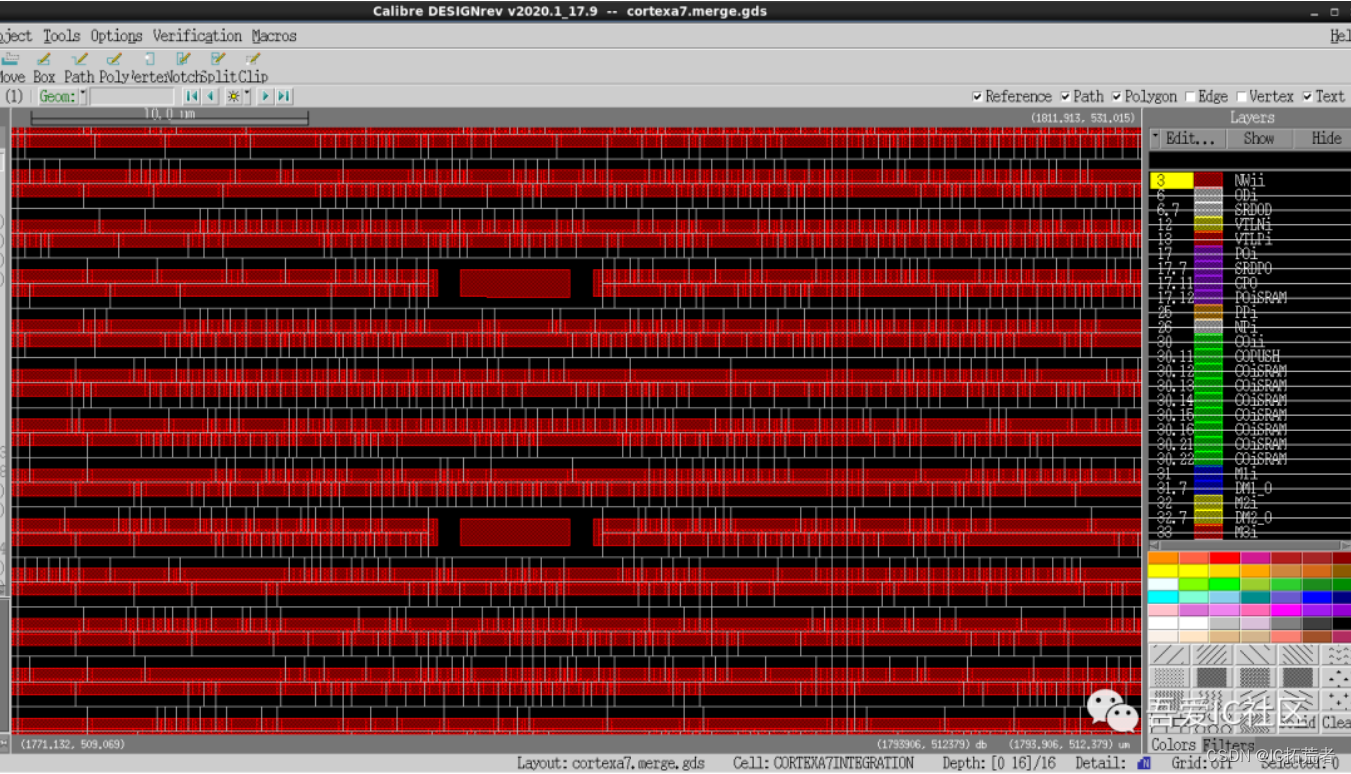

比如placement阶段需要如何设置clock latency,Placement阶段如何优化顶层Top和子模块Cortexa7core的接口时序,时钟树综合阶段要如何做好顶层和子模块reg的clock balance,route阶段要如何规避子模块和顶层的DRC,物理验证DRC,LVS阶段要如何处理子模块cortexa7core,静态时序分析要如何做hierarchical和flatten的Timing signoff等等。

这些问题是不是妥妥的IC后端笔试面试题?在学习和做项目这个过程,也把项目相关笔试面试题都掌握了。

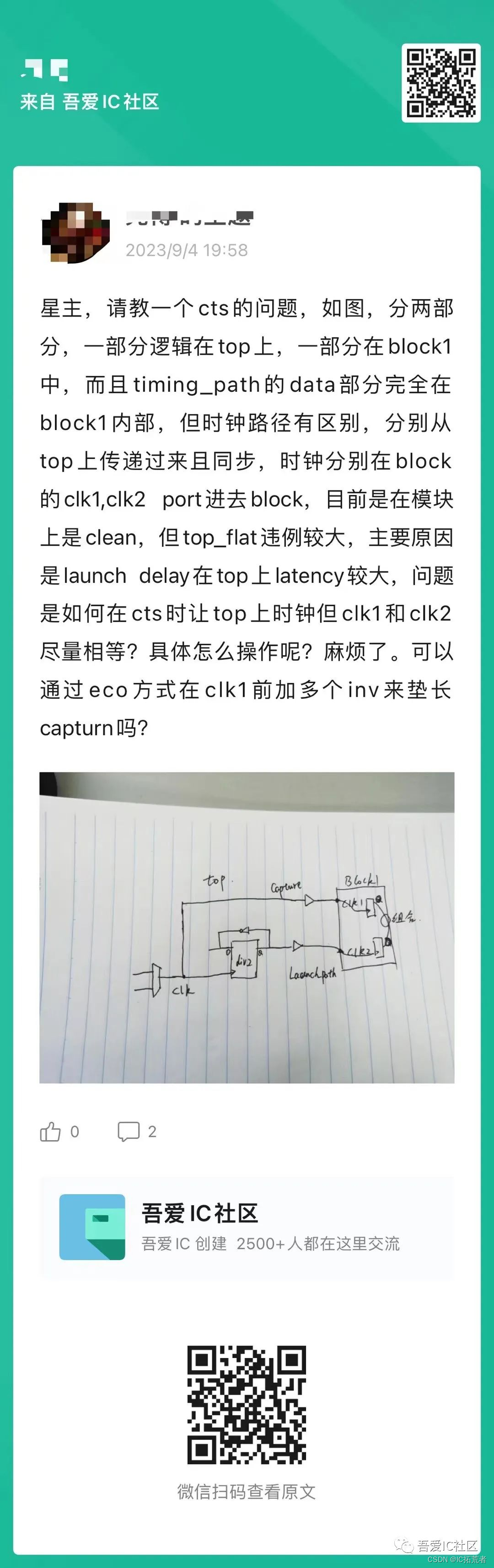

就像咱们知识星球上这个问题,学完这个课程就能够轻松应对。这个问题也是今年某IC企业的数字IC后端笔试题。

2)掌握低功耗设计理论,熟悉常见低功耗cell(isolation cell,level shifter cell)的用法及其实现经验

熟悉数字IC设计实现中所有低功耗技术手段,比如clock gating,power gating,Multi-VT等技术手段。并通过项目实操来掌握常见低功耗cell在数字IC后端实现中的相关技术经验及其checklist检查。比如如何确保isolation cell摆放到合适的power domain,isolation cell的input电气特性,level shifter cell secondary pg连接及secondary pg net的电阻检查等。

3)根据低功耗设计实现需求编写upf验证upf内容

根据需求划分power domain,voltage domain,选择合适的isolation cell类型和level shifter cell类型。通过实际后端项目加载upf后进行verifyPowerDomain相关检查。

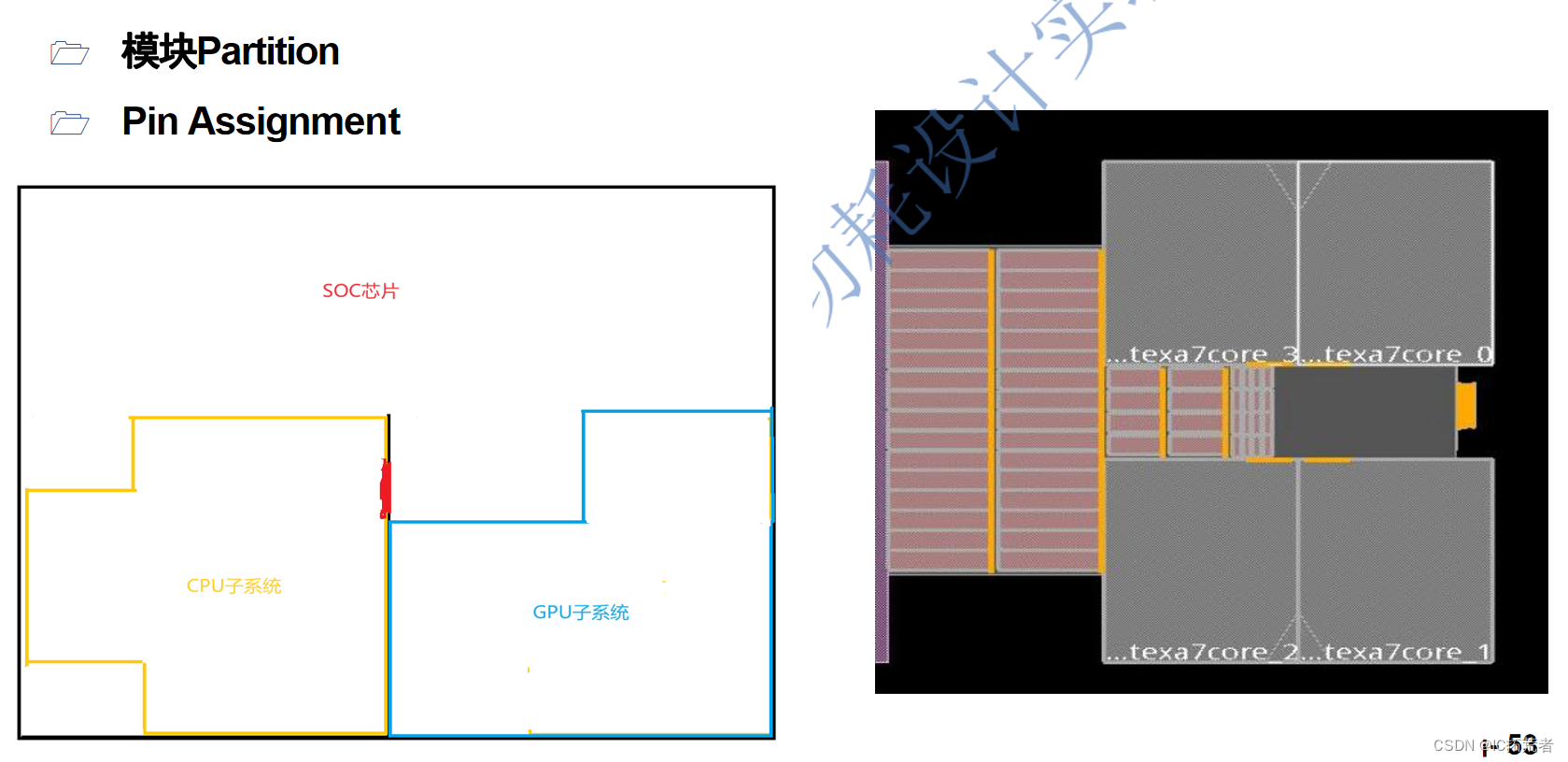

4)根据顶层release的top floorplan def进行cpu子系统各模块的partition以及pin assignment

通过本实战项目的实操,可以熟练掌握Hierarchical Flow自顶向下的Partition和Pin Assignment Flow。通过顶层的模块切分,release对应数据给各个子模块,供子模块进行后端实现(本项目涉及两个层次的模块Partition)。

【机密】从此没有难做的floorplan(数字后端设计实现floorplan篇)

数字IC后端实现TOP Floorplan专家秘籍

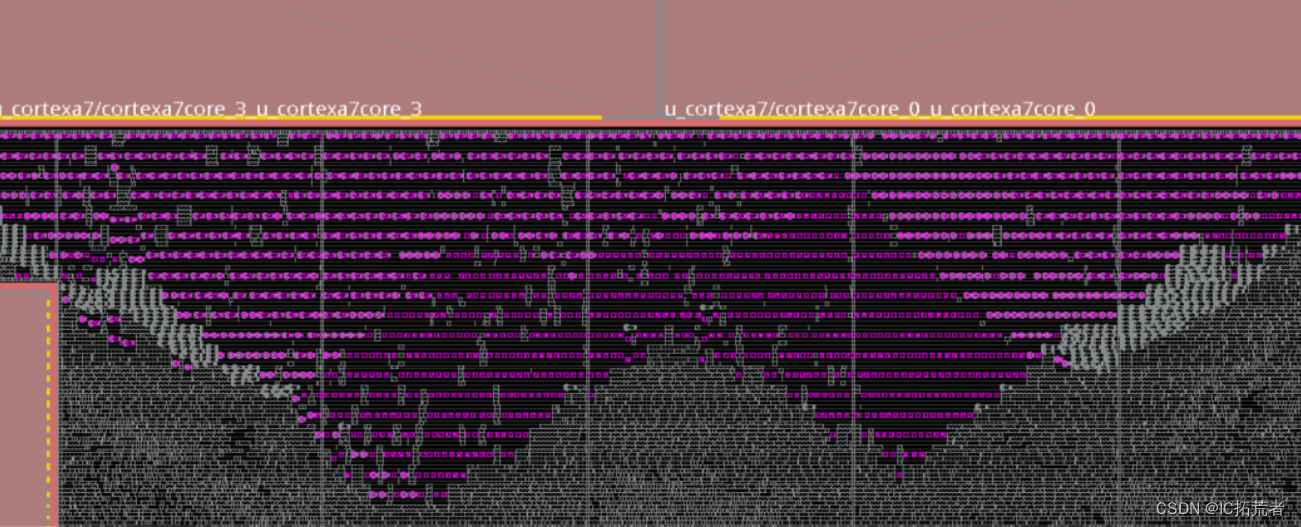

5)子模块cortexa7core,A7 top以及A7top_wrapper的floorplan工作

本项目涉及三大模块的数字IC后端实现。各个模块的floorplan需要考虑模块在顶层拼接可能出现的drc violation,尤其是base layer的DRC。

6)整体cpu子系统的powerplan规划及实现(实现模块和顶层PG的allignment)

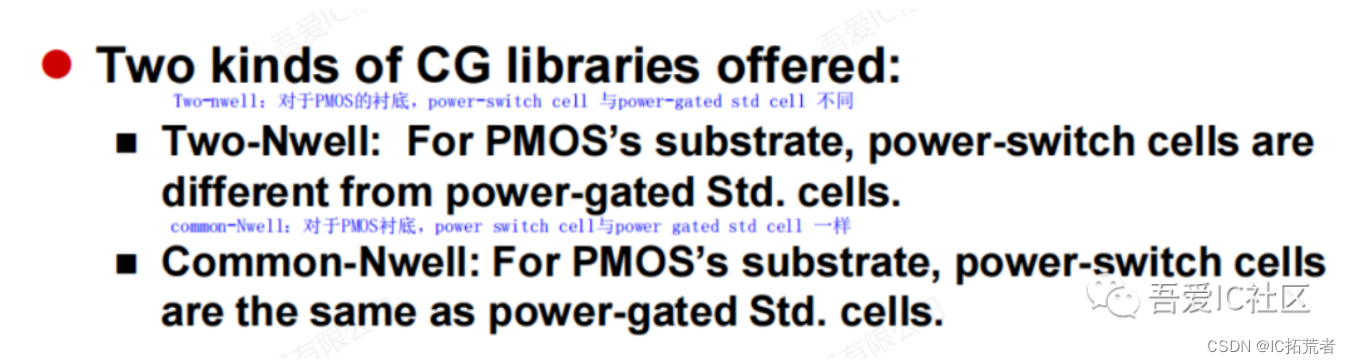

涉及power switch cell选型,power switch cell Nsleep信号串链等。比如power switch cell到底是用HVT还是RVT?power switch cell是使用common nwell还是two nwell?

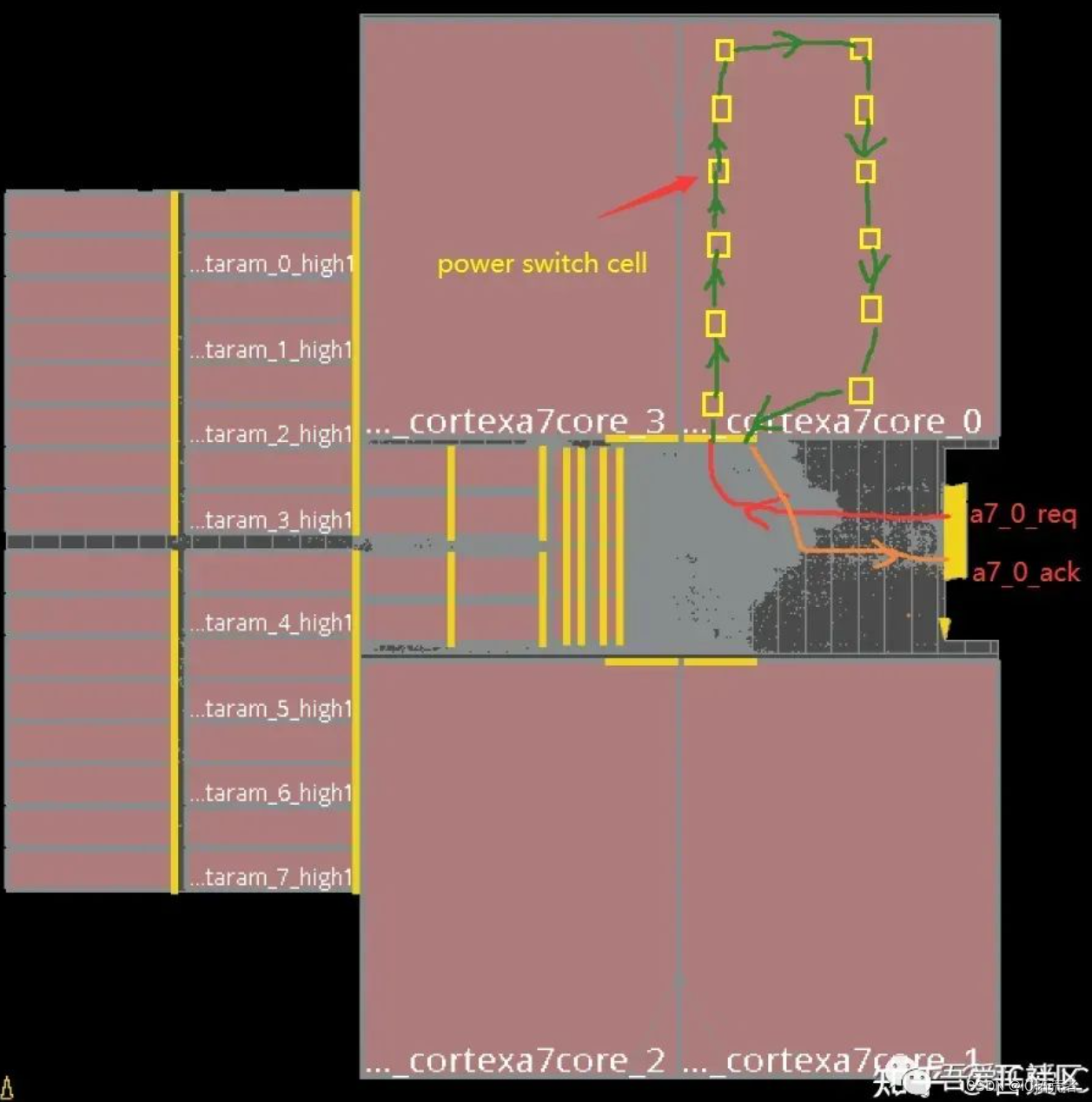

比如下图所示为咱们低功耗高级训练营项目中用到的Power Switch Cell类型,很显然它的NWELL和其他标准单元是隔断的。

【思考题】咱们这个项目能否使用common nwell的power switch cell? 如果可以,应该如何做特殊处理?

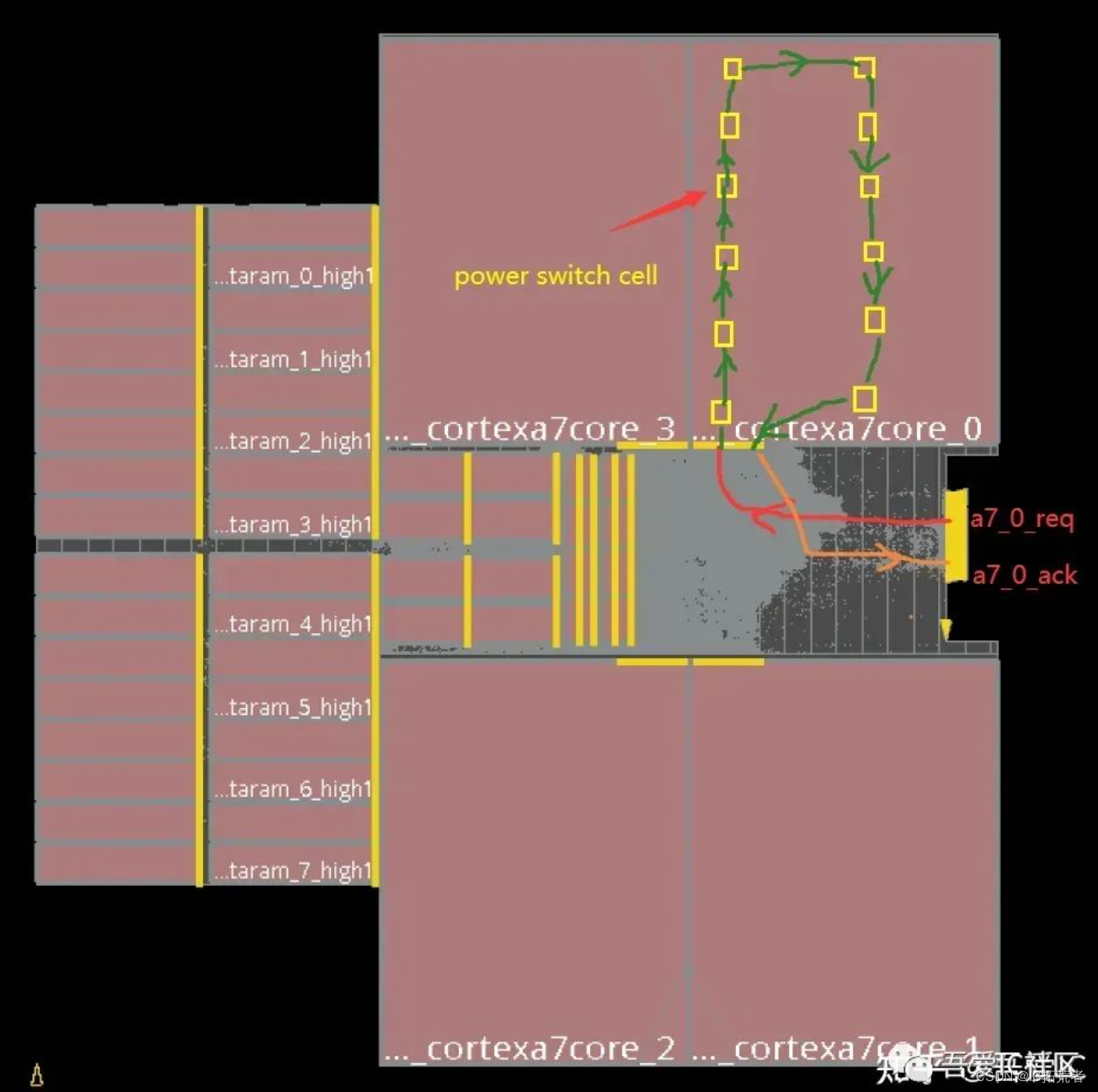

另外,咱们这个项目的四个CPU核是支持单独开关的,所以在Floorplan阶段还需要考虑好Power Switch Cell的串链问题。到底是先串Nsleep1还是Nsleep2? 这些链需要使用always on buffer吗?

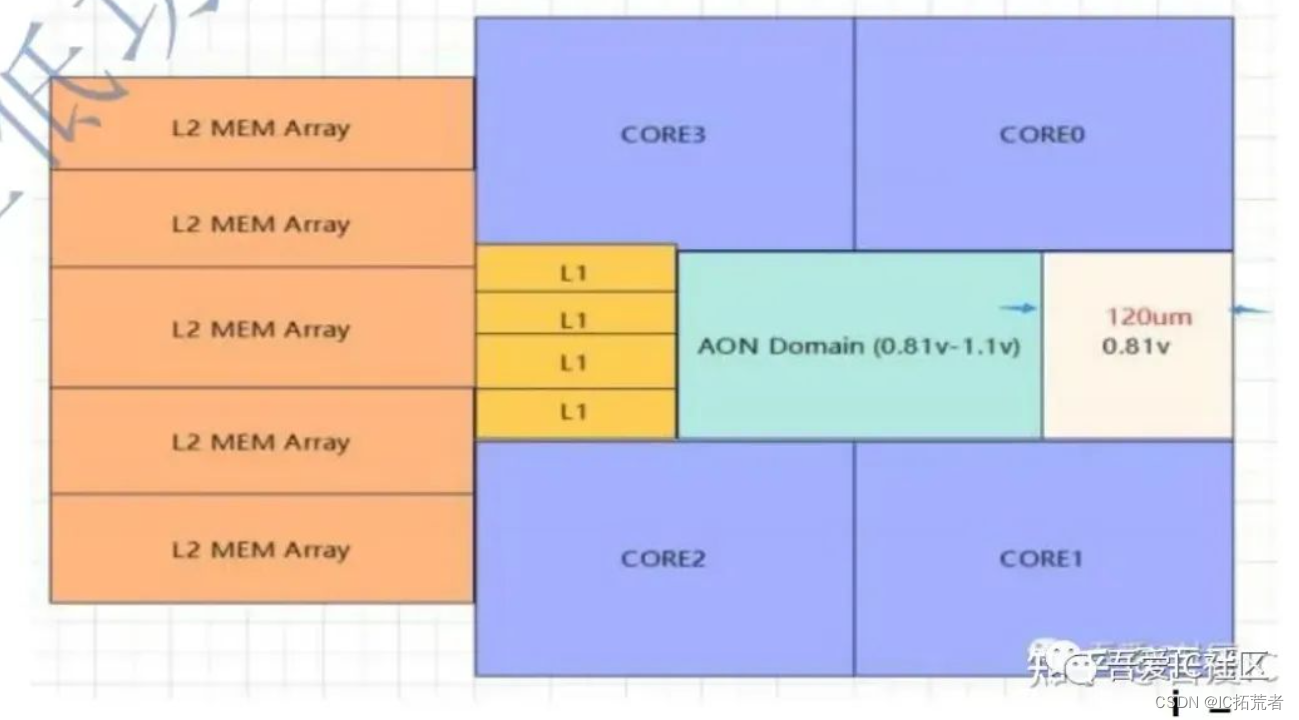

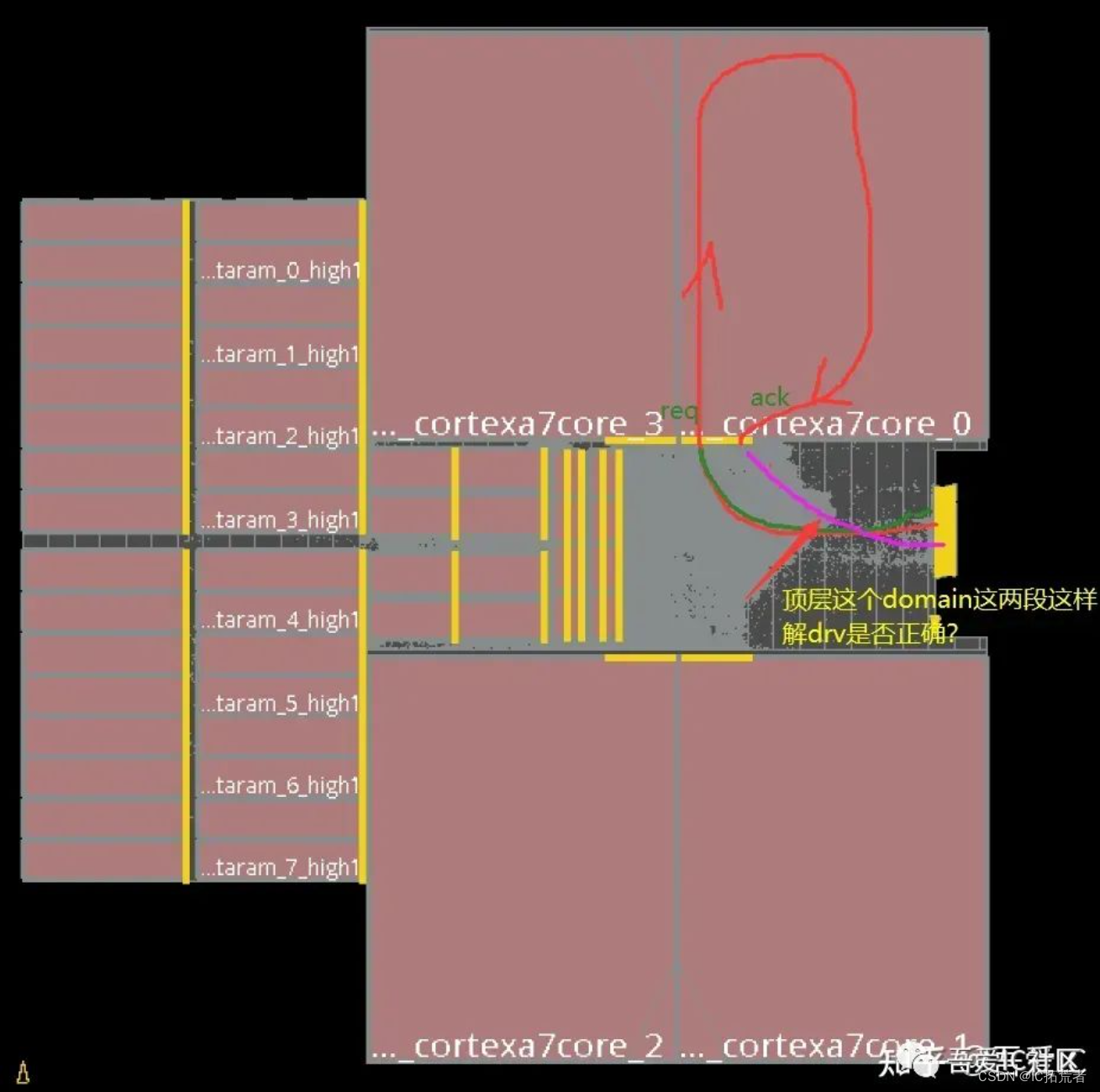

为了方便下图只画出了一条chain的连接示意图。目前这个低功耗四核A7顶层项目的串链连接关系如下图所示。设计中有a7_0_req,a7_0_ack,a7_1_req,a7_1_ack,a7_2_req,a7_2_ack,a7_3_req和a7_3_ack这些信号。这些信号可以在RTL阶段加入,也可以在后续PR阶段ECO加入。此时这些pso chain在顶层top只需要正常解max transition即可,即只需要top domain中普通的buffer即可。

如果把下图中间这层AON Domain改成另外一个需要power off的domain(这个PD相比四个CPU来说是更aon的domain),而且各个CPU支持单独开和关,那么此时这个设计的req和ack信号都有哪些?这些power switch cell的chain应该如何来连接呢?

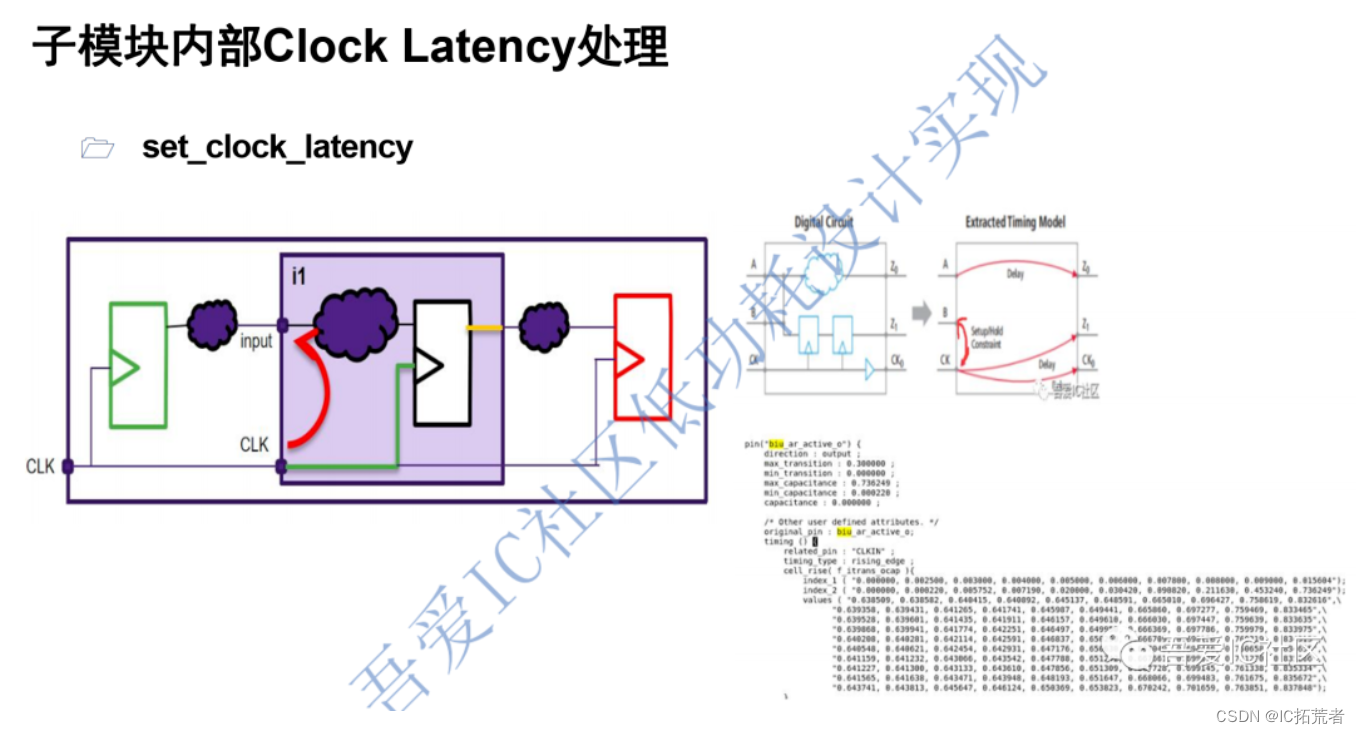

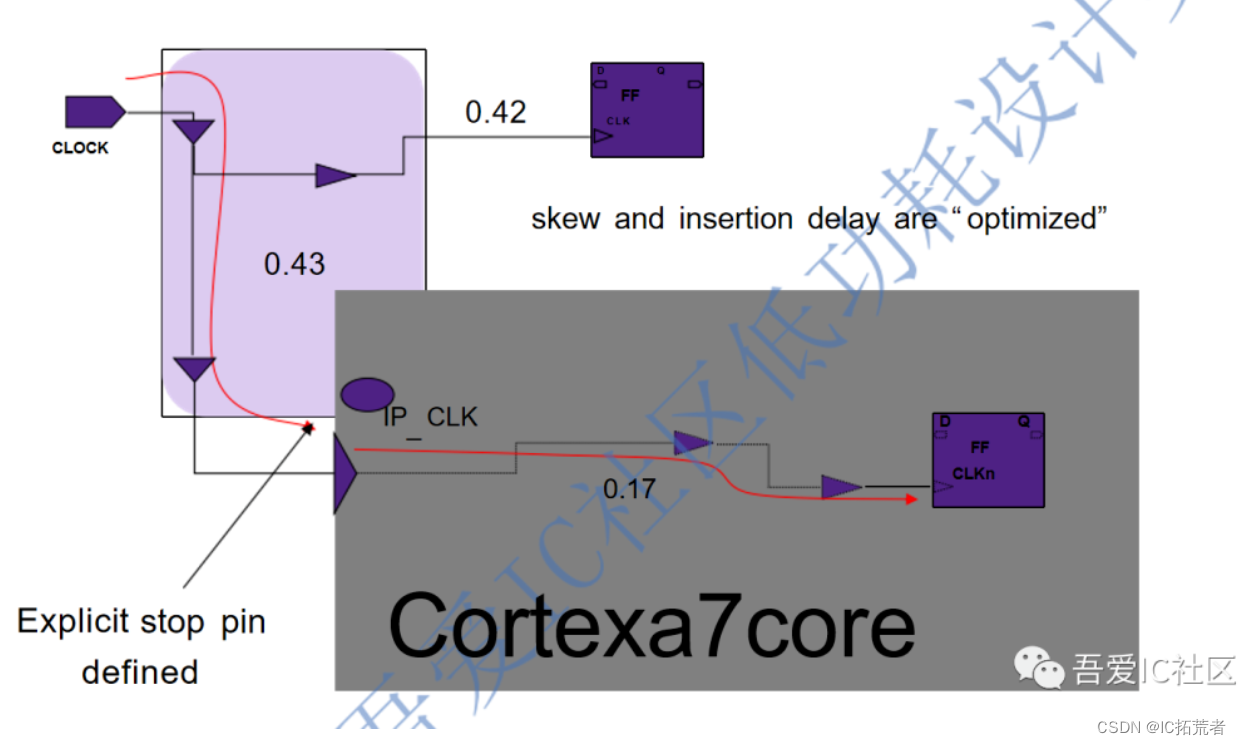

7)根据子模块cortexa7core,A7 top的post-Route ETM分别设置子模块的clock latency(考虑子模块内部的clock tree)

通过这部分内容的学习和实践,可以真正学会set_clock_latency的用法以及这种带子模块cortexa7core的hierarchical后端实现在placement阶段的一些不同的做法。

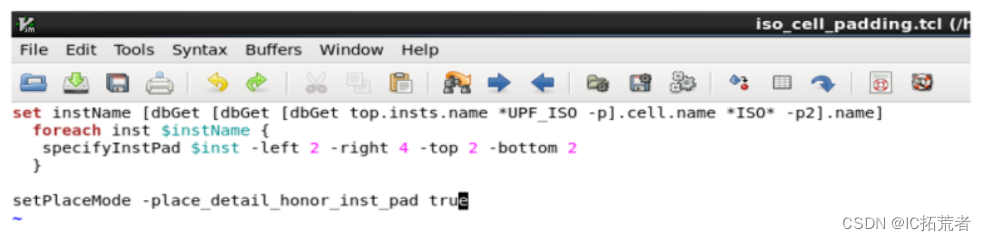

8)A7 TOP这个模块中对isolation cell进行cell padding处理以及isolation cell input电学特性检查(编写简易脚本实现)

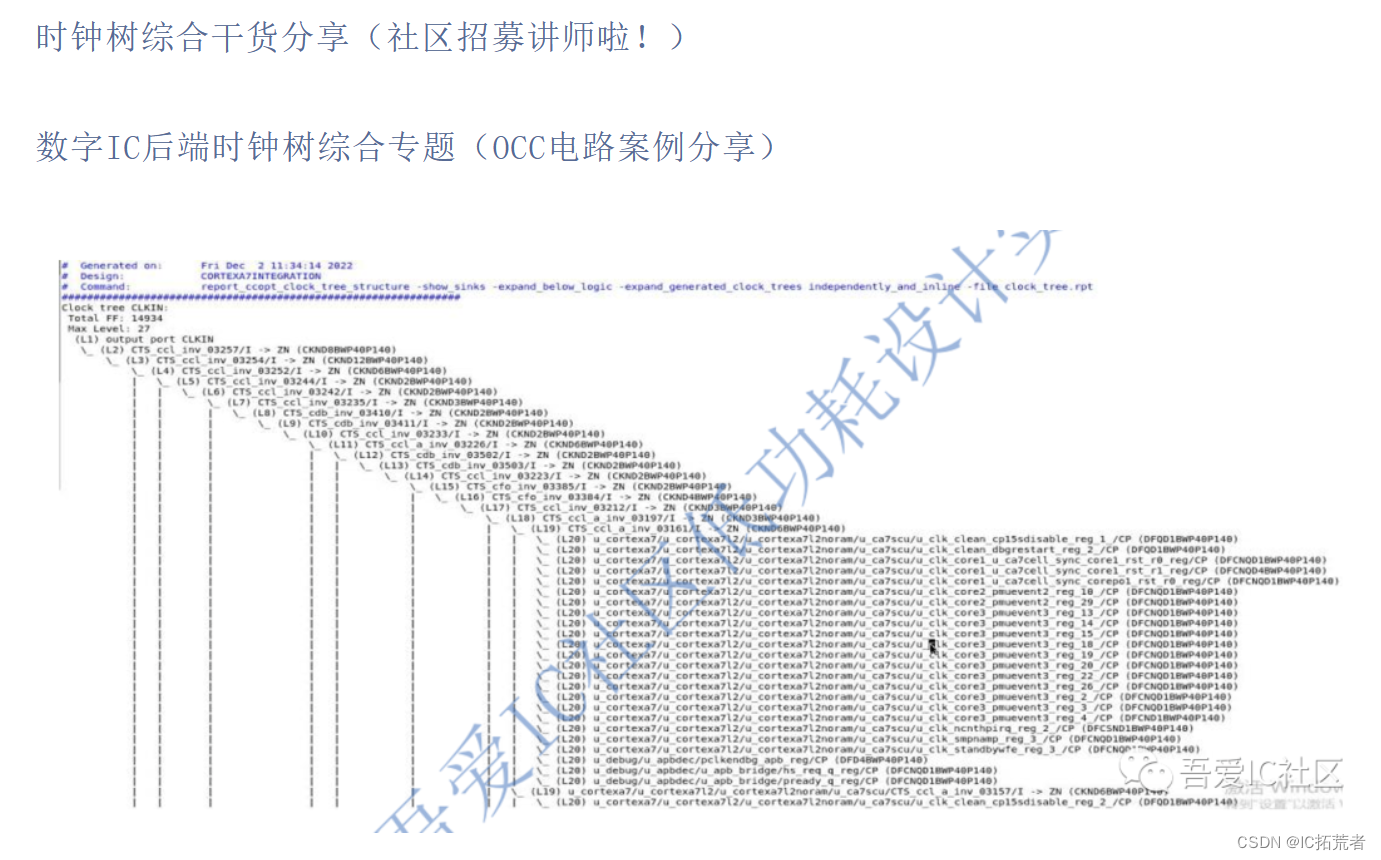

9)Cpu子系统时钟树结构trace和分析

通过这部分的理论学习和实操演练,可以熟练掌握对任何一个设计进行时钟结构的分析。

特别是彻底搞清楚对于带子模块hierarchical flow的时钟树综合做法。有了这套理论可以确保我们做出来的clock tree最短和clock skew最小。

另外,通过后续的PT时序验收还可以返回来调整子模块和顶层clock tree的insertion delay值,确保顶层寄存器和子模块cortexa7core 寄存器的balance。

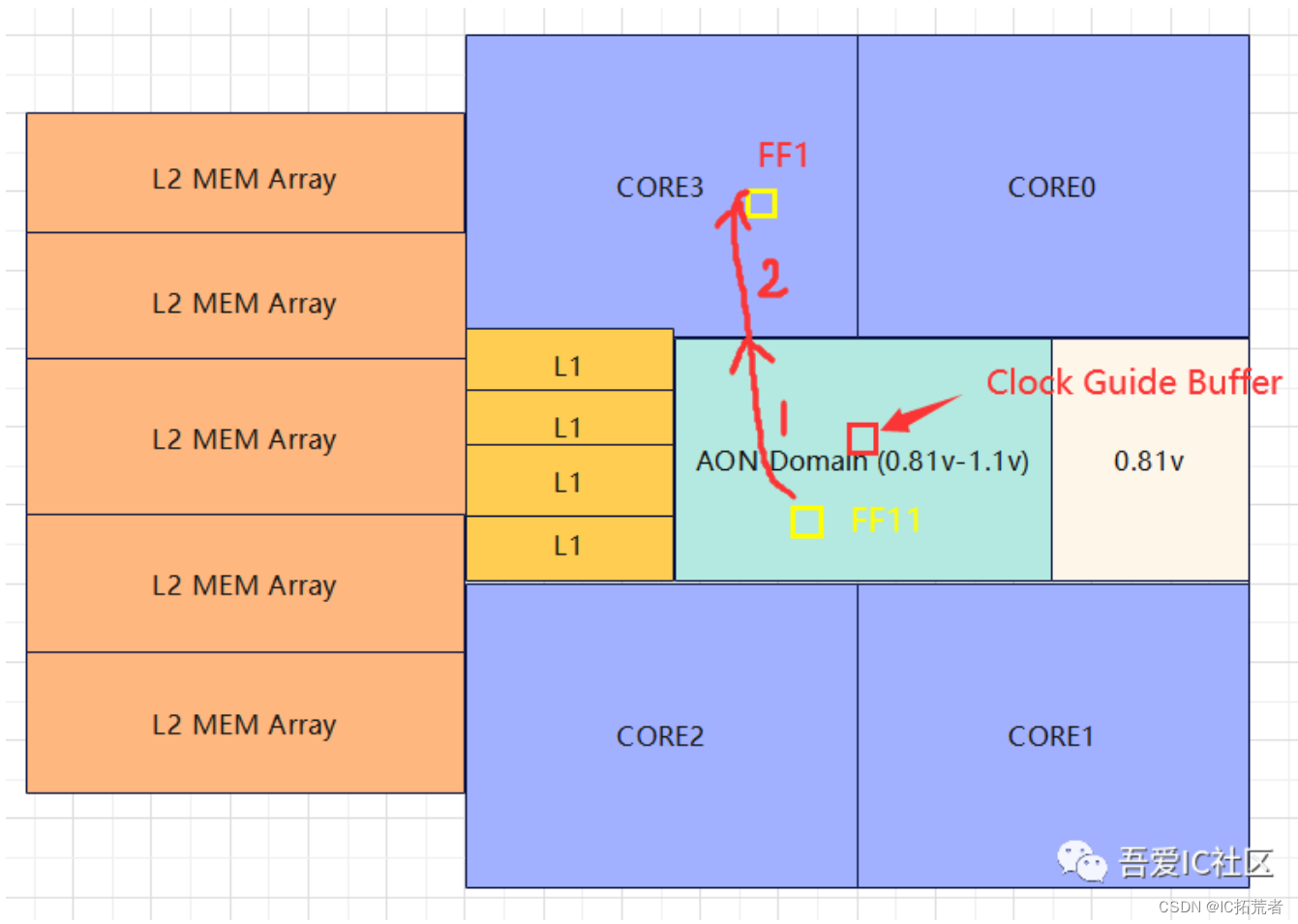

10)根据时钟结构添加guide buffer以及manual place clock tree逻辑cell来实现common clock path最长以及clock insertion delay最短

11)展示clock gating cell clone案例

因为phsicial因素,可能逻辑上common的clock gating ICG的tree会出现太早分叉的情况。此时可以通过clone clock gating的方法来避免uncommon path太长的问题。

12)熟练掌握各种Timing Optimization方法

系统全面学习数字IC后端实现中的各种时序优化方法,并将这些方法一一应用到项目实操中,通过实践的方式来深刻理解每个时序优化手段的原理和实际的效果。比如细分group path,添加region,使用High effort flow,利用不同Vth来优化时序,使用early clock flow和useful skew等手段优化时序

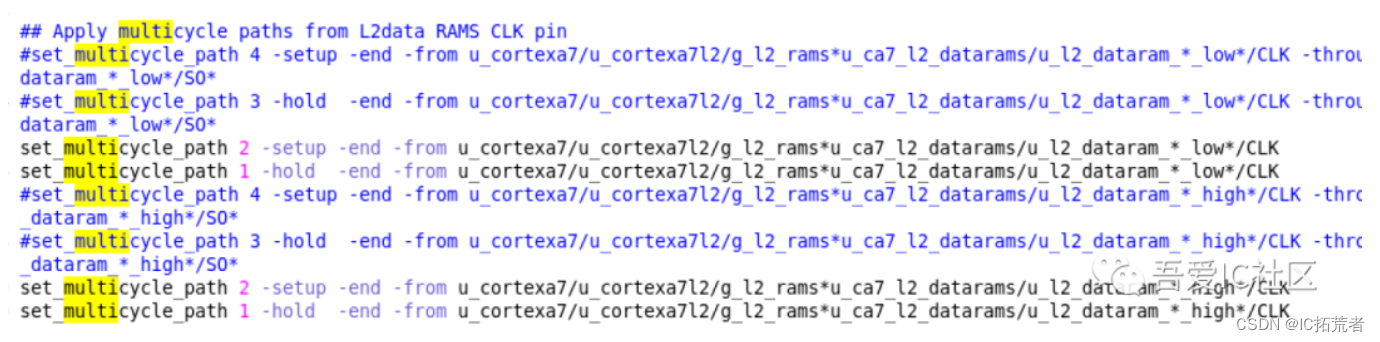

13)静态时序分析中的Timing Exception(set_false_path和set_multicycle_path)解析及应用案例

14)掌握低功耗设计实现中leakage和dynamic power的优化方法

15)对common clock trunk部分做shielding处理以减少crosstalk对Timing的影响

16)掌握子模块和顶层Top接口时序优化方法以及接口Route DRC的处理

17)掌握Fatten RC抽取流程及其checklist检查

芯片Tapeout前到底应该如何来做signoff?

18)根据Foundary Timing Signoff标准建立PT时序检查环境

19)根据Foundary Timing Signoff标准设置调整PR阶段的Timing derate值

20)熟悉掌握PT的Hierarchical和Flatten Timing检查流程

通过项目实操亲自体验Hierarchical和Flatten Timing检查的数据准备的不同,并根据PT时序检查结果进行对比两者的差异。

21)根据PT的Timing与PR Timing的差异性进行Timing一致性检查和分析

22)掌握Flatten DRC检查流程,并根据DRC结果返回Innovus进行各个子模块DRC修复

23)掌握Hierarchical &Flatten LVS检查原理及其实现技术

通过理论学习和实操练习,彻底掌握Hierarchical Flow带子模块设计的LVS检查步骤以及常见子模块和顶层拼接的LVS问题。

24)掌握根据整个CPU子系统的Dummy Insertion Flow

25)掌握带dummy的RC抽取及带Dummy的Timing检查

26)A7 top wrapper层的Level Shifter Cell的选型及其摆放

27)掌握A7 top wrapper层Level Shifter Cell Secondary PG连接方法及其roubust检查

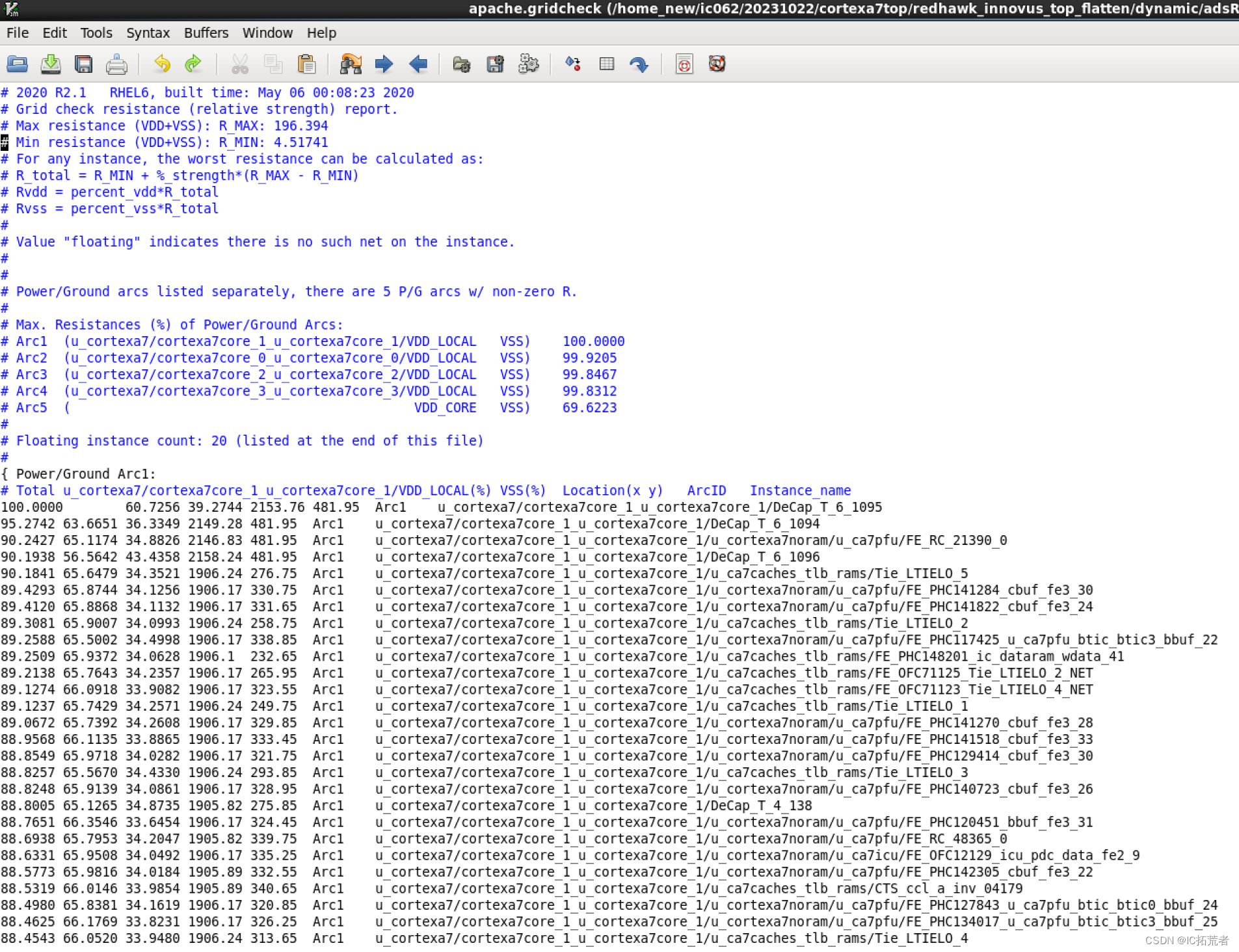

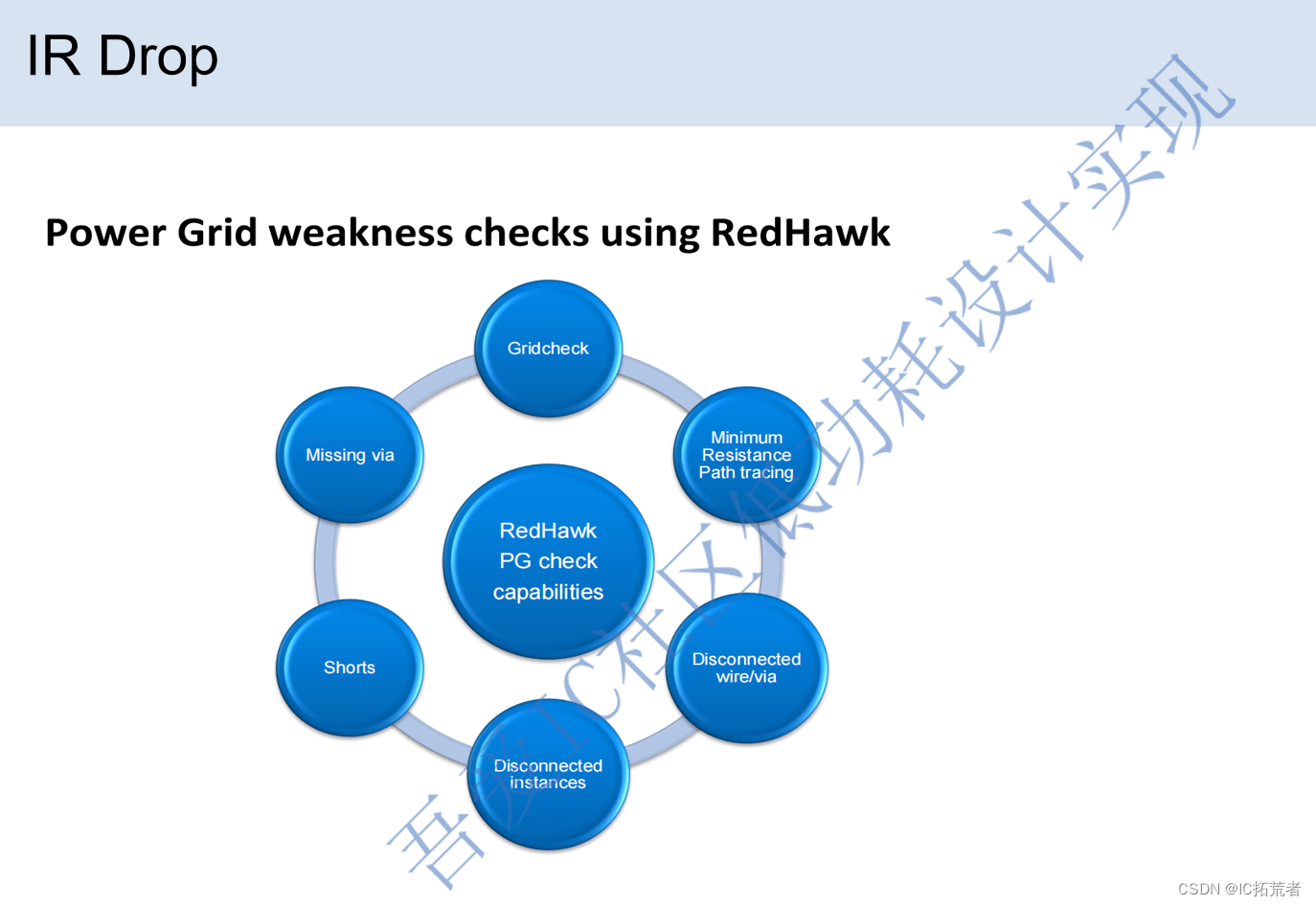

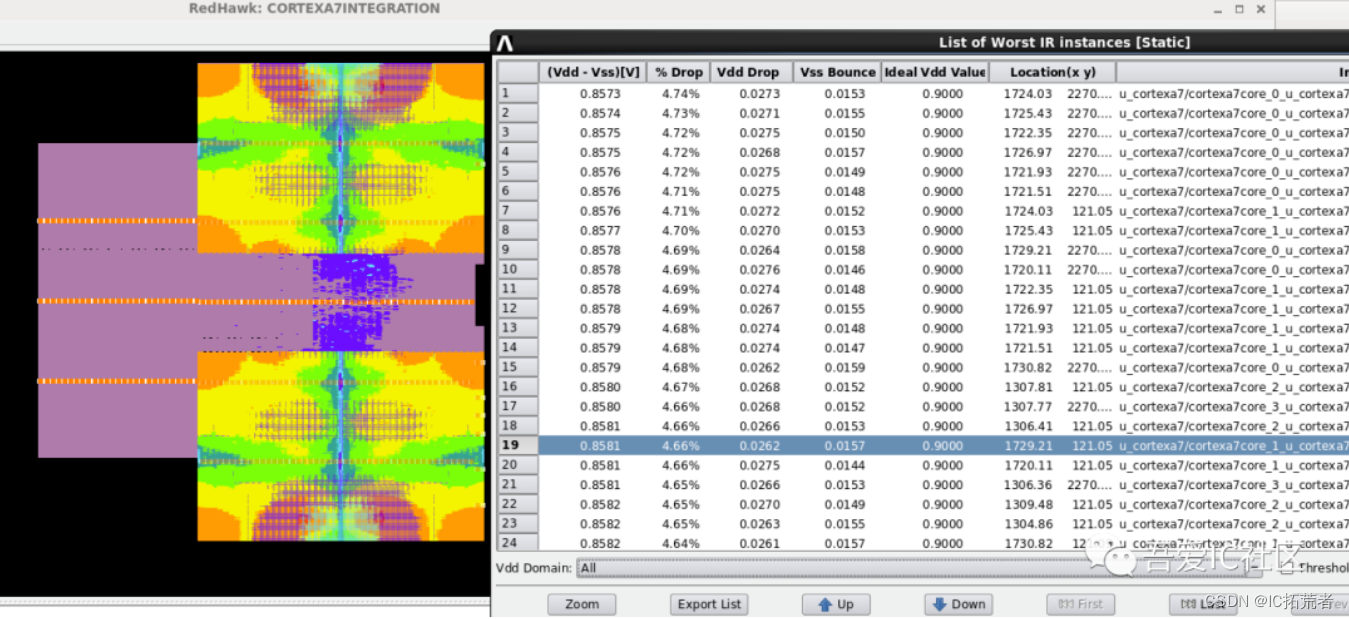

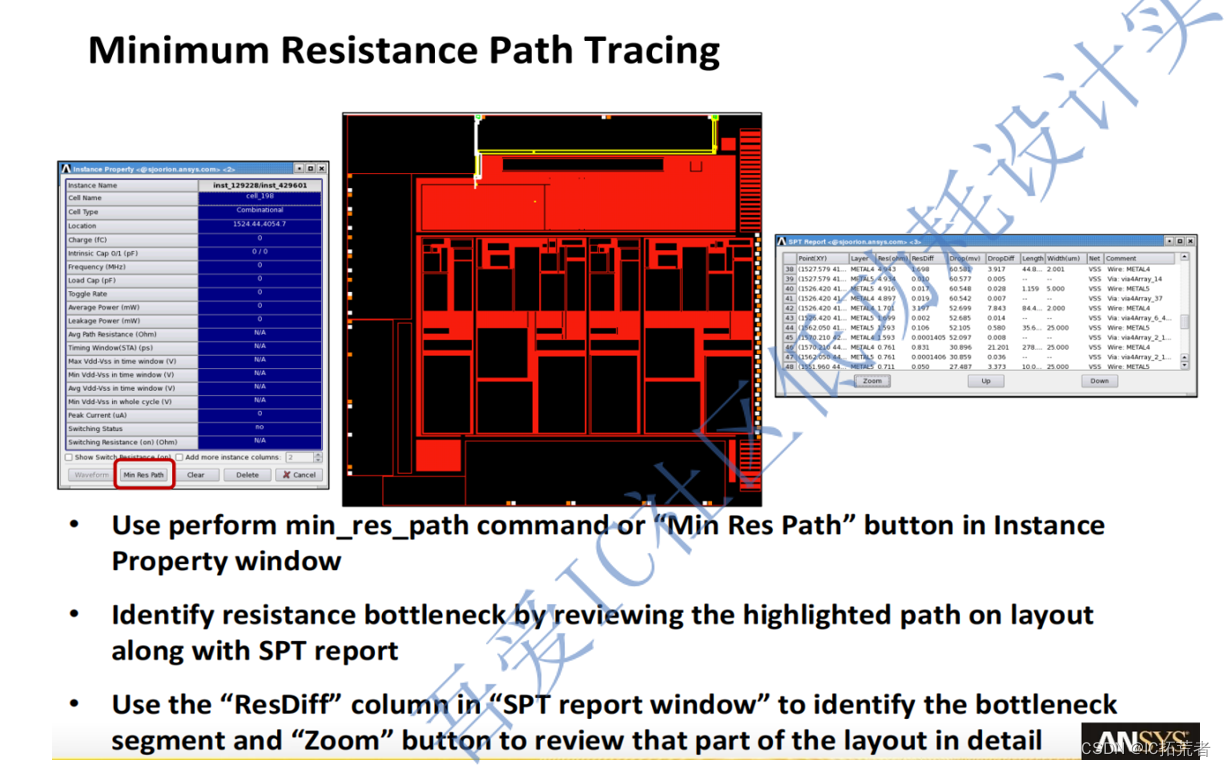

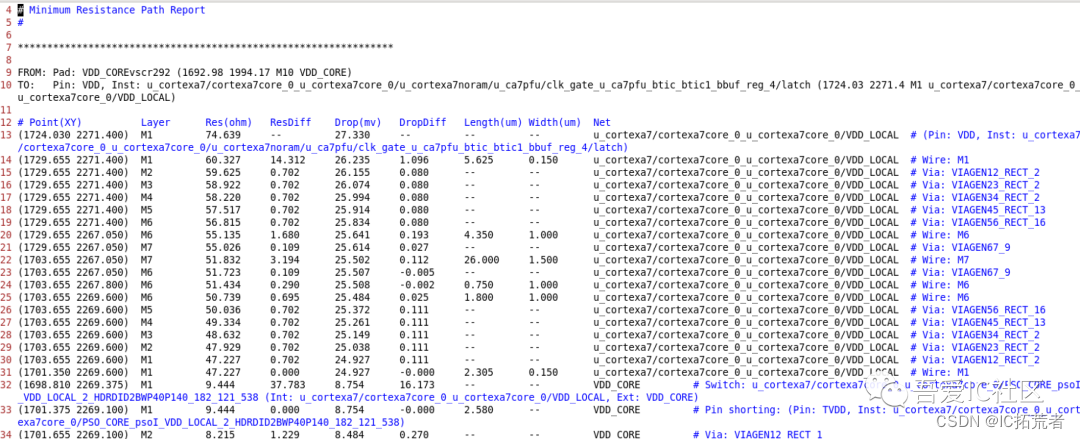

28)整个CPU子系统的IR Drop数据准备及IR Drop结果分析

通过这个项目的学习,掌握整个CPU子系统的IR Drop分析,包括静态IR Drop和动态IR Drop分析。这里面涉及子模块cortexa7core,CORTEXA7INTEGRATION和CORTEXA7INTEGRATION_TOP三大模块的IR Drop分析。各自分析ir drop后,我们还会做一个整体Flatten的IR Drop分析。

通过IR Drop的分析,我们会对工具生成的各种summary文件进行检查 ,快速定位出PG floating点,PG供电弱点,Power Switch Cell没有连接点和设计中电阻比较大的点等等。

好了,今天的内容分享就到这里。如果你想和小编有更进一步的沟通交流的机会,欢迎加入小编知识星球,让我们一起学习成长,共同进步。相信在这里能让你成就一个更完美的自己。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- [安全警报] Npm木马利用“Oscompatible“包悄然安装AnyDesk

- kubeadm 安装k8s集群后,master节点notready问题解决方案

- Python Pymysql实现数据存储

- pyDAL一个python的ORM(11) pyDAL的连接查询2

- 都是动词+ing 动名词与现在分词短语作目的状语的区别 英语语法 chatGPT学英语

- 联想电脑打开视频显示禁止相机排查

- img图片的src分别在vue2、vue3项目中如何动态赋值?

- pandas如何替换掉数据中不想要的内容

- mybatisplus实现自动创建/更新时间

- 【Vue3】2-7 : 计算属性与侦听器区别与原理(二)