5.3 Verilog 带参数例化

5.3 Verilog 带参数例化

分类?Verilog 教程

关键词: defparam,参数,例化,ram

当一个模块被另一个模块引用例化时,高层模块可以对低层模块的参数值进行改写。这样就允许在编译时将不同的参数传递给多个相同名字的模块,而不用单独为只有参数不同的多个模块再新建文件。

参数覆盖有 2 种方式:1)使用关键字 defparam,2)带参数值模块例化。

defparam 语句

可以用关键字 defparam 通过模块层次调用的方法,来改写低层次模块的参数值。

例如对一个单口地址线和数据线都是 4bit 宽度的 ram 模块的 MASK 参数进行改写:

实例

//instantiation

defparam?? ? u_ram_4x4.MASK?=?7?;

ram_4x4 ? ?u_ram_4x4

? ??(

? ? ? ? .CLK ? ?(clk),

? ? ? ? .A ? ? ?(a[4-1:0]),

? ? ? ? .D ? ? ?(d),

? ? ? ? .EN ? ??(en),

? ? ? ? .WR ? ??(wr),?? ?//1 for write and 0 for read

? ? ? ? .Q ? ? ?(q)?? ?);

ram_4x4 的模型如下:

实例

module??ram_4x4

? ??(

? ? ?input?? ? ? ? ? ? ? CLK?,

? ? ?input?[4-1:0]?? ? ? A?,

? ? ?input?[4-1:0]?? ? ? D?,

? ? ?input?? ? ? ? ? ? ? EN?,

? ? ?input?? ? ? ? ? ? ? WR?,?? ?//1 for write and 0 for read

? ? ?output?reg?[4-1:0]??Q ? ?);

?

? ??parameter?? ? ? ?MASK?=?3?;

?

? ??reg?[4-1:0]?? ? mem?[0:(1<<4)-1]?;

? ??always?@(posedge?CLK)?begin

? ? ? ??if?(EN?&&?WR)?begin

? ? ? ? ? ? mem[A]??<=?D?&?MASK;

? ? ? ??end

? ? ? ??else?if?(EN?&&?!WR)?begin

? ? ? ? ? ? Q ? ? ??<=?mem[A]?&?MASK;

? ? ? ??end

? ??end

?

endmodule

对此进行一个简单的仿真,testbench 编写如下:

实例

`timescale?1ns/1ns

?

module?test?;

? ??parameter?? ?AW?=?4?;

? ??parameter?? ?DW?=?4?;

?

? ??reg?? ? ? ? ? ? ? ? ?clk?;

? ??reg?[AW:0]?? ? ? ? ? a?;

? ??reg?[DW-1:0]?? ? ? ? d?;

? ??reg?? ? ? ? ? ? ? ? ?en?;

? ??reg?? ? ? ? ? ? ? ? ?wr?;

? ??wire?[DW-1:0]?? ? ? ?q?;

?

? ??//clock generating

? ??always?begin

? ? ? ??#15?? ? clk?= ~clk?; // 修改

? ??end

?

? ??initial?begin

? ? ? ? clk = 0 ;

? ? ? ? a ? ? ? ??=?10?;

? ? ? ? d ? ? ? ??=?2?;

? ? ? ? en ? ? ? ?=?'b0?;

? ? ? ? wr ? ? ? ?=?'b0?;

? ? ? ??repeat(10)?begin

? ? ? ? ? ??@(negedge?clk)?;

? ? ? ? ? ? en ? ??=?1'b1;

? ? ? ? ? ? a ? ? ?=?a?+?1?;

? ? ? ? ? ? wr ? ??=?1'b1?;??//write command

? ? ? ? ? ? d ? ? ?=?d?+?1?;

? ? ? ??end

? ? ? ? a ? ? ? ??=?10?;

? ? ? ??repeat(10)?begin

? ? ? ? ? ??@(negedge?clk)?;

? ? ? ? ? ? a ? ? ?=?a?+?1?;

? ? ? ? ? ? wr ? ??=?1'b0?;??//read command

? ? ? ??end

? ??end?// initial begin

?

? ??//instantiation

? ??defparam?? ? u_ram_4x4.MASK?=?7?;

? ? ram_4x4 ? ?u_ram_4x4

? ??(

? ? ? ? .CLK ? ?(clk),

? ? ? ? .A ? ? ?(a[AW-1:0]),

? ? ? ? .D ? ? ?(d),

? ? ? ? .EN ? ??(en),

? ? ? ? .WR ? ??(wr),?? ?//1 for write and 0 for read

? ? ? ? .Q ? ? ?(q)

? ? ?);

?

? ??//stop simulation

? ??initial?begin

? ? ? ??forever?begin

? ? ? ? ? ??#100;

? ? ? ? ? ??if?($time?>=?1000)??$finish?;

? ? ? ??end

? ??end

?

endmodule?// test

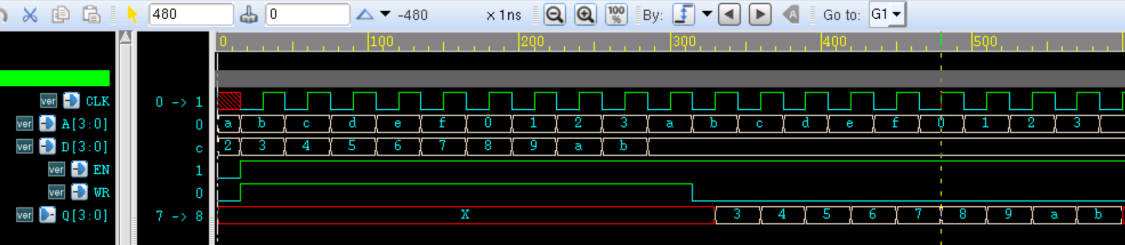

仿真结果如下:

图中黄色部分,当地址第一次为 c 时写入数据 4, 当第二次地址为 c 时读出数据为 4;可知此时 ram 行为正确,且 MASK 不为 3。 因为 ram 的 Q 端 bit2 没有被屏蔽。

当第一次地址为 1 时写入数据为 9,第二次地址为 1 时读出的数据却是 1,因为此时 MASK 为 7,ram 的 Q 端信号 bit3 被屏蔽。由此可知,MASK 参数被正确改写。

带参数模块例化

第二种方法就是例化模块时,将新的参数值写入模块例化语句,以此来改写原有 module 的参数值。

例如对一个地址和数据位宽都可变的 ram 模块进行带参数的模块例化:

实例

ram?#(.AW(4),?.DW(4))

? ? u_ram

? ??(

? ? ? ? .CLK ? ?(clk),

? ? ? ? .A ? ? ?(a[AW-1:0]),

? ? ? ? .D ? ? ?(d),

? ? ? ? .EN ? ??(en),

? ? ? ? .WR ? ??(wr),?? ?//1 for write and 0 for read

? ? ? ? .Q ? ? ?(q)

? ? ?);

ram 模型如下:

实例

module??ram

? ??#(??parameter?? ? ? AW?=?2?,

? ? ? ??parameter?? ? ? DW?=?3?)

? ??(

? ? ? ??input?? ? ? ? ? ? ? ? ? CLK?,

? ? ? ??input?[AW-1:0]?? ? ? ? ?A?,

? ? ? ??input?[DW-1:0]?? ? ? ? ?D?,

? ? ? ??input?? ? ? ? ? ? ? ? ? EN?,

? ? ? ??input?? ? ? ? ? ? ? ? ? WR?,?? ?//1 for write and 0 for read

? ? ? ??output?reg?[DW-1:0]?? ? Q

? ? ?);

?

? ??reg?[DW-1:0]?? ? ? ? mem?[0:(1<<AW)-1]?;

? ??always?@(posedge?CLK)?begin

? ? ? ??if?(EN?&&?WR)?begin

? ? ? ? ? ? mem[A]??<=?D?;

? ? ? ??end

? ? ? ??else?if?(EN?&&?!WR)?begin

? ? ? ? ? ? Q ? ? ??<=?mem[A]?;

? ? ? ??end

? ??end

?

endmodule

仿真时,只需在上一例的 testbench 中,将本次例化的模块 u_ram 覆盖掉 u_ram_4x4, 或重新添加之即可。

仿真结果如下。由图可知,ram 模块的参数 AW 与 DW 均被改写为 4, 且 ram 行为正确。

区别与建议

(1) 和模块端口实例化一样,带参数例化时,也可以不指定原有参数名字,按顺序进行参数例化,例如 u_ram 的例化可以描述为:

ram #(4, 4) u_ram (......) ;

(2) 当然,利用 defparam 也可以改写模块在端口声明时声明的参数,利用带参数例化也可以改写模块实体中声明的参数。例如 u_ram 和 u_ram_4x4 的例化分别可以描述为:

实例

defparam?? ? u_ram.AW?=?4?;

defparam?? ? u_ram.DW?=?4?;

ram ? u_ram(......);

ram_4x4 ?#(.MASK(7))?? ?u_ram_4x4(......);

(3) 那能不能混合使用这两种模块参数改写的方式呢?当然能!前提是所有参数都是模块在端口声明时声明的参数或参数都是模块实体中声明的参数,例如 u_ram 的声明还可以表示为(模块实体中参数可自行实验验证):

实例

defparam?? ? u_ram.AW?=?4?;

ram?#(.DW(4))?u_ram?(......);??//也只有我这么无聊才会实验这种写法

(4) 那如果一个模块中既有在模块在端口声明时声明的参数,又有在模块实体中声明的参数,那这两种参数还能同时改写么?例如在 ram 模块中加入 MASK 参数,模型如下:

实例

module??ram

? ??#(??parameter?? ? ? AW?=?2?,

? ? ? ??parameter?? ? ? DW?=?3?)

? ??(

? ? ? ??input?? ? ? ? ? ? ? ? ? CLK?,

? ? ? ??input?[AW-1:0]?? ? ? ? ?A?,

? ? ? ??input?[DW-1:0]?? ? ? ? ?D?,

? ? ? ??input?? ? ? ? ? ? ? ? ? EN?,

? ? ? ??input?? ? ? ? ? ? ? ? ? WR?,?? ?//1 for write and 0 for read

? ? ? ??output?reg?[DW-1:0]?? ? Q ? ?);

?

? ??parameter?? ? ? ? ? ?MASK?=?3?;

?

? ??reg?[DW-1:0]?? ? ? ? mem?[0:(1<<AW)-1]?;

? ??always?@(posedge?CLK)?begin

? ? ? ??if?(EN?&&?WR)?begin

? ? ? ? ? ? mem[A]??<=?D?;

? ? ? ??end

? ? ? ??else?if?(EN?&&?!WR)?begin

? ? ? ? ? ? Q ? ? ??<=?mem[A]?;

? ? ? ??end

? ??end

?

endmodule

此时再用 defparam 改写参数 MASK 值时,编译报 Error:

实例

//都采用defparam时会报Error

defparam?? ? u_ram.AW?=?4?;

defparam?? ? u_ram.DW?=?4?;

defparam?? ? u_ram.MASK?=?7?;

ram ? u_ram ?(......);

?

//模块实体中parameter用defparam改写也会报Error

defparam?? ? u_ram.MASK?=?7?;

ram?#(.AW(4),?.DW(4))?? u_ram?(......);

重点来了!!!如果你用带参数模块例化的方法去改写参数 MASK 的值,编译不会报错,MASK 也将被成功改写!

ram #(.AW(4), .DW(4), .MASK(7)) u_ram (......);

可能的解释为,在编译器看来,如果有模块在端口声明时的参数,那么实体中的参数将视为 localparam 类型,使用 defparam 将不能改写模块实体中声明的参数。

也可能和编译器有关系,大家也可以在其他编译器上实验。

(5)建议,对已有模块进行例化并将其相关参数进行改写时,不要采用 defparam 的方法。除了上述缺点外,defparam 一般也不可综合。

(6)而且建议,模块在编写时,如果预知将被例化且有需要改写的参数,都将这些参数写入到模块端口声明之前的地方(用关键字井号?#?表示)。这样的代码格式不仅有很好的可读性,而且方便调试。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 【论文精读】A Survey on Large Language Model based Autonomous Agents

- CSS 伪类函数 :is() 和 :where()

- 计算机毕业设计------企业ERP报销管理系统

- [OpenWrt]RAX3000一根线实现上网和看IPTV

- 获取 Linux 系统中所有网络命名空间的路由表

- Ubuntu系统入门指南:基础操作和使用

- 开源知识库zyplayer-doc部署指南

- 代码随想录day31 贪心算法初探

- Spring boot:3.X + Security OAuth2 自定义登录页面、登出后跳转到登录页

- 最牛量子处理器Heron亮相,IBM让量子计算不再空谈理论