硅像素传感器文献调研(六)

写在前面:

感叹一下前人的智慧,保护环结构?保护环——场限制环?怎么发展着还改名字了哈哈哈哈哈

发现一个领域的文章是读得越多越好读了,知识都是那些。

发现大家的引言写的都很像,背后似乎是有一种套路在的。

1983年——带场限制环的平面器件的阻塞能力

?0.摘要

介绍了场限环平面器件击穿电压的研究结果。采用有限差分法求解二维泊松方程。对具有多个场环的器件的最佳环间距问题以及表面电荷对阻挡能力的影响进行了广泛的研究。讨论了环间距、环宽度、掺杂梯度和表面电荷密度对器件性能的影响。本文提出了一个简化计算的分析模型,用以说明场环器件的主要特性。此外,显示EBIC测量的一些实验结果。

1.引言

平面pn结的击穿电压由于结的曲率和表面电荷的影响而下降。Kao和Wolley [1]指出,同心环结(图1)可以提高平面结的击穿电压。Matsushita和Hayashi[2]在衬底的顶部和底部使用场限制环,以实现甚至高于体击穿电压的击穿电压。

Adler等人[3]提出了第一个具有一个场限制环的器件的二维数值分析,他开发了一种算法来在泊松方程的解中引入和去除浮动电位区域。Sonntag等人[4]在击穿电压为5 kV的高压晶闸管中应用了场限环。Jaecklin[5]研究了高达4 kV的场环器件。Yasuda和Yonezawa[7]最近报道了具有一个场限制环的平面p+n-n+器件的结果。

到目前为止发表的数值研究仅限于只有一个场限制环的设备。Adler[3]的结果表明,具有一个最佳放置环的器件的最大击穿电压是归一化曲率半径的函数。在我们的论文中,对具有多个场环的器件进行了数值研究,以确定优化阻塞能力的基本方面。在大多数计算中,只考虑了两个环,因为发现特征关系已经可以识别。

随着环数量的增加,场环器件的优化变得非常广泛。因此,一个简单的分析模型推导出的主要特征,并给出近似值的数值计算。

制造具有两个场环的pn二极管。最后给出了一些有趣的EBIC测量实验结果。

图1 平面器件和单场限环的对应结构

2.器件结构

图2显示了数值计算中研究的pn二极管的器件结构。在所有p+区中假定相同的掺杂分布。杂质分布近似为指数分布。

其中N(r)是净杂质浓度,ND是衬底杂质浓度,dj是结深,λ是距离参数,r是空间坐标。

图2 数值计算中使用的p+n场环结构

此外,假设p区边缘处的横向扩散深度等于垂直结深度dj。因此,曲率半径等于dj。环间距dR是在扩散的p区之间的表面处的均匀n区的宽度。半导体表面由固定的表面电荷密度Ns来考虑。阻断电压施加在阴极,而阳极保持在零电压。计算中使用的数据在各图的图例中给出。

3.数值方法

数值计算的基础是求解二维泊松方程的程序系统

在区域AEFG(见图2)中,相对介电常数Er在硅ABCD中设置为Er = 11.7,在所有计算结构的周围区域中设置为Er = 1。N(x,y)是半导体体中的净掺杂浓度,并且在半导体外部被设置为零。该解决方案是使用有限差分法完成的,同时将解决方案限制在零和施加电压之间(更详细的描述见[3])。外部边界由以下边界条件考虑。沿着对称线AD,电场的x分量Ex由于该边界处的平面场分布的均匀性而为零。沿着AB的电势由阴极的固定电势Vc给出。B和C之间的平面器件的表面总是具有阴极的电势。因此,沿着BEF的电势被设置为等于Vc。从H到F,假设V线性增加。由于在计算中使用的到半导体表面的大距离,沿该边界的电势不影响空间电荷区域中的解。

求解泊松方程的问题是将浮置电势区域包括在场环区域中。在[3]中描述了从物理考虑导出的主要方法。该算法直接应用于具有多个场环的设备是非常广泛的,并且包含不稳定的风险。从物理角度来看,可达到的准确度受到环边缘网格线密度的限制,降低了低压点LVP的可能位置(参见[3])。因此,采用了修改后的程序。网格节点处的电势按所示顺序(图2)沿着每条网格线计算.每个p区域中的第一个点被视为LVP,并且在该特定迭代步骤期间,其势被用作局部参考。所选择的点位于表面下方,并且是对表面电荷密度的感兴趣范围的折衷。用一个场限环作比较计算,与文献[3]的结果符合得很好。

根据场分布,雪崩击穿电压UBR通过使用Van Overstraeten和de Man[6]的电离系数计算倍增因子来确定。根据空穴引发倍增的方程计算倍增因子Mr。

等于1的faip值用作击穿的标准。

4.数值结果

所提出的结果是一个总结的数值计算调查以下器件参数的影响:环距离,环宽度,掺杂梯度和表面电荷密度。以下各节将指出其主要特点。

4.1?场环的最佳位置

具有平坦的掺杂分布,30 μ m深,和衬底掺杂的10 14cm -3的结构进行了优化,为1000 V的固定电压。阳极和环形区域中的最大电场的相等值的条件作为优化的标准。

平面器件的最大场计算为263 kV/cm。

如果仅施加一个环,则最佳环间距被确定为15 μ m。对于该环距离,最大电场降低至205 kV/cm。

使用两个环给出了195 kV/cm的最大场,其中第一环的最佳环间距为9 μ m,第二环的最佳环间距为15 μ m。通过对最佳环间距的比较,得出了第二环间距等于单环间距的显著结论。第5节对这个结果作了一般性的讨论.

图3表示具有两个环的器件的100 V步长的等势线。冶金结处用虚线表示。在没有场限制环的情况下,沿沿着冶金结的电势从均匀阳极区域中的约150 V增加到表面处的300 V。该电位通过第一个环降低到100 V。在平面阳极区的边缘附近接触p区的200 V线被迫围绕第一环。图4表示具有仅一个场限制环和15 μ m的环间隔的相应结构的场分布。人们可以识别阳极、环和阴极的中性部分。该分布显示出两个极大值,一个在位于半导体体中的阳极区域中,一个在位于表面处的环中。

从这些结果可以得出以下一般性结论:

环之间的相等距离不会导致最佳场分布。

优化设计的结构的环间距从内环到外环的方向上增加。

图3?具有两个场环的结构的等位线.Vc=1000V,ΔV=100V

图4 一个场环结构的场分布

4.2?掺杂分布对最佳环间距的影响

最佳环间距是曲率半径、衬底掺杂、掺杂梯度和表面电荷密度的函数。Adler等人研究了前两个参数的影响[3]。他们发现,一个最佳放置的场环的UBR/UBRmax比值是归一化曲率半径的函数。然而,相应的最优环间隔取决于掺杂分布的陡度。

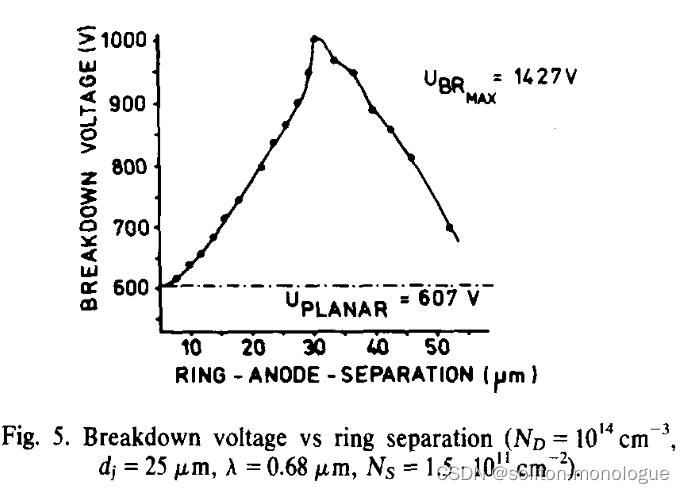

图5示出了作为环形阳极间距的函数的击穿电压UBR。在这种情况下,环结构具有1014cm-3的衬底掺杂和25 μ m的扩散深度。如果环太靠近阳极,则击穿将发生在环区域中。离阳极太远的环不会降低阳极区域中的增强场。对于这两种情况,击穿电压将接近平面击穿电压。最佳环间距为30 μ m,或者为了比较的目的用扩散深度dR = 1.2 dj表示。

在4.1节中讨论的结构表明最佳环间距仅为15 μ m或dR = 0.5 dj。这种结果是由掺杂分布的不同梯度引起的。第4.1节中环形结构的平坦掺杂分布产生了空间电荷层向p区的相当大的延伸。为了获得同样的最佳效果,场环必须位于更靠近阳极的位置。

图5 击穿电压和环间距的关系

4.3?表面电荷对阻隔性能的影响

表面电荷在器件表面形成积累层,对器件的阻挡能力有很大的影响。对腐蚀或热氧化硅样品的实验结果表明,存在正表面电荷。图6表示在不同的正表面电荷密度下具有两个场限制环的器件的等势线。在表面处的耗尽区的收缩导致第一环的场环电压从166 V增加到443 V。虽然第二个环在较高的Ns值失去了它的有效性,几个场环结构是较少依赖于表面效应。图7证明了多个环在表面电荷影响方面的优势,图7示出了平面器件和具有两个环的场环结构的击穿电压和最大场。没有场环的平面器件的击穿电压随着密度Ns的增加而降低。相比之下,具有两个环的器件的击穿电压示出了随着Ns的略微增加,随后在较高的Ns值处接近平面器件的击穿电压的强烈衰减。这种效应是由于最大场从第二环转移到第一环。带有场环的器件带来了击穿电压的明显增加,在Ns=2.5e11cm-2时高达1500V.该器件在有限的范围内对表面电荷的变化不敏感。

图6.对于不同的Ns值,在V = 1000 V处具有2个环的结构的以ΔV = 100 V为步长的等势线:(a)Ns = 0,(B)Ns=5e11(c)Ns = 1e12cm2

图7 击穿电压和最大电场与表面电荷密度的关系。(对于具有两个环的平面场环器件)

4.4?场环宽度对场分布的影响

除了环间距之外,还可能通过场环宽度影响场分布。数值结果表明,当环的均匀部分宽度小于3 · dj时,最大场有明显的变化。宽场环改善了前一区域中最大场的减小,并且适用于内环,而窄环防止了其自身区域中的场增强,并且应用于外环。

4.5?具有相等环间距的器件

几个实验研究的阻断能力的功率器件与场环应用相等的环间距[4,5]。图8显示了由[5]制造的具有三个环和大约4 kV击穿电压的结构的场分布。计算的结构具有65 μ m深的平坦扩散分布和衬底掺杂的1.8e13cm-3。等环距优化的局限可以在图8中看到。最大场发生在阳极和外环中,而内环未被完全利用。为了实现固定的击穿电压,与根据第4.1节的可变环间隔相比,需要更多的环。

图8 3个场环结构的场分布(均匀环间距)

5.分析模型

为了描述场环器件的主要特性,并使最佳环间距的近似值,导出了一个简单的模型(见附录)。

该模型将二维Poisson方程简化为具有已知解的两个耦合一维方程组。图9示出了下面的一维场分布的位置和形式。在均匀区域中,使用平面结构的关系。曲率半径的影响牵连在半导体表面的场分布的衬底掺杂的正式增加。环之间的电压降由环的位置决定。当所有表面场分布满足击穿条件时,环存在最佳位置

该模型产生归一化击穿电压u和归一化环间隔1作为归一化曲率半径g和环数目n的函数,其中

在这些方程中,UBRmax和Wmax是平面结构的击穿电压和相应的耗尽层宽度。所需的耦合因子“η”是通过数值解的比较确定的。

图10(a)显示了在内环之间使用“η?= 0.7”计算的击穿电压,最外环使用“η= 0.5”计算的击穿电压。n =0和n =1时的曲线与Adler[3]给出的数值结果符合得很好。

图10(B)中所示的计算的归一化环间距1,1,支持在第4,1节中已经发现的结果。仅应用一个环(n = 1),曲线i = n产生所需的环间距。使用两个环(n = 2),第一个环(i = 1)的环间距为g!甚至通过曲线i= n- 1,第二环(i = 2)的间距为再次由曲线i = n确定。通常,添加新环导致主要环的移位而不改变它们的环间距。新环插入阳极。

图10 归一化击穿电压和归一化曲率半径的关系

计算还表明,最佳的环结构作为一个分压器,几乎与参数g无关。具有一个环的器件在阳极和环之间具有击穿电压的40%的电压降。具有两个环的结构对于第一环和第二环分别具有U~R的27%和30%的电压降。

所提出的模型只能在参数g的有限范围内使用。在较高的g值的模型产生的击穿电压高于体击穿电压。击穿发生在表面的假设不再正确,因为最大场的点在p +区域的下部。

6.实验结果

具有两个场环的器件使用硼沉积,然后通过驱入扩散来制造。这些器件对应于图7中计算的结构。将测量的击穿电压与计算的击穿电压进行比较,得到表面电荷密度Ns在1-1.5.1011cm-2的范围内。

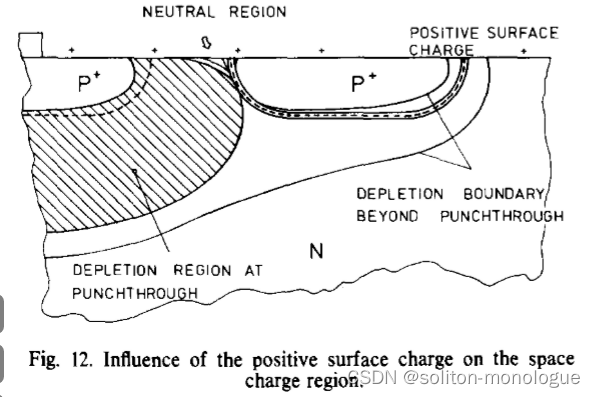

通过测量电子束感生电流(EBIC)研究了空间电荷区的扩展。图11表示该EBIC测量的示例。空间电荷层到第一和第二环的穿通分别在25和165 V的电压下发生。

如果载流子的产生发生在空间电荷区,则所有载流子都应该对感应电流有贡献。相比之下,测得的曲线显示出典型的下降。为了解释这种行为,图12可视化了穿通时的空间电荷区域。发生初始穿通的点位于表面下方。在穿通点上方的三角形准中性区域中,在该区域中产生的载流子的一部分在表面处复合,因为它们没有立即被电场提取,因此不能用于感应电流。随着电压的增加,该区域的延伸减小,并且下降变得更小。

图11 2个场环器件的EBIC特性

图12 空间电荷区的表面正电荷影响

7.结论

本工作的目的是显示具有多个场限制环的平面器件的主要特性。使用一个以上的场环,还没有对最佳环间距的研究。在大多数情况下,使用具有相等环间距的设计。由于我们的计算,一个结构与可变环间距导致一个改进的设计有关的最大击穿电压和表面电荷的影响,所开发的分析模型揭示了多环场环结构的主要特点,并简化了其优化。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 计网 - LVS 是如何直接基于 IP 层进行负载平衡调度

- vulnhub一句话木马 DC5个人学习记录

- 乳糖不耐受人群,多喝牛奶,反而降低糖尿病风险?

- Proxifier安装与激活

- 【第2讲】微信机器人 · 自动发消息

- MS2267视频放大器可Pin to Pin兼容NJM2267

- 【打卡】牛客网:BM88 判断是否为回文字符串

- 最佳实践!Apipost使用指南

- Spark原理——物理执行图

- 十大电脑屏幕监控软件超全盘点!