Verilog HDL数据类型

发布时间:2023年12月18日

1 网络型(net型)数据

????????两种驱动方式:在结构描述中将其连接到一个门元件或模块的输出端;或用assign语句对其赋值。

????????【例】分别调用Verilog HDL提供的门元件和采用assign语句设计一个二输入与非门 ? ? ?????????input?? ?a,b; ? ? ?

????????output?? ?y; ? ? ?

????????wire ? ? y; ? ? ?

????????nand?? ?my_nand(y,a,b); ? ?//调用门元件nand ? ? ?

????????assign?? ?y=!(a&&b); ?//或采用assign语句 ? ? ?

????????常用的net型数据

????????wire,tri:连线类型,可综合

????????wor,trior:具有线或特性的多重驱动连线

????????wand,triand:具有线与特性的多重驱动连线

????????tri1,tri0:上拉电阻和下拉电阻

????????supply1,supply0:电源(逻辑1)和地(逻辑0),可综合

????????trireg:具有电荷保持作用的连线,可用于电容的建模

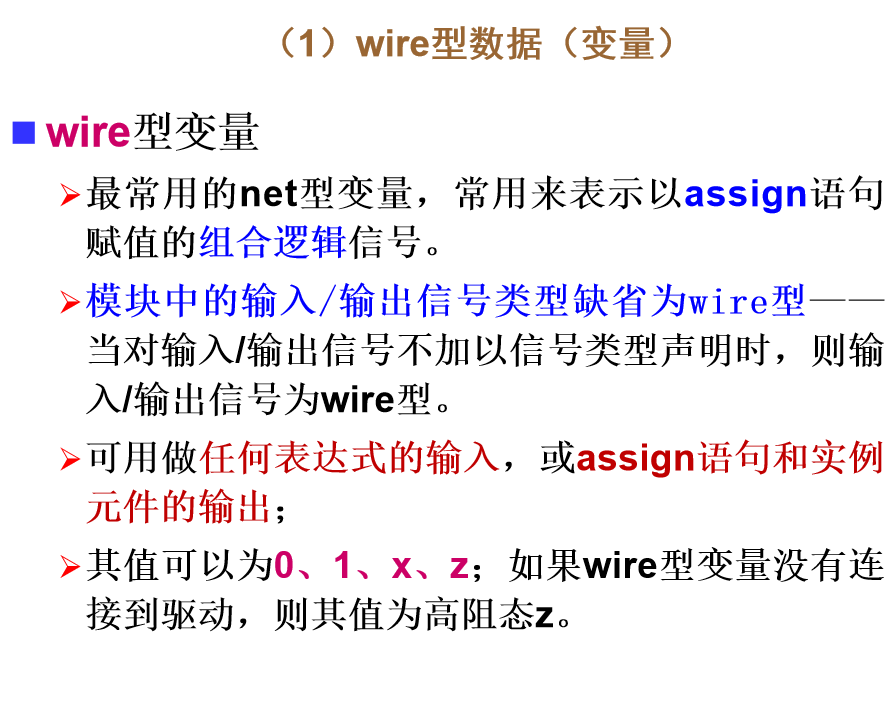

? ? ? ? (1)wire型数据(变量)

????????

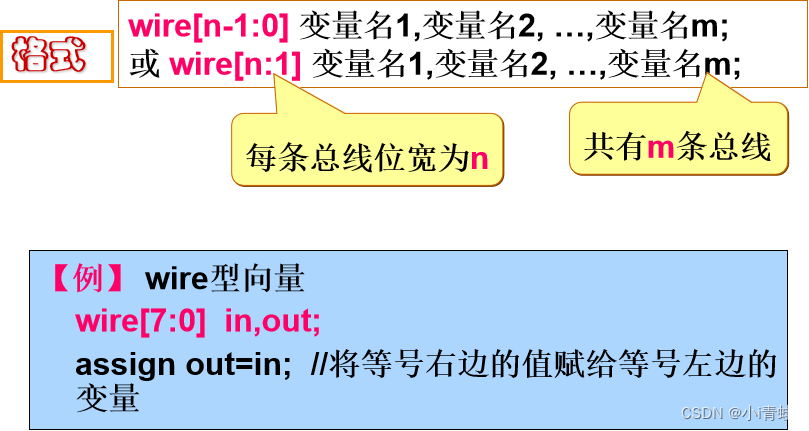

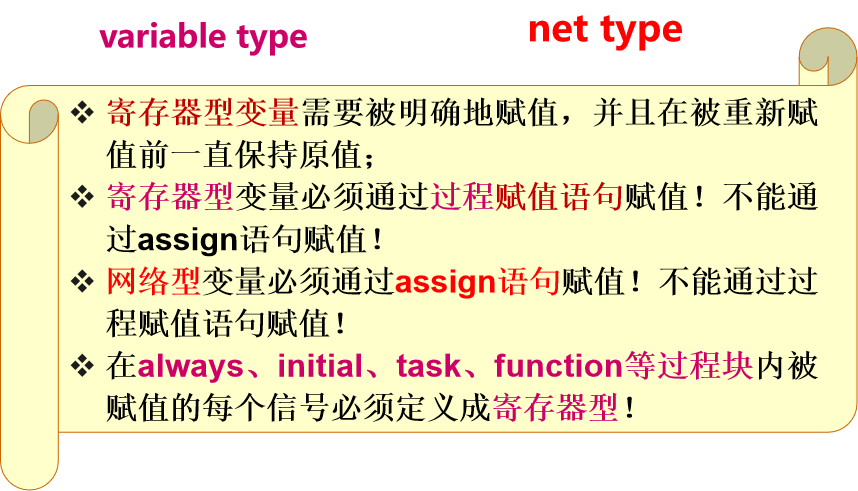

2 寄存器型

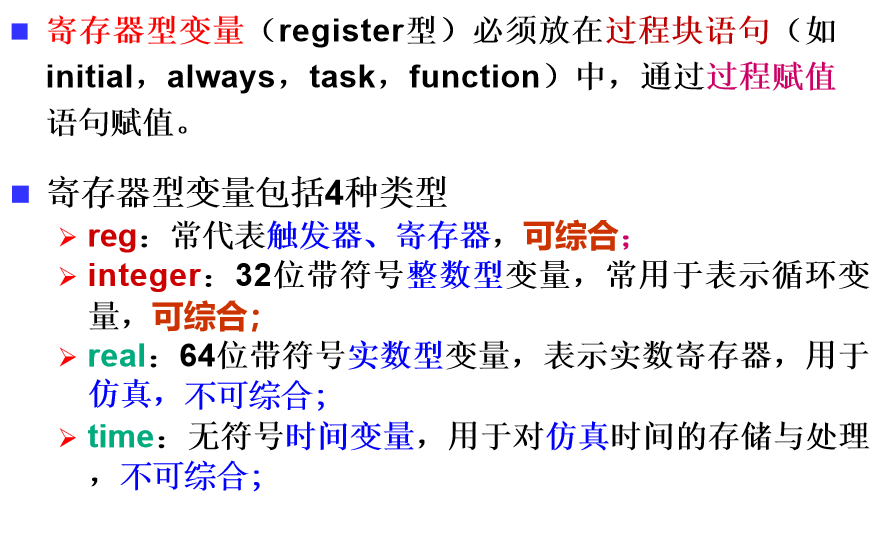

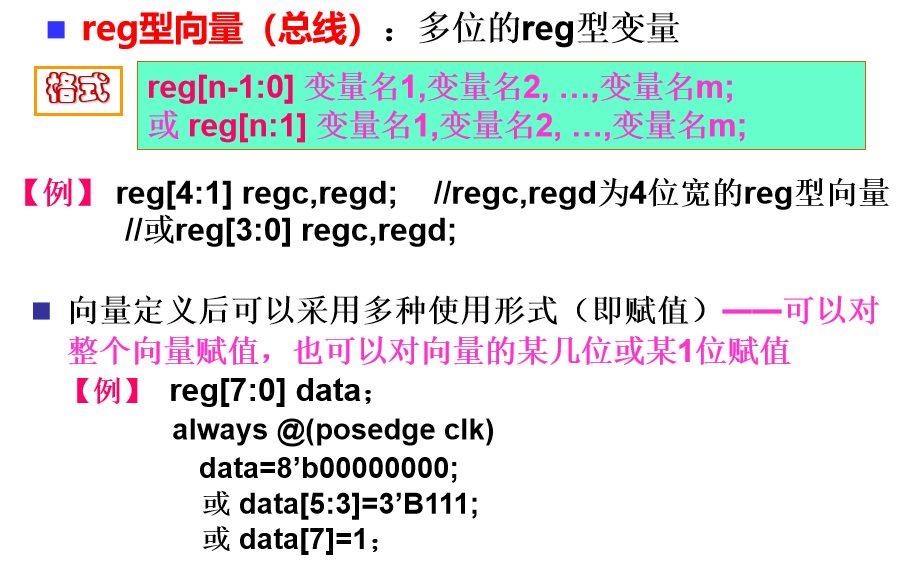

????????(1)reg型变量

????????reg型变量是最常用的寄存器型变量,常用于具体的硬件描述。是数字系统中存储元件的抽象,或者是普通的连线 。

????????(2)interger型变量

?

?

文章来源:https://blog.csdn.net/axxdxzz/article/details/134970800

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 自动化测试po模式是什么?自动化测试po分层如何实现?-附详细源码

- 21、Kubernetes核心技术 - 高可用集群搭建(kubeadm+keepalived+haproxy)

- 忘记RAG,未来是RAG-Fusion

- 项目-导波雷达物位计的基本理论

- 【Verilog】期末复习——数字逻辑电路分为哪两类?它们各自的特点是什么?

- 成本管理常用的ChatGPT通用提示词模板

- Android Selinux权限之MLS

- YOLOv5改进之OTA、SimOTA

- c# listbox 添加图标和文字

- 总420+,专业120+南京大学851信号与系统电子信息考研经验通信,电子信息