芯课堂 | 如何配置SWM系列系统时钟?

如何配置SWM系列

系统时钟?

? ? ? 华芯微特科技有限公司SWM系列芯片可通过软件配置改变时钟的速度,可以让我们的设计更加灵活,频率可选空间也更加广泛,用户可以根据自己的实际需求配置需要的系统时钟。为了让用户能够更简单的使用这一功能,下面小编将以SWM190为例,给大家展示如何配置SWM系列产品的系统时钟。

S W M 1 9 0

最大时钟频率可达

60MHz

有5个时钟源可供使用:

01.内部高频振荡器(RCHF):内部高频振荡器为片内时钟源,无需连接任何外部器件。频率为24MHz或48MHz,通过HRCCR寄存器进行切换,精度为百分之一,可提供较精确的固定频率时钟.

02.内部低频振荡器(RCLF):内部低频振荡器为片内时钟源,无需连接任何外部器件。频率为32KHz。

03.外部振荡器(XTAH):外部振荡器可接4~32MHz频率.

04.外部低频振荡器(XTAL):外部低频振荡器,支持32.768KHz时钟接入

05.PLL:支持RCHF或XTAH作为输入源

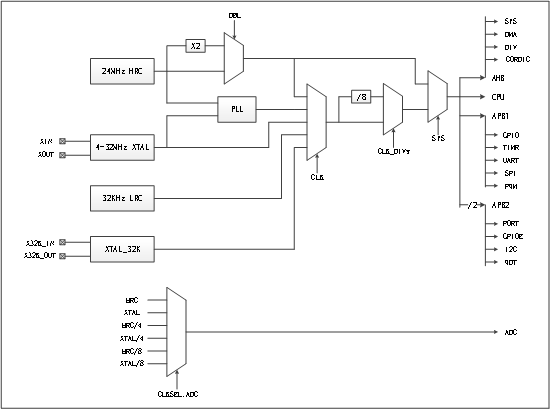

我们来看一下时钟系统框图

如图所示:

?SWM190时钟框图

S W M 1 9 0

时钟配置方法

? ? ? 在SWM190固件库中对时钟频率的选择进行了简化,原先的很多操作都在后台进行。系统给出的函数为SystemInit(void),可直接调用配置系统时钟,但在调用前还需要进行一些宏定义的设置,具体的设置在system_SWM190.c文件中。

如下:

/* 系统时钟设定?*/

#define SYS_CLK_24MHz ?0 ? //0 内部高频24MHz RC振荡器

#define SYS_CLK_3MHz ?1 ?//1 内部高频 3MHz RC振荡器

#define SYS_CLK_48MHz ?2 ?//2 内部高频48MHz RC振荡器

#define SYS_CLK_6MHz ?3 ?//3 内部高频 6MHz RC振荡器

#define SYS_CLK_XTAL ?4 ?//4 外部晶体振荡器(2-30MHz)

#define SYS_CLK_XTAL_DIV8 5 ?//5 外部晶体振荡器(2-30MHz) 8分频

#define SYS_CLK_PLL ? 6 ?//6 锁相环输出

#define SYS_CLK_PLL_DIV8 7 ?//7 锁相环输出 8分频

#define SYS_CLK_32KHz ?8 ?//8 内部低频32KHz RC ?振荡器

#define SYS_CLK_XTAL_32K 9 ?//9 外部低频32KHz 晶体振荡器

#define SYS_CLK ??SYS_CLK_48MHz

//您只需要修改此处SYSCLK宏定义来修改系统时钟。

S W M 1 9 0

PLL 设定

? ? ? PLL的输入参考时钟源可设置为内部高频时钟或外部高频晶振输入,最大输出时钟可设置为60MHz。

? ? ? 当系统时钟配置为PLL时钟时,可通过配置以下几处寄存器来配置PLL时钟,其配置公式为:VCO输出频率=PLL输入时钟/INDIV*4*FBDIV

PLL输出频率=PLL输入时钟/INDIV*4*FBDIV/OUTDIV=VCO输出频率/OUTDIV

具体宏定义如下:

#define SYS_PLL_SR

SYS_CLK_24MHz

//可取值SYS_CLK_24MHz、SYS_CLK_48MHz、SYS_CLK_XTAL

#define PLL_IN_DIV?6

//SYS_PLL_SRC = SYS_CLK_24MHz 时用6,SYS_PLL_SRC= SYS_CLK_48MHz 时用 12

#define PLL_FB_DIV?30

#define PLL_OUT_DIV8 0

#define PLL_OUT_DIV4 1

#define PLL_OUT_DIV2 2

#define PLL_OUT_DIV??PLL_OUT_DIV8

//此外,在system_SWM190.c文件中还定义了运行过程中更改时钟函数

SystemCoreClockUpdate()

switchTo24MHz()

switchTo3MHz()

switchTo48MHz()

switchTo6MHz()

switchToXTAL()

switchToPLL()

switchTo32KHz()

switchToXTAL_32K()

等一系列的函数方便用户在系统运行过程中修改系统时钟时使用。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- minio 分布式对象存储

- PDsehell16连接pgsql出现“Could not initialize JavaVM“时的解决步骤

- 如何使用idea部署springboot项目全过程

- LeetCode 第381场周赛个人题解

- vue3 element plus 自定义组件封装,多层双向绑定v-model

- Jenkins-Pipeline

- 不要长期把焦点放在让你烦恼的事情上

- 配置dns主从服务器,实现正反向解析

- 第一章-信息安全概述

- 【PHP】Yii2 使用validate规则验证