安路IP核应用举例(OSC、UART)

发布时间:2023年12月19日

1.OSC(内部振荡器)

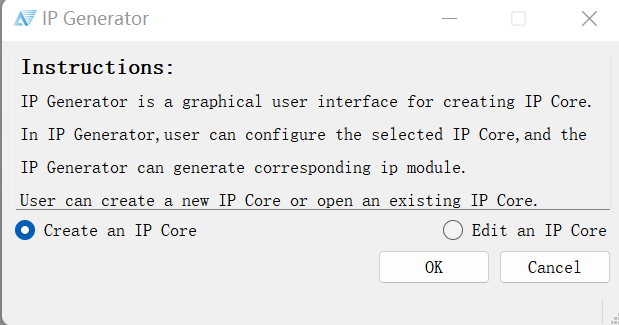

按照Project->New Project顺序新建工程后,后按照Tools->IP Generator顺序,创建IP核,如下图:

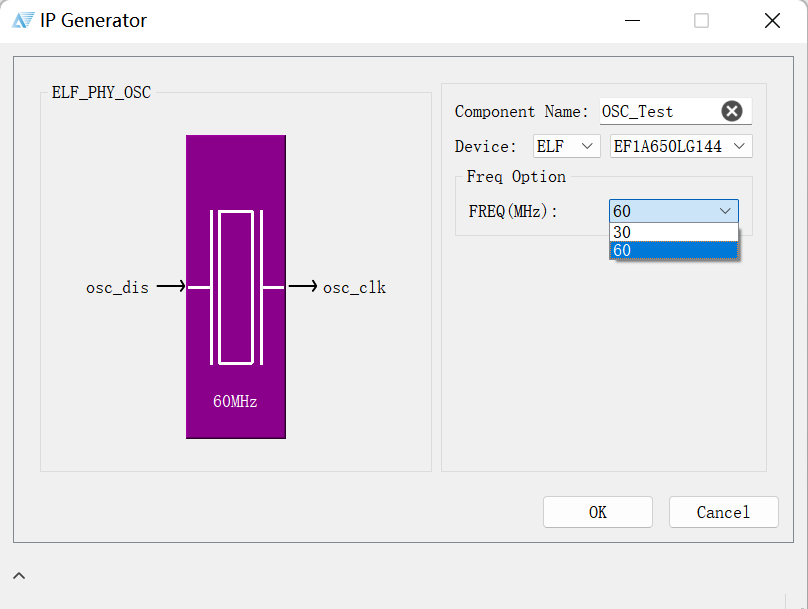

安路FPGA的内置OSC振荡模块频率可选30MHz、60MHz。

可选Verilog或VHDL语言。

如图,生成的.v文件只读,如需进一步的修改,可将文件另存,然后将新文件更新到工程里即可。

osc_clk为输出频率,osc_dis为使能输入,低电平有效,参数“60”为配置频率,单位为MHz。为测试效果,可进行分频后输出,如下:

module OSC_Test( clk_out ); //

output reg clk_out;

//input osc_dis;

wire osc_clk;

reg[24:0]count;

ELF_PHY_OSC #( //例化,配置为60MHz输出

.FREQ("60"))

osc_inst(

.osc_clk(osc_clk), //频率输出

.osc_dis(1'b0)); //使能,低电平有效

always@(posedge osc_clk) //60M分频成1Hz

if (count>=30000000-1)

begin clk_out<=~clk_out; count<=0; end

else

count<=count+1;

endmodule需要注意的是,程序重新Download后,FPGA功能有可能没有随即更新,可关闭电源重新上电再行操作。

2.UART(串口通信)

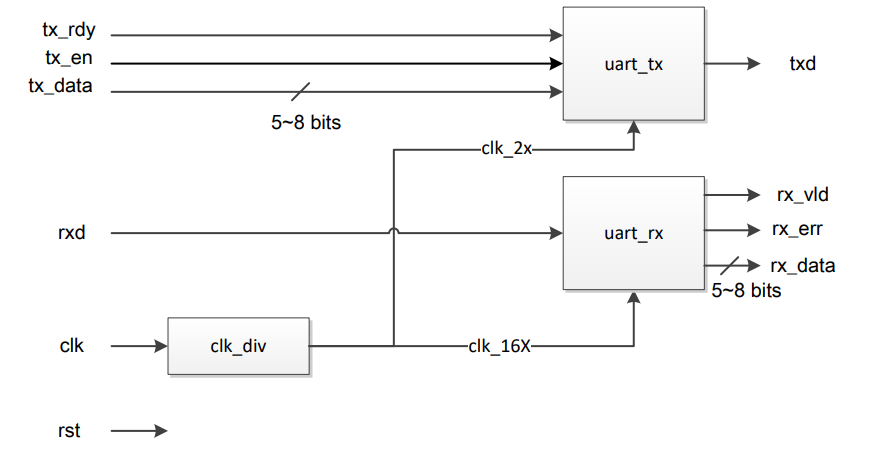

依据安路官方资料,其uart基本结构如下:

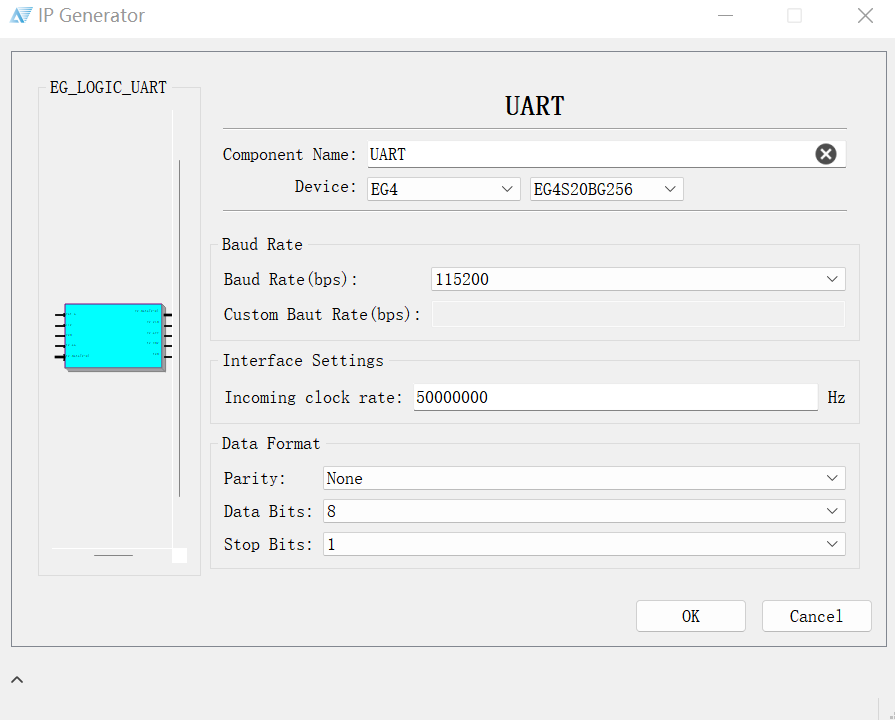

IP核配置选择如下:

以EF1A650LG144为例,24MHz时钟,波特率115200bps。

新建一顶层文件:

module uart_top

(

clk, //24M

rst_n, //低电平复位

rxd, //rxd

txd //txd

);

input clk;

input rst_n;

input rxd;

output txd;

wire tx_en; //发送使能,高电平有效

wire rx_err; //接收错误,高电平有效

wire rx_vld; //接收有效,高电平有效

wire tx_rdy; //高电平准备好,可以发送;低电平发送忙

wire [7:0] tx_data; //8位发送

wire [7:0] rx_data; //8位接收

UART u0(

.clk(clk),

.rst_n(rst_n),

.rxd(rxd),

.tx_data(tx_data),

.tx_en(tx_en),

.rx_data(rx_data),

.rx_err(rx_err),

.rx_vld(rx_vld),

.tx_rdy(tx_rdy),

.txd(txd)

);

assign tx_en=rx_vld&tx_rdy&(!rx_err);

assign tx_data=rx_data+1'b1;

endmodule

以上程序的作用是收到一个ACII码后,加1后回送,效果如下:

引脚约束:

set_pin_assignment { clk } { LOCATION = P20; }

set_pin_assignment { txd } { LOCATION = P143; }

set_pin_assignment { rxd } { LOCATION = P144; }

set_pin_assignment { rst_n } { LOCATION = P120; }3.对于硬木课堂出品的EG4S20开发板来说,如下图,其时钟为50M,rxd、txd引脚分别为F12、D12。

IP核配置如下:

引脚配置如下:

引脚配置如下:

set_pin_assignment { clk } { LOCATION = R7; }

set_pin_assignment { rst_n } { LOCATION = A14; }

set_pin_assignment { rxd } { LOCATION = F12; }

set_pin_assignment { txd } { LOCATION = D12; }

文章来源:https://blog.csdn.net/weixin_41784968/article/details/134231061

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- JS变量、作用域与内存

- 苹果Vision Pro将于1月27日上市!

- Making Large Language Models Perform Better in Knowledge Graph Completion

- Nginx首页修改及使用Nginx实现端口转发

- Android - app实现 A/B 升级

- 获取域控的方法

- 双双入选 中科驭数第二代DPU芯片K2和低时延DPU卡荣获2023年北京市新技术新产品新服务认定

- word中MathType公式编号

- 黑马Java——面向对象进阶(static&继承)

- 系统及应用安全巡检表