FPGA设计时序约束十五、Set_Bus_Skew

目录

一、序言

? ? 在时序约束中,对时钟的约束除了set clock latency,set clock uncertainty,set input jitter外,还有一条set bus skew的约束命令。该命令主要用于跨时钟域的场景中,下面将对set bus skew的使用进行详细的介绍。

二、Set Bus?Skew

2.1 基本概念

? ?Set Bus Skew用于在多个跨时钟域路径中设置一个最大的偏斜要求,可以限制用于发送数据的源时钟沿的数目以及被目的时钟沿捕获。和普通路径上的时钟偏斜不同,bus skew对应的是约束下所有路径中最大的捕获时钟偏斜值,该值同时应用到fast corner和slow corner。

????Bus skew约束通常用于以下几种跨时钟域的拓扑结构中:

????a) 格雷码总线切换中,例如异步FIFOs

????b)带有CE,MUX或MUX hold的多比特跨时钟域电路中

????c) 配置寄存器的跨时钟域

?尽管set_bus_skew命令可以设置一个总线偏斜约束到同步跨时钟域中,但这种做法是多余的,因为setup和hold检查已经可以确保在两个时序安全的同步跨时钟域路径间安全切换。

????总线偏斜约束不属于时序例外,和set_data_check一样,它属于时序断言。因此,总线偏斜约束不会被时序例外约束,如set_clock_group,set_false_path,set_max_delay,set_multicycle_path约束影响,仅可能会被route_design优化掉。

????约束设置时建议将总线偏斜约束到没有扇出fanout的路径上,并且,每个总线偏斜约束必须覆盖最少两个起点和两个终点。

2.2?设置界面

进入Timing Constraints界面,在左侧Assertions栏中选中Set Bus Skew,右侧即显示Set Bus Skew

?

设置界面中Specify bus skew设置总线信号上最快的信号和最慢的信号间的偏斜,start points和end points分别设置起点和终点,Through points设置中间路径,也可不设。同时,也可指定只分析rise、fall或都分析

?

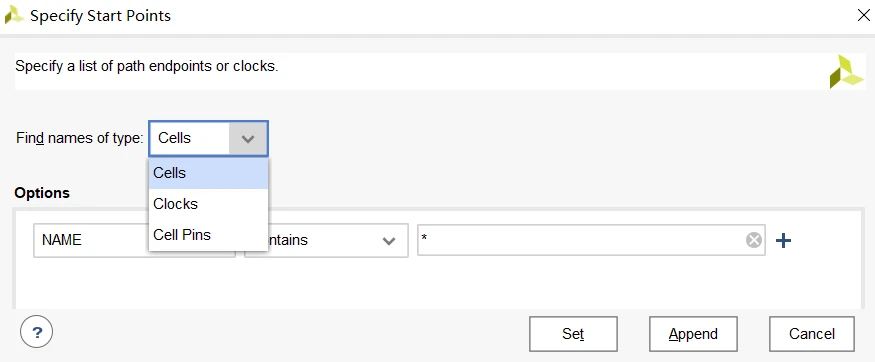

约束from/to的对象,只能为Cells或cell pins或clocks

?

through的对象则只能为Cells,Nets或Cell Pins

2.3?命令语法

命令格式

set_bus_skew [-from <args>] [-to <args>] [-through <args>] <value>

?

2.4 报告分析

????set_bus_skew的分析报告和普通时序报告结果查看有些不一致。可以通过tcl console使用命令或界面运行Report Bus Skew,进入Reports?→?Timing?→?Report Bus Skew

?

对报告进行显示设置

?

也命令执行report_bus_skew -delay_type max -max_paths 10 -name bus_skew_2,bus_skew_2为报告名

?

三、工程示例

3.1 工程代码

设计中跨时钟域是握手机制的一部分,当数据被采样时源时钟发送数据。目的时钟域用了一个4阶同步器来同步发送信号。在4阶同步器之后,信号驱动跨时钟域寄存器的时钟使能端口CE.在这种场景下,必须设置总线偏斜来调整包含CE端口路径上的阶段数,因为它代表了数据有效时目的时钟周期的数目。

module set_bus_skew(src_clk,dest_clk,rst,ce,d,in,out);

input src_clk,dest_clk,rst,ce;

input d;

input [1:0] in;

output reg [1:0] out;

reg [3:0] syn_reg;

reg src_send;

reg [1:0] src_data;

always@(posedge src_clk)

begin

if(!rst)

src_send<=0;

else

src_send<=d;

end

always@(posedge dest_clk)

if(!rst)

begin

syn_reg[0]<=0;

syn_reg[1]<=0;

syn_reg[2]<=0;

syn_reg[3]<=0;

end

else

begin

syn_reg[0]<=src_send;

syn_reg[1]<=syn_reg[0];

syn_reg[2]<=syn_reg[1];

syn_reg[3]<=syn_reg[2];

end

assign des_infer=~syn_reg[3];

always@(posedge src_clk)

if(!rst)

begin

src_data[0]<=0;

src_data[1]<=0;

end

else

begin

src_data[0]<=in[0];

src_data[1]<=in[1];

end

always@(posedge dest_clk)

if(!ce)

begin

out[0]<=0;

out[1]<=0;

end

else

if(des_infer)

begin

out[0]<=src_data[0];

out[1]<=src_data[1];

end

endmodule综合网表连接图如下图所示

?

约束文件,源时钟周期为5ns,目的时钟周期为2.5ns,set_bus_skew对两个起点src_data_reg[0]/src_data_reg[1]和两个终点out_reg[0]/out_reg[1]设置总线偏斜约束

create_clock -period 5.000 -name src_clk -waveform {0.000 2.500} [get_ports src_clk]

create_clock -period 2.500 -name dest_clk -waveform {0.000 1.250} [get_ports dest_clk]

set_max_delay -from [get_cells src_send_reg] -through [get_cells {{out_reg[0]} {out_reg[1]}}] 10.000

set_bus_skew -from [get_cells {{src_data_reg[0]} {src_data_reg[1]}}] -to [get_cells {{out_reg[0]} {out_reg[1]}}] 0.1003.2?时序报告

? ? 先对总线偏斜设置为0ns,此时路径时序违例

?

????将总线偏斜约束设置为0.5ns,违例消失,设置的0.5ns补偿违例的0.492ns,因此,结果为0.008ns

?

四、参考资料

用户手册:ug903-vivado-using-constraints-en-us-2022.2.pdf

链接:https://pan.baidu.com/s/17AK_-J4wRXiFLtLTorlrwg?pwd=mylt?

提取码:mylt? ?

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 012 基本运算符

- ?总结MySQL 的一些知识点:MySQL 选择数据库?

- java/php/node.js/python超市管理系统设计【2024年毕设】

- C语言printf函数详解

- tpt之help.sql这个可以查看所有tpt命令文件的作用

- 【云原生】初识Docker,安装以及了解操作命令

- JSP 和 servlet 有什么区别?

- houdini fft模型

- 【2024】基于springboot的铁路订票小程序系统设计丨另有汽车客运售票

- LanceDB:在对抗数据复杂性战役中,您可信赖的坐骑