14.7-时序反馈移位寄存器建模

发布时间:2024年01月04日

时序反馈移位寄存器建模

1,阻塞赋值实现的LFSR,实际上并不具有LFSR功能

线性反馈移位寄存器(LFSR),是带反馈回路的时序逻辑。

反馈回路给习惯于顺序阻塞赋值描述时序逻辑的设计人员带来了麻烦。

1.1.1,RTL设计,阻塞赋值

//

module lfsrb1(q3, clk, pre_n);

output q3;

input clk, pre_n;

reg q1, q2, q3;

wire n1;

assign n1 = q1 ^ q3;

always@(posedge clk or negedge pre_n)

if(!pre_n) begin

q3 = 1'b1;

q2 = 1'b1;

q1 = 1'b1;

end

else begin

q3 = q2;

q2 = n1;

q1 = q3;

end

endmodule

1.1.2,tb测试代码

module test_lfsrb1;

reg clk, pre_n;

wire q3;

lfsrb1 u1_lfsrb1(

.q3 (q3 ),

.clk (clk ),

.pre_n (pre_n )

);

always #5 clk = ~clk; // T = 10

initial begin

clk = 1'b1;

pre_n = 1'b0;

#100

pre_n = 1'b1;

end

endmodule

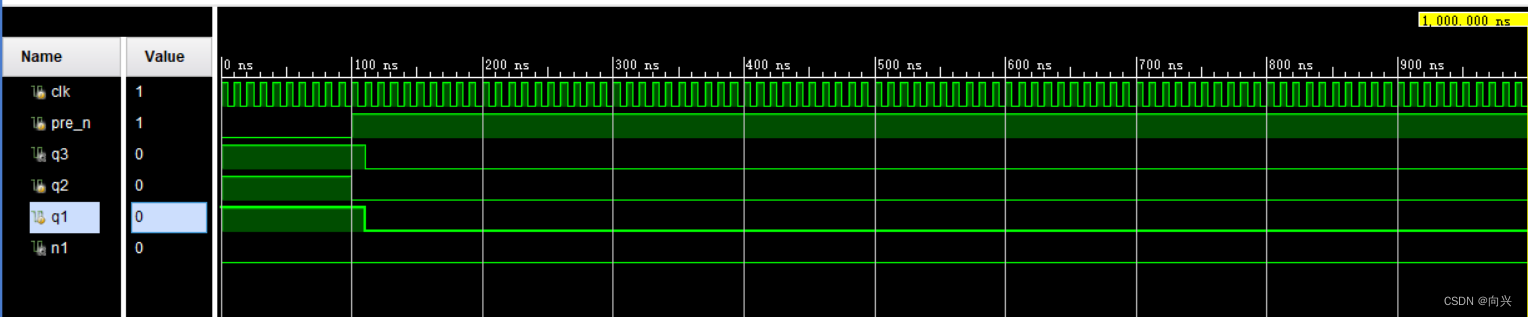

1.1.3,波形仿真输出,SIM输出,没实现LFSR

1.2.1,RTL设计,非阻塞赋值

module test_lfsrb1;

reg clk, pre_n;

wire q3;

lfsrb1 u1_lfsrb1(

.q3 (q3 ),

.clk (clk ),

.pre_n (pre_n )

);

always #5 clk = ~clk; // T = 10

initial begin

clk = 1'b1;

pre_n = 1'b0;

#100

pre_n = 1'b1;

end

endmodule

除非使用中间暂存变量,否则上例所示的赋值是不可能实现反馈逻辑的。

1.2.2,RTL设计,非阻塞赋值

mmodule lfsrb1(q3, clk, pre_n);

output q3;

input clk, pre_n;

reg q1, q2, q3;

wire n1;

assign n1 = q1 ^ q3;

always@(posedge clk or negedge pre_n)

if(!pre_n) begin

q3 <= 1'b1;

q2 <= 1'b1;

q1 <= 1'b1;

end

else begin

q3 <= q2;

q2 <= n1;

q1 <= q3;

end

endmodule

1.2.3,波形功能实现,LFSR

三级目录

文章来源:https://blog.csdn.net/qq_21952195/article/details/135383900

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 软件设计考试相关信息

- Go json 能否解码到一个 interface 类型的值

- 北美“水务巨头”遭遇勒索软件攻击,账单支付系统被破坏

- 破局:疯狂2+1商业模式玩法,顺联动力新零售百亿架构模型

- LinkSLA智能运维 优化企业运维的利器

- sql-labs服务器结构

- 第十九节TypeScript 模块

- 记录--npm, npx, cnpm, yarn, pnpm梭哈

- 研华板卡自带软件Navigator使用说明(基于PCIE1751)

- 阻止指定IP地址进行网站访问的简单方式