STM32H7 CPU Cache 与MDMA冲突问题

发布时间:2023年12月28日

关于最近使用STM32H743+SDMMC+QSPI+MDMA+FATFS读写SD卡与SPI FLASH时的问题:

注:以下修改适用于你使用了STM32H743+SDMMC+QSPI+MDMA+FATFS+Cache缓存的情况。

-

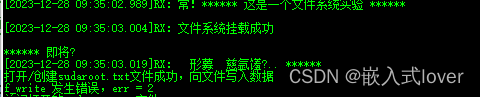

在读写SD卡时,发现f_write函数返回FR_INT_ERR,然后打断点调试发现底层函数返回值没有问题:

](https://img-blog.csdnimg.cn/direct/8dea21ef893b4baea2f8bef774717710.png)

使用读卡器发现数据实际已经写入;这让我百思不得其解,怀疑是什么原因导致数据没有同步;于是想到了会不会是STM32H7的Cache缓存的问题,然后上网找资料,看到了一篇文章:文章链接

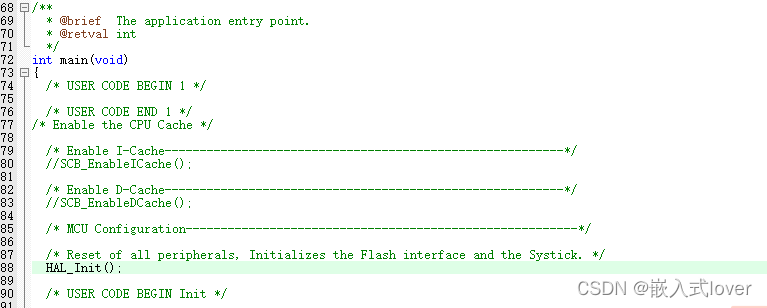

经过这篇文章提示,于是看了代码,确实开启了Cache;尝试关闭后:

果然写入返回错误的问题解决了:

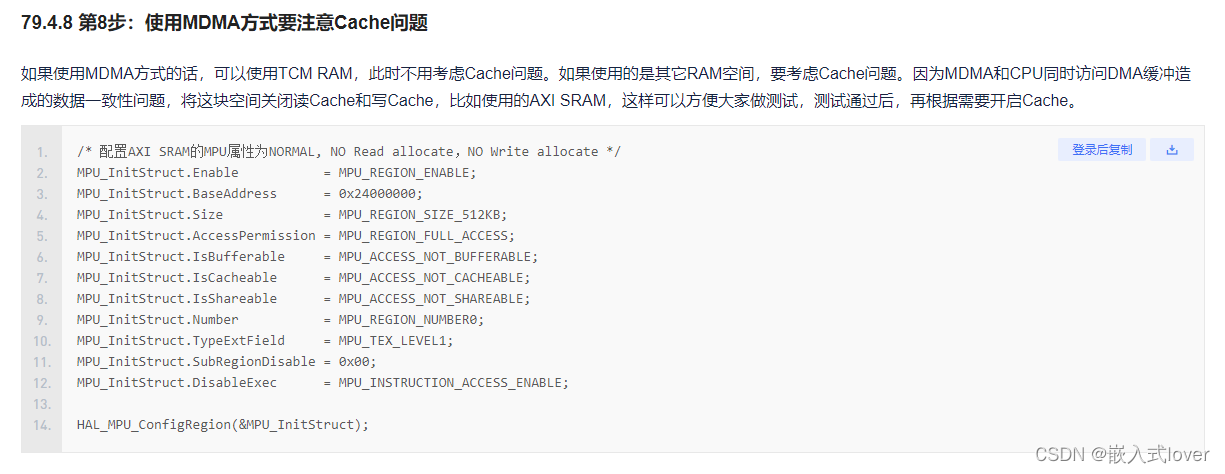

关闭Cacheh后,SDRAM的内存映射读写也变慢了,影响了其他模块性能,问题还未完全解决。

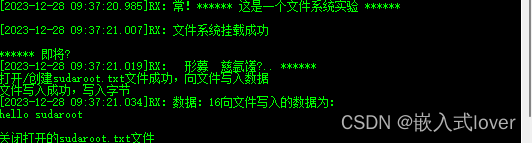

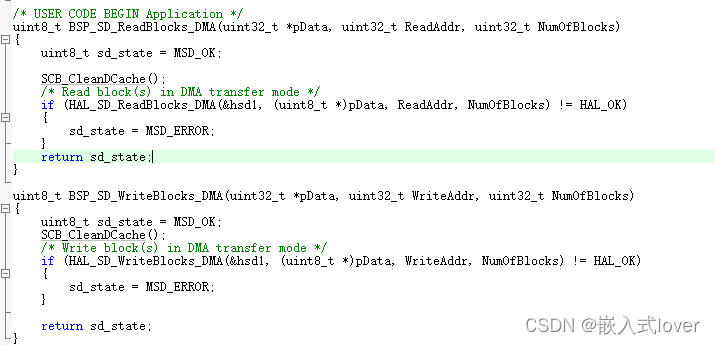

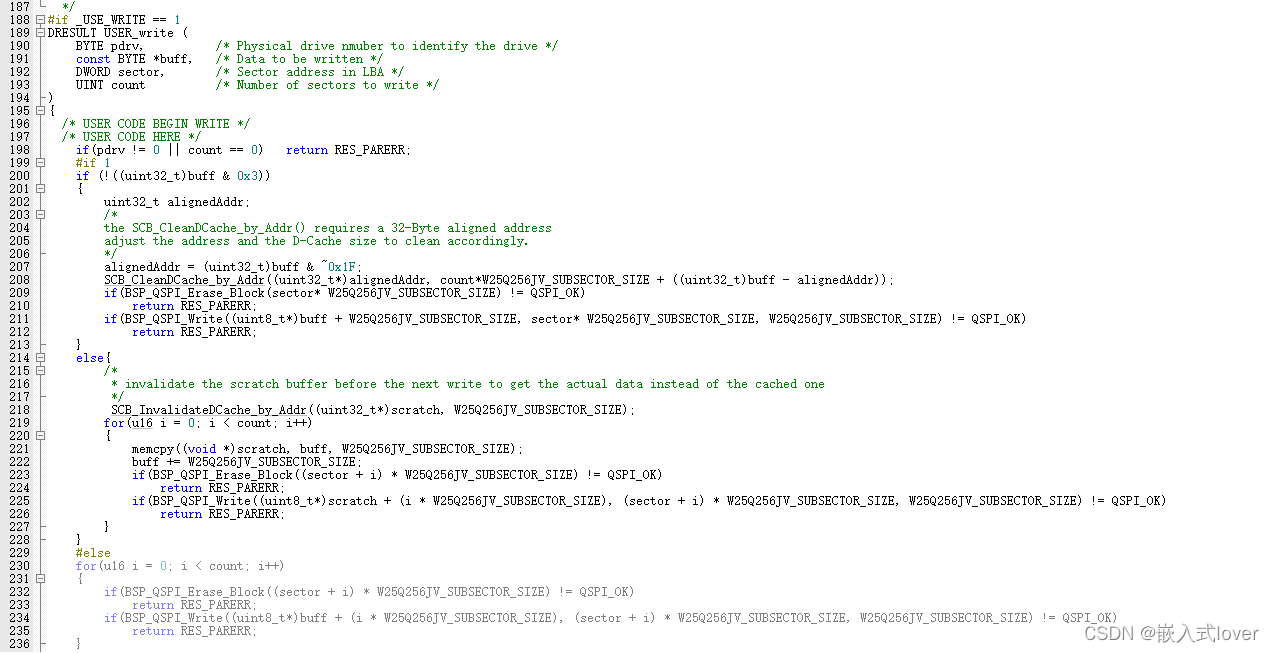

于是想办法在不关闭缓存机制的情况下,能够保证数据的一致性了,然后根据SCB_EnableDCache这个函数跳转,发现了一个SCB_CleanDCache函数,该函数是清除数据Cache的,然后尝试使用了一下,在DMA读写之前调用,重写了下面函数:

测试发现也是可以的,其他模块也没有受到影响,到此,问题全部解决。 -

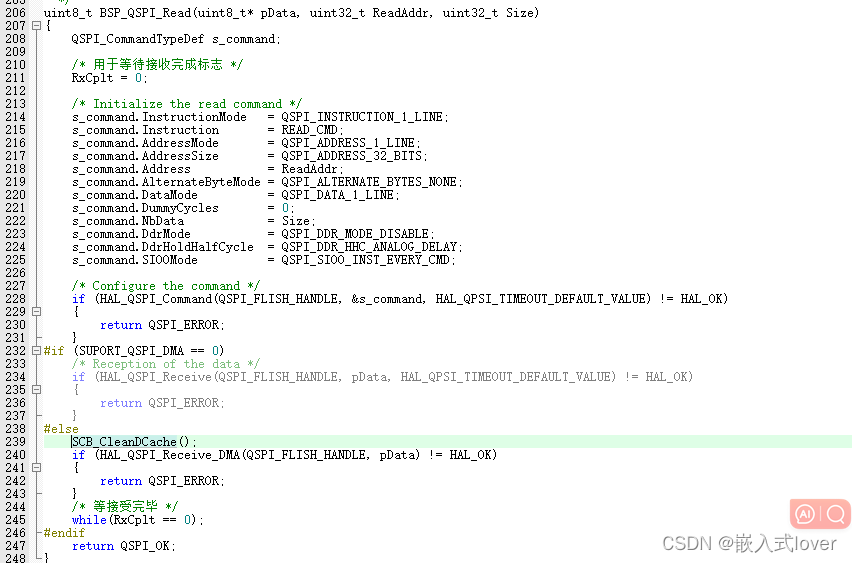

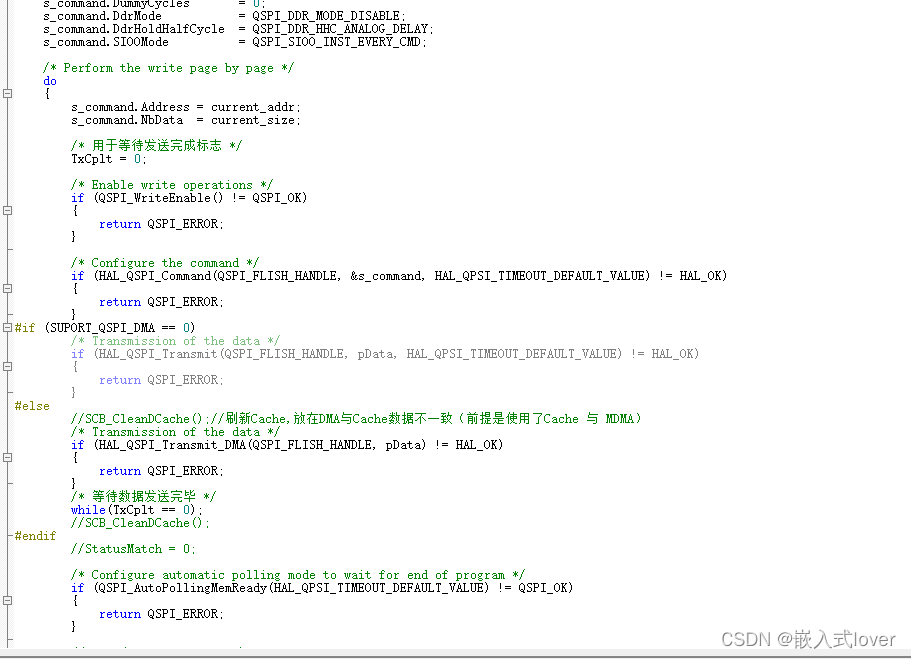

QSPI FALSH读写也是一样,也是MDMA与Cache数据不一致导致的,解决方法可以参考上面SD卡。

修改读写部分函数(底层驱动基于野火开发板例程修改):

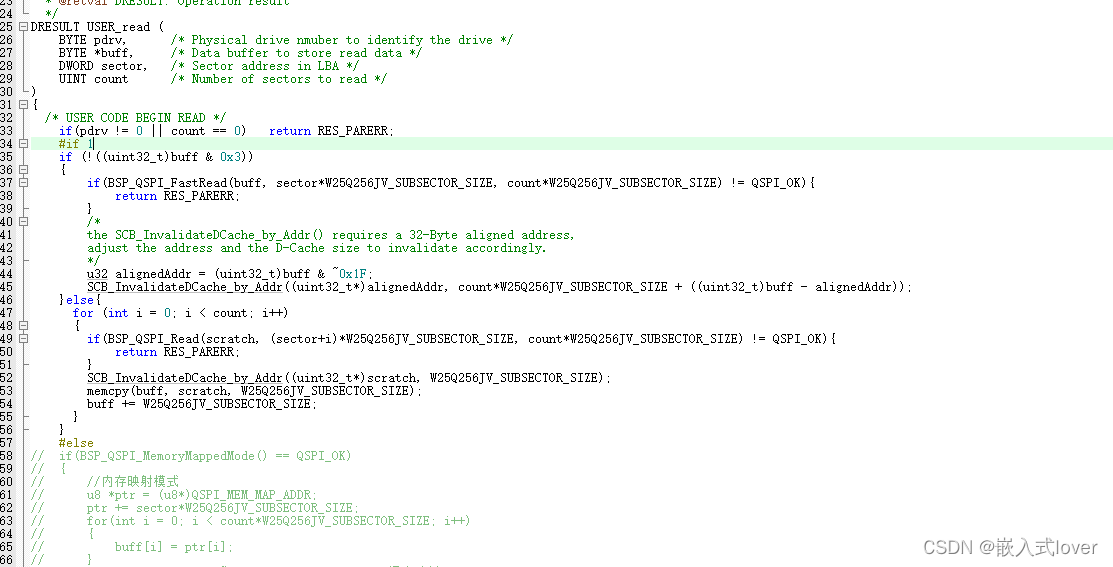

参照SDMMC的磁盘读写(sd_diskio.c文件),完成以下修改:

-

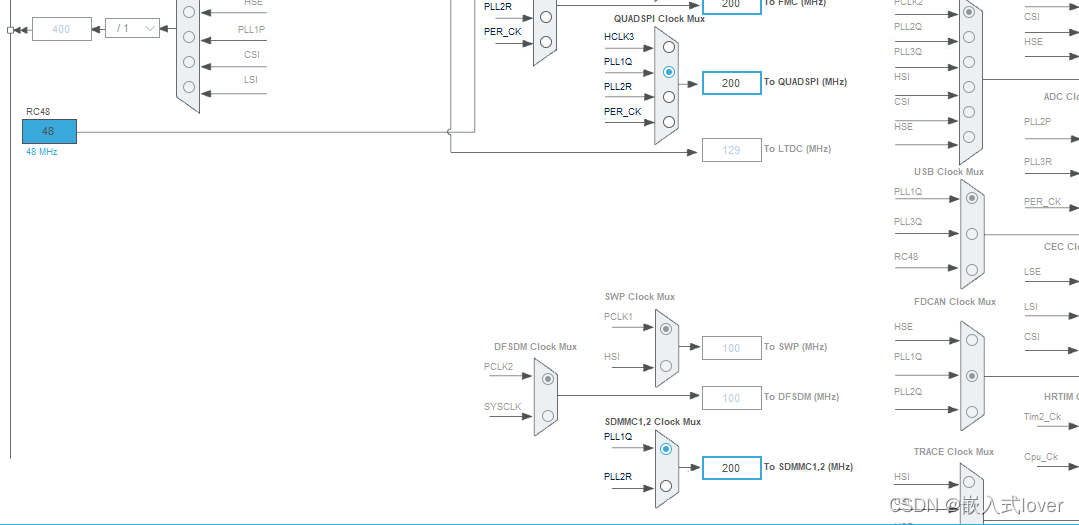

最后注意时钟树的选择:

DTCM内存池,DTCM共128KB,此部分内存仅CPU和MDMA(通过AHBS)可以访问!!!

ITCM内存池,DTCM共64 KB,此部分内存仅CPU和MDMA(通过AHBS)可以访问!!!

之前我QSPI 时钟选择是HCLK3,所以 QSPI按照SD卡改了也不行,更改时钟选择就行了。

文章来源:https://blog.csdn.net/weixin_56565733/article/details/135260889

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- Java三层架构/耦合/IOC/DI

- 【软件工程】走进敏捷开发:灵活、协作、迭代的软件工艺之旅

- 2023安洵杯-秦岭防御军wp

- 使用 CMake 和 Ninja 构建 C/C++ 项目的教程

- 工程监测仪器振弦采集仪的发展与前景展望

- ansible部署安装Tomcat

- 用Python画出漂亮的地图

- 6.6k star!推荐一款轻松创建隔离环境的命令行及容器工具!

- Spring Boot接口请求响应慢,超过10秒以上,如无法优化SQL或代码的情况下,建议写入数据库或缓存中,请求接口时从数据库或缓存中读取返回

- Mybatis-Plus讲义v1.0