浅析CXL P2P DMA加速数据传输拥堵问题的解决方案

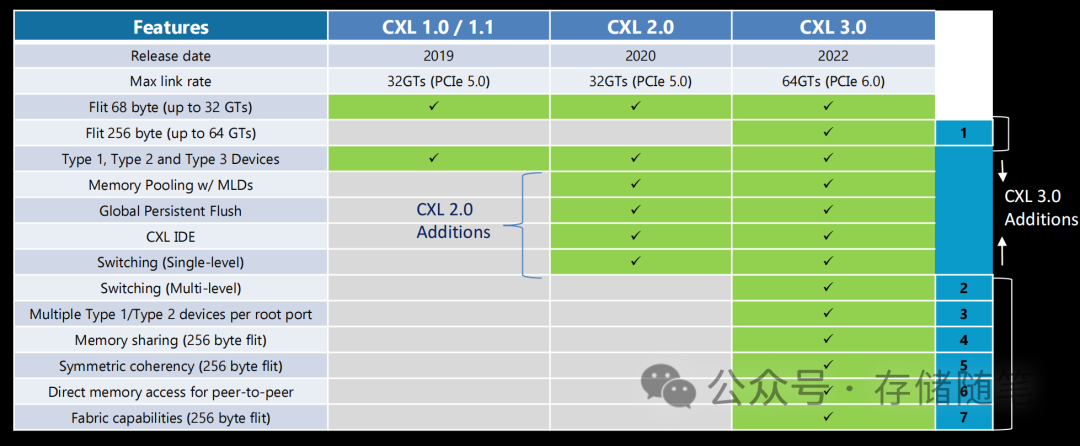

为了改善这个问题,CXL 3.0引入了Unordered-IO和Back Invalidate Snoop新机制,允许更直接和高效点对点数据传输,以减轻上游CXL通道的压力并减少延迟。

(1)Unordered-IO (UIO)

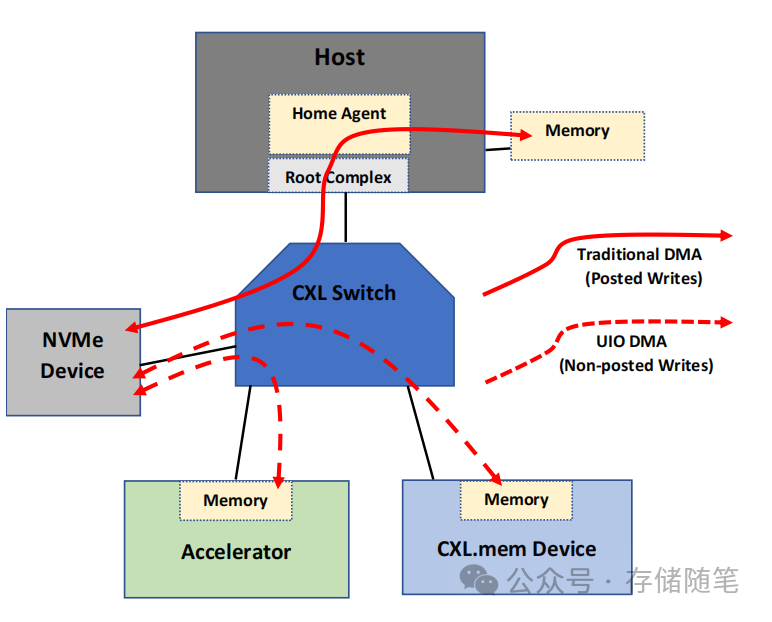

在传统PCIe体系中,DMA传输通常是有序的,要求严格按照顺序完成,否则可能导致数据依赖性错误。而Unordered-IO允许通过CXL Switch进行非顺序化的DMA传输,允许数据包在网络中以最有效的方式流动,无需严格遵循发送顺序。

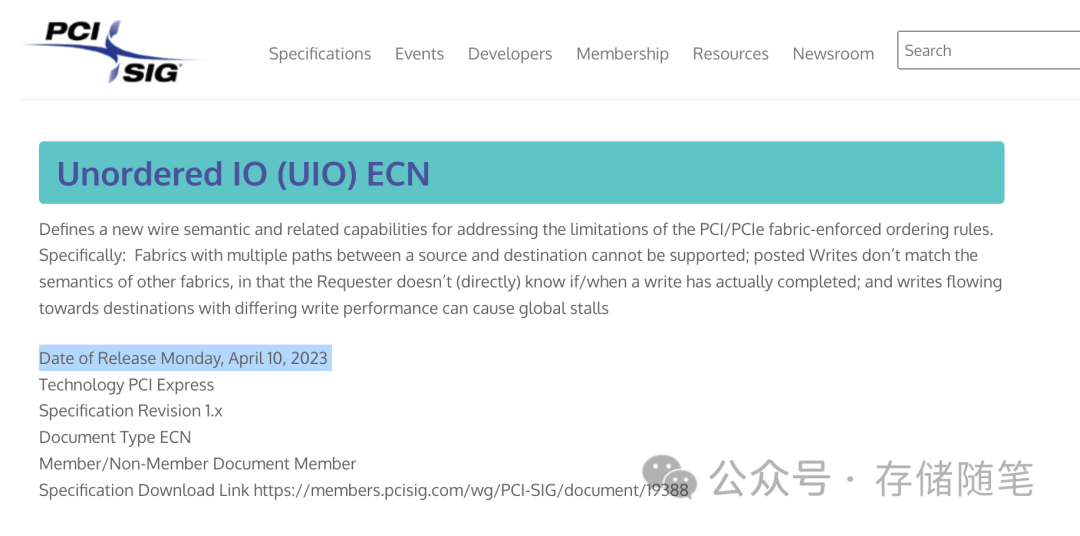

Unordered-IO 是一种PCIe 6.0引入的新型的?TLP格式,主要用于点对点(Peer-to-Peer, P2P)DMA传输。从PCI-SIG官网消息来看,2023年4月10日对外正式发布。

这种特性使得CXL设备可以绕过传统瓶颈,直接通过Switch进行高效的数据交换,降低了延迟,提升了带宽利用率,特别适用于不需要顺序保证的场景。

(2)Back Invalidate Snoop

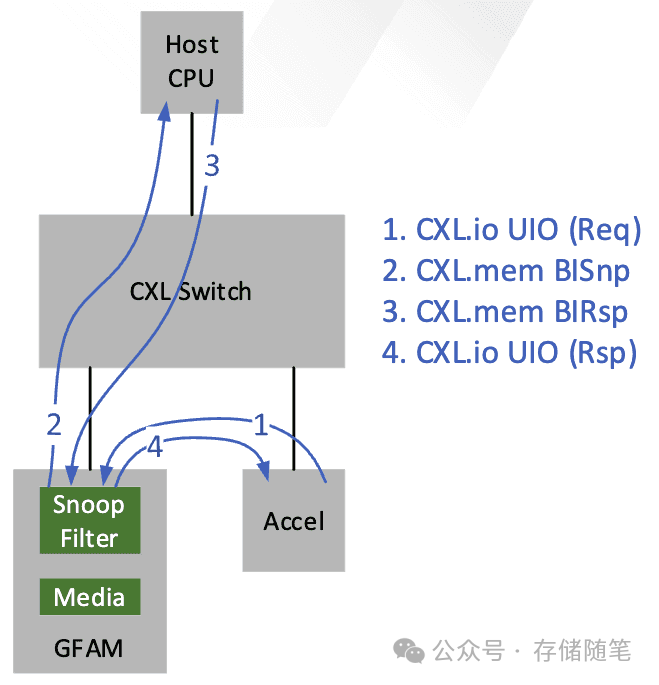

在CXL架构下,为了保持内存一致性,特别是对于共享CXL内存资源的情况,Back Invalidate Snoop 是一种CXL 3.0新引入的请求类型。

当从属的CXL内存设备(如SSD或其他带有CXL.mem接口的存储设备)需要更新自身的内存缓存副本时,它可以发起Back Invalidate Snoop 请求,直接向Home Agent或者其他持有最新数据的设备请求更新一致性状态。

通过这种方式,CXL设备能够在不经过Root Complex的情况下自行发起并完成一致性状态的更新,有效地解除了对上游CXL通道的拥堵,同时降低了遍历延迟。

这两个特性结合使用,不仅可以实现CXL设备间高效、低延迟的P2P通信,还能够确保在整个系统中保持内存数据的一致性,这对于构建大规模、分布式、高性能计算环境至关重要。

不过需要注意,在PCIe 6.0协议中,UIO writes是non-posted TLP,这意味着与posted write相反,UIO写操作不会立即返回确认给发起方,而是等待实际写操作完成后才发出完成信号。由于这种异步性质增加了等待时间,UIO写操作可能会带来一定的性能损耗

在判断NVMe设备是否可以发起UIO DMA时,有三个关键条件必须满足:

-

DMA操作目标地址限定:DMA操作必须明确指向位于同一个CXL switch peer上的地址。也就是说,数据传输的目标必须是直接相连并通过CXL Switch可达的设备。

-

CXL Switch支持UIO P2P:所使用的CXL Switch底层结构必须支持UIO P2P路由功能。这意味着Switch能够识别和处理UIO格式的TLP,并允许其直接在不同设备间传递,而不必经过额外的中间跳转或绕行。

-

目标CXL.mem设备支持Back Invalidate:目标CXL内存设备(CXL.mem)必须具备Back Invalidate功能的支持。这是为了确保在进行U-IO DMA操作时,能够正确地同步内存一致性状态,即当数据发生更改时,相关的缓存条目可以在整个系统中得到及时无效化(invalidate),从而维护全局内存一致性。?

PCIe/CXL扩展阅读:

小编每日撰文不易,如果您看完有所受益,欢迎点击文章底部左下角“关注”并点击“分享”、“在看”,非常感谢!

精彩推荐:

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 第一章 随机事件和概率

- 【LeetCode】232. 用栈实现队列(简单)——代码随想录算法训练营Day10

- hash 密码校验

- 如何才能让手机人工智能无人直播成为商家的引流利器呢?

- 京东年度数据报告:2023全年度平板电视十大热门品牌销量(销额)榜单

- Java基础进阶(学习笔记)

- GZ015 机器人系统集成应用技术样题8-学生赛

- 常见的AdX程序化广告交易模式有哪些?媒体如何选择恰当的交易模式?

- cs231n assignment1——SVM

- UG全参数化建模