【USTC】verilog 习题练习1-5

发布时间:2024年01月18日

1?编写 Verilog 代码,使电路输出信号1

输入格式

无输入

输出格式

输出1,位宽为1

module top_module(

output out

);

// Write your code here

assign out =1;

endmodule2编写 Verilog 代码,使电路输出信号0

输入格式

无输入

输出格式

输出0,位宽为1

module top_module(

output out

);

// Write your code here

assign out = 0;

endmodule3 WIRE

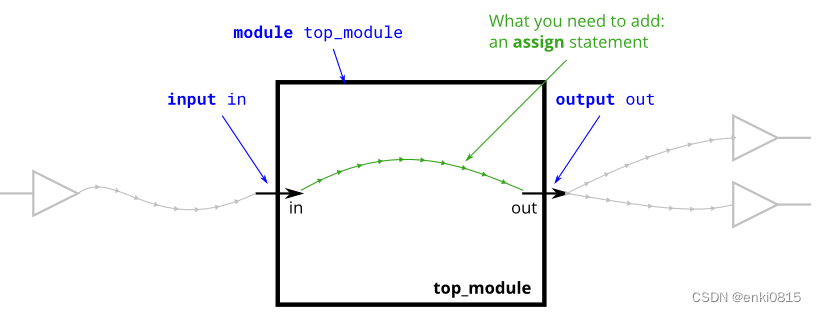

wire 是 Verilog 的关键字,用于表征信号类型的,其含义是线网。wire 可理解为物理连线,但又有所不同,因为 Verilog 中的 wire 是有方向的。例如设计一模块,模块名命名为 top_module,输入信号名为 in,输出信号名为 out,使 in 与 out 直连,如下图所示:

请使用 assign 语句将代码补充完整,使其实现上述电路图的功能。

输入格式

任意

输出格式

与输入完全相同

module top_module(

input in, output out

);

// Write your code here

assign out = in ;

endmodule4?多个端口的模块

题目描述

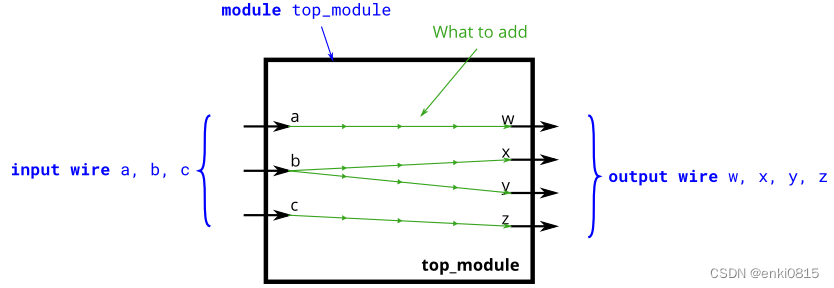

wire是Verilog的关键字,用于表征信号类型的,其含义是线网,wire可理解为物理连线,但又有所不同,因为verilog中的wire是有方向的,例如设计一模块,模块名命名为top_module,输入信号名为in,输出信号名为out,使in与out直连,如下图所示:

请使用assign语句将代码补充完整,使其实现上述电路图的功能

输入格式

1 1 1

输出格式

1 1 1 1

module top_module(

input a,b,c,

output w,x,y,z );

// 请用户在下方编辑代码

assign w=a;

assign x=b;

assign y=b;

assign z=c;

//用户编辑到此为止

endmodule

5?非门

题目描述

创建一个名为top_module的Verilog模块,实现非门的功能

输入格式

无

输出格式

无

module top_module( input in, output out );

// 请用户在下方编辑代码

assign out = ~in;

//用户编辑到此为止

endmodule

文章来源:https://blog.csdn.net/luhputu520/article/details/135651857

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!