【微机原理与接口技术】期末模拟卷(2)

有不会的题可以后台问我的哦,看见了就会回。

本文章主要是微机的模拟卷,最后祝大家期末心想事成

1、微处理器为8086数据总线和地址总线为 ()位

A.16 16

B.16 32

C.16 20

D.32 32

8086是16位寄存器,即需要16位数据线

2、微型计算机硬件系统由()、存储器、输入输出子系统和总线四部分构成。

A.控制器B.寄存器C微处理器D.外设

3、冯·诺依曼基本思想主要是指( )。

A.二进制数和存储程序B.二进制数和存储器C.CPU和存储器D.存储器和输入输出设备

4、若X=+101 1011,则其补码 ()

A.0101 1010

B.1101 1011

C.0101 1001

D.0101 1011

0101 1101

5、若X=+101 1011 ,则其反码为()

A.0101 1010

B.0101 1011

C.1101 1011

D.0101 1111

正数的原码=反码=补码???? 补码=反码+1

6、DMAC8237A有()个独立的通道

A、4??? B 、2? ? C 、8? ?D 、3

7、在进入 DMA工作方式之前,DMA控制器当作CPU总线上的一个()

A.I/0设备B.I/0接口C.主处理器D.逻辑高

8、某存储单元的段基址为 3806H,段内偏移地址为 2948H,该存储单元的物

理地址为()。

A.4100H

B.3A9A8H

C.3B008H

D.3AA08H

9、CPU每次能够响应()个中断源的中断强求

A、1? ? B 、2? ? C 、3? ? D 、多个

10、DRAM的主要缺点是()

A、存储容量小B、价格昂贵C、功耗大D、外围电路复杂

11、某存储器芯片容量为2KX4bit、若用它组成16KX8bit 存储器组,所用芯片数以及用于组内寻址的地址线为()。

A.2片、11根?B.16片、14根??C.8片、16根 D.16片、8根

12、高速缓存由() 构成。

A.SRAM

B.DRAM

C.EPROM

D.硬磁盘

SRAM? 功耗大,价格贵,速度快、集成度低、容量小、用于高速缓存、路由器、服务器

13、关于系统总线说法错误的是 ()

A.数据总线:装载数据和指令代码,是双向的

B.控制总线:CFJ向其他部件传送控制信号,其他部件向 CPU传送状态信

号和请求信号,宽度各异,是双向的

C.地址总线:装载地址信号,是双向的(是单向的)

D.地址线的根数决定了CPU所能直接访问的存储空间容量

14、对于指针与变址寄存器说法正确的是()

A.以下说法都正确

B.参与地址运算的主要是指针与交址存组中的4个寄存SP/BP/SI/DI

C.SP/ESP 堆指针寄存器:用以指出在段中当前栈顶的地址

D.入(PUSH)和出栈(POP)指令由 SP给出栈顶的偏移地址

15、下面哪个寄存器不是专用寄存器 ()

A.SP

B.AX

C.BP

D.SI

16、在编程结构下,按功能分,可将 8086分为()

A.总线接口部件和执行部件

B.运算器和控制器

C总线接口部件和 CPU

D.寄存器组和CPU

17、下列说法正确的是 ()

A.RAM为只读存储器

B.ROM为可读可写存储器

C.RAM 为可读可写存储器

D.RAM和ROM都为可读可写存储器

18、以下寻址方式正确的是 ()

A.MOV 12H,AL

B.MOV CS,1000H

C.MOV ?IP,2000H

D.MOV? AX,[1070H]

?

不能为目的操作数的是:立即数、CS、IP、EIP

不能为源操作数的是:IP

存储器之间不能、段寄存器之间不能

参考mov的使用规则

19、存储器的性能指标不包含 ()

A.速度B.可靠性C.可读可写D.存储容量

20、下列那个不是为调试程序而设置的中断()

A.溢出中断B.单步中断C.断点中断D.中断指令

二、判断题

1.某 RAM 芯片标识为32KX8b,该芯片的地址线和数据线数目为 5和8。×

2.并行通信具有传输速度快、效率高的特点,较适用于远距离的传输。×

3.中断向量就是子程序入口地址。√

4.8086 CPU 有 16 条数据总线,20 条地址总线,能寻址的内存物理空间为 1M。√

5.SRAM存储器元件所使用的 MOS 管多,占用硅片面积大,集成度低,速度慢。×

6.CPU 在指令的最后一个时钟周期检测 INTR 引脚, 若测得 INTR 为高电平且IF 为1, 则CPU在结束当前指令后响应中断请求。√

7.执行 XOR AX,AX 后,AX 寄存器的值为0。√

8.指令指针寄存器 IP 的作用是保存正在执行的条指令所在的位置。×

9.为了保证地址转换的效率,访问存储器时,总是由段寄存 器提供段址。√

10.在存储器的层次结构中,越远离 CPU的存储器,其存取速度越慢,存储容量越大,价格越低。√

三、简答题(每小题5分,共20分)

1、简述为什么要使用 IO 接口电路?

(1)外设设备功能多种多样

(2)信息既有数字式,又有模拟式

(3)多个外设共享总线,信息有串行和并行,而CPU只能接收和发送并行信息

(4)外设速度低且各不相同,需要接口电路对I/O过程进行缓冲

2、运行以下程序

MOV EAX,5439H

MOV EBX,321AH

ADD EAX,EBX

计算运算结果后,标志寄存器中六个标志位的值分别是 多少?

SF=1

ZF=0

PF=1

CF=0

AF=0

OF=1

3、计算机中为什么要采用高速缓冲存储器 (Cache) ?

为了缓解内存与CPU之间速度不匹配的问题。

4、DMAC的功能有哪些?

(1)向CPU发出总线请求控制

(2)实行向三大总线的控制

(3)修改所用的存储器和接口的地址指针

(4)发读写控制信号

(5)字节计数器(存放数据长度直至为0)

(6)交还总线控制权

四、综合题

1、

简述北桥芯片与南桥芯片的异同?

异:

(1)位置不同:南桥芯片位于其硬盘IDE接口或者SATA接口较近的一个位置,北桥芯片位于其CPU较近的一个位置;

(2)作用不同:南桥芯片负责I/O总线之间的通信,北桥芯片负责与CPU的联系并控制内存AGP数据在北桥内部传输;

(3)特点不同:南桥芯片具有双芯片设计,集成网络,高品质音频,显卡工作总线等特点。

同:

北桥芯片和南桥芯片都是主板芯片组中最重要的组成部分。传统来说,靠上方的叫北桥,靠下方的叫南桥。

2、8086 在结构上引入的最重要概念是什么? 以后从 8086到80286,到80386,到 80486,直到Pentium4,每更新一代CPU,主要有什么改进?

(1)8086CPU 在结构上引进的两个主要概念是:指令流水线和存储器分段管理。

(2)从8086到Pentium4,每更新一代 CPU,主要的改进有:

80286:

指令流水线级数由 8086 的两级提高至 4级,提高了数据的吞吐率; 引进虚拟存储器概念, 把外存当内

存用, 扩大了软件可使用的存储空间, 解决了内存容量不足的 问题;

CPU 的工作方式演变出两种:实地址方式和保护方式。在保护方式下 80286 可支持多任务多用户操

作。

80386:

CPU 芯片封装开始采用 PGA 封装,以适应高频率环境;

CPU 增加一种新的工作方式:虚拟 8086方式。

80486:

CPU芯片开始采用通过相应的接口( Socket插座)安装到主板上;

芯片内部集成与 CPU 速度相当的高速缓冲存储器,提高了系统的运行速度; 首次采用 RISC 技术,可在

一个时钟周期内执行一条指令; 采用突发总线方式提高与内存的数据交换速度; 引入倍频技术。

Pentium : 首次引进超标量结构,可在一个时钟周期内执行两条指令,极大地提高了程序的执行速度; 采

用双 Cache 结构; 工作方式增加系统管理方式; 采用分支预测技术。

Pentium Pro :

超标量结构增加至 3 级,流水线级数增至 14级,为设计和制造更高频率 CPU 创造了条件; 引进动态执

行技术,使程序执行效率更高。

Pentium MMX :

增加 MMX (多媒体扩展技术) 指令集, 增强了 Pentium 处理器在音像、 图形和通信方面的能力。 Pentium II :

CPU 封装改用 SEC 卡盒封装形式,提出了将 L2 Cache 和 CPU 整合在芯片内部的思想; 采用双总线结构,

?L2 Cache 能运行在更高频率上( CPU 主频的一半) 。

Pentium III :

新增加 SSE 指令集,进一步增强了 CPU 的音频、视频和三维处理能力,并大大优化网络功能; CPU 主频突破 1GHz。

Pentium 4:

超标量流水线达到 30 多级,使 Pentium4 处理器可达到更高的频率; 首次在台式处理器芯片中引入超

线程技术;增加 SSE2、 SSE3 指令集; CPU 封装改用 LGA 封装形式。

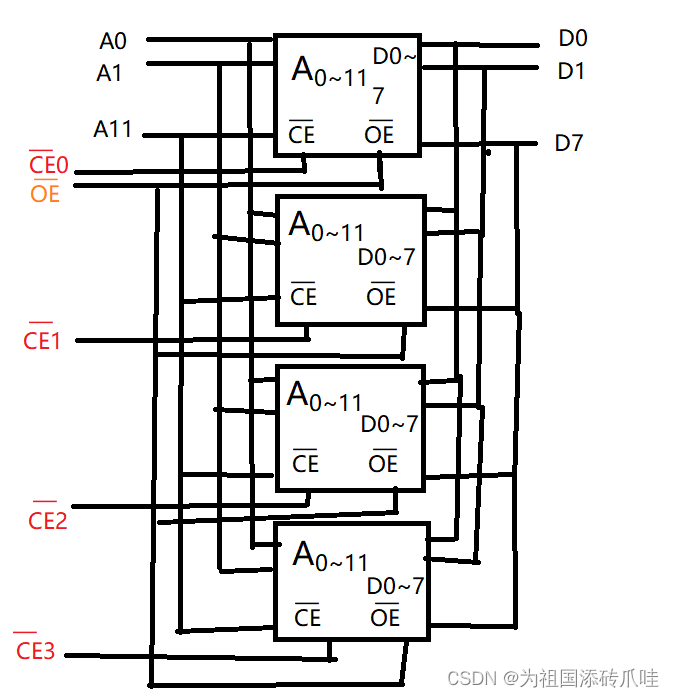

3、利用以下芯片 8b*4KB 扩充到8b*16KB,请画出扩充示意图?

D0~7

OE

CE

A0~11

还可能考的简述题和综合题:

1.CPU为什么这么贵?

2.简述8237A的工作过程

3.pentium的内部结构示意图

4.微型计算机系统的三大层次

5.DMA传送的详细过程

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!