点亮流水灯

发布时间:2024年01月23日

目录

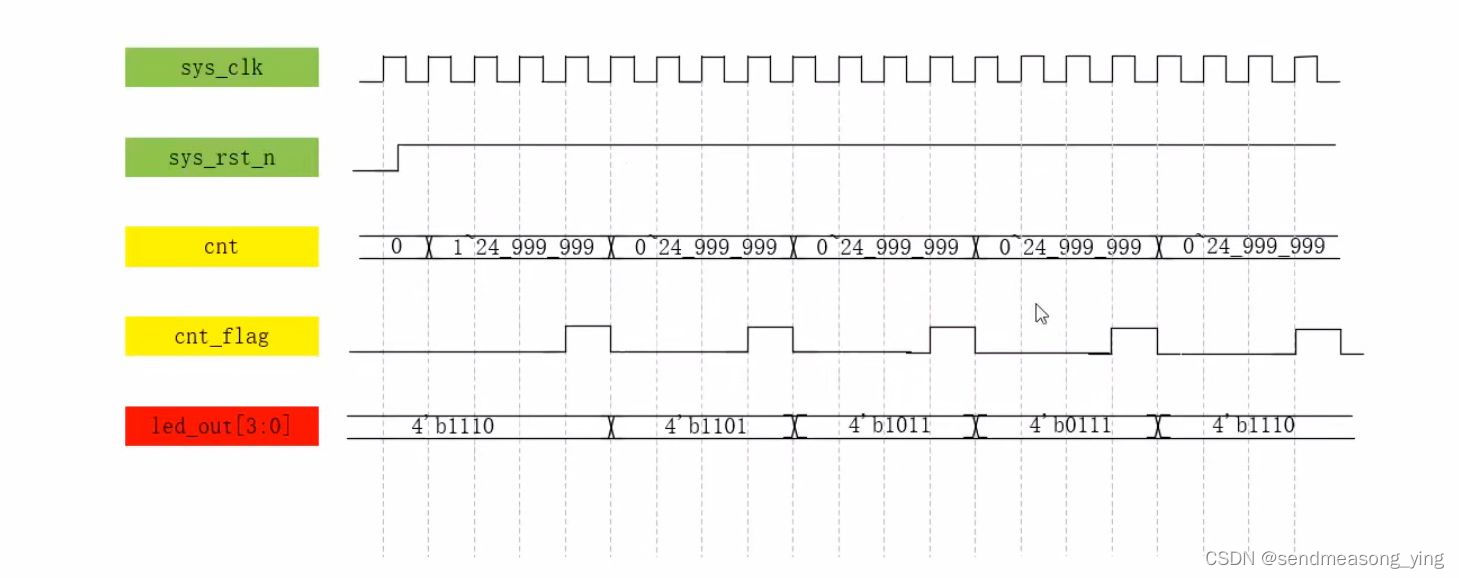

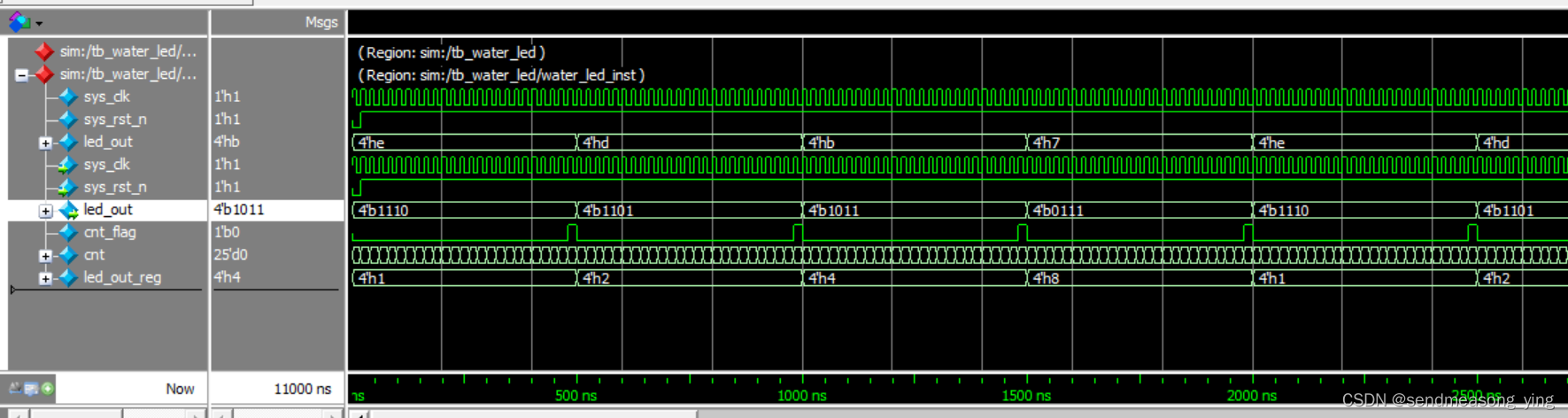

50MHZ一个周期是20ns,0.5秒就是20ns=0.02um=0.00002ms=0.000_00002s。0.5/0.000_00002s=25_000_000个时钟周期,表示要从0计数到24_999_999

LED灯是低电平点亮,前0.5秒点亮第一个LED灯,当检测到脉冲信号点亮第二个灯,然后依次点亮。以上的波形图是采用左移的方式来led_out的赋值的,但是实际会发生错误,因为左移右移都是在空位补零并不会出现如上图的led_out的输出情况,因此考虑增添一个信号。

通过对led_out_reg取反就可以得到需要的输出。

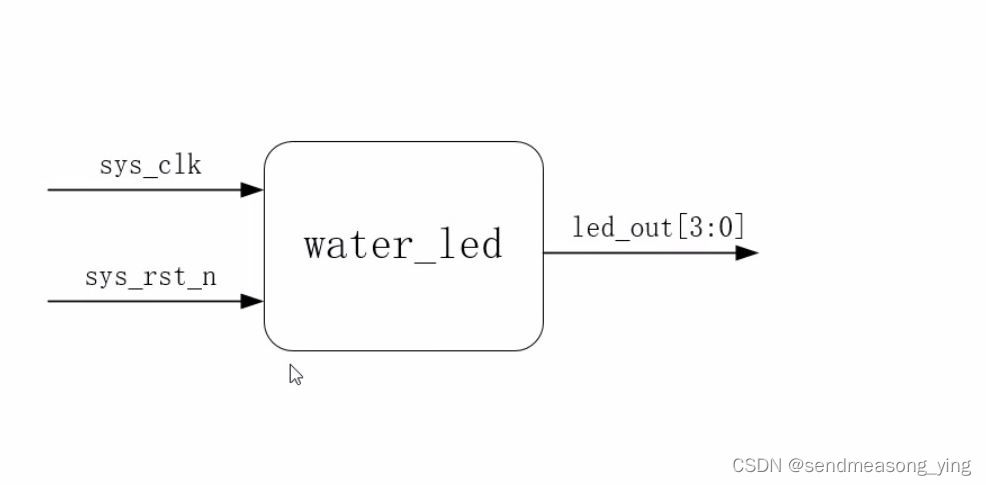

1.water_led

module water_led

#(

parameter CNT_MAX=25'd24_999_999

)

(

input wire sys_clk ,

input wire sys_rst_n ,

output wire [3:0] led_out

);

reg [24:0] cnt ;

reg cnt_flag ;

reg [3:0] led_out_reg;

assign led_out=~led_out_reg;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n==1'b0)

cnt<=25'd0;

else if(cnt==CNT_MAX)

cnt<=25'd0;

else

cnt<=cnt+25'd1;

always@(posedge sys_clk or negedge sys_rst_n)

if (sys_rst_n==1'b0)

cnt_flag<=1'b0;

else if (cnt==CNT_MAX-1'b1)

cnt_flag<=1'b1;

else

cnt_flag<=1'b0;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n==1'b0)

led_out_reg<=4'b0001;

else if((led_out_reg==4'b1000)&&(cnt_flag==1'b1))

led_out_reg<=4'b0001;

else if (cnt_flag==1'b1)

led_out_reg<=led_out_reg<<1;

//左移,右移这两种移位运算都用0来填补移出的空位

else

led_out_reg<=led_out_reg;

endmodule2.tb_water_led

`timescale 1ns/1ns

module tb_water_led();

reg sys_clk;

reg sys_rst_n;

wire [3:0] led_out;

initial

begin

sys_clk=1'b1;

sys_rst_n<=1'b0;

#20

sys_rst_n=1'b1;

end

always#10 sys_clk=~sys_clk;

water_led

#(

.CNT_MAX(25'd24)

)

water_led_inst

(

.sys_clk (sys_clk),

.sys_rst_n (sys_rst_n),

.led_out (led_out)

);

endmodule

文章来源:https://blog.csdn.net/m0_51133942/article/details/135758363

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 【Java】SmartTomcat的配置及使用

- 为何我选择山海鲸可视化:五大优势解析

- 大创项目推荐 深度学习的视频多目标跟踪实现

- 组态王与S7-1200PLC之间 Profinet无线以太网通信

- 基于AT32F421的freemodbus 移植

- Linux日志服务管理

- 阿里云账号注册之后实名认证选择个人还是企业认证好?有什么区别?

- 【神器】wakatime代码时间追踪工具

- NLP深入学习(四):贝叶斯算法详解及分类/拼写检查用法

- Java常用日期类