vivado RTL分析

RTL分析

概述

AMD Vivado? Design Suite具有由源文件表示的设计的三个视图和添加到项目中的设计约束,或在非项目模式下读取到内存中:阐述了RTL的设计、综合设计、布局和布线设计。RTL顶层设计的细化运行RTL linting检查,执行高级优化,从RTL推断逻辑,构建设计数据结构,并可选择应用设计约束。在默认的断章取义设计流中,您也可以使用Vivado设计套件包括IP核心的综合设计检查点(DCP)、块设计、DSP模块或分层块。

提示:将断章取义的模块包括在详细设计中可以增加详细设计的时间过程,因为Vivado工具将合成设计中不最新的任何模块。此功能可以在设置对话框的精化选项卡下启用或禁用。

Vivado Design Suite为RTL设计提供了许多分析功能。例如,您可以:

?RTL过梁

?使用“图解”和“层次”窗口可视化设计细节

?窗口之间的交叉探测

?运行设计规则检查(DRCs)

?查看信息

?搜索使用Find命令生成的RTL网表

?在RTL级别创建和应用约束

注意:在此阶段无法运行时序分析。

RTL设计初探

RTL linting是分析RTL代码的一个重要工具,可以捕捉语法错误等问题QoR问题。它有助于RTL设计者提高生产力,越来越多地被用户采用。run linter是Vivado的内置功能,它分析RTL设计代码并提供违规行为的详细报告。您可以通过单击RTL来激活过梁功能分析?→??在流导航器中运行Linter。Run Linter有助于检测通过提供错误的详细分析,在早期阶段。当你点击Run Linter,Vivado时自动检查和编译RTL源文件,并通过打开提供详细报告Linter窗口。单击“文件名”列中的分析超链接将打开相应的文件,并突出显示代码中违反的行。如果意外违规由该工具报告,您可以通过创建弃权来忽略违规行为。单击“确定”时,放弃复选框将显示增加了设计中的总豁免数量。

?导出到电子表格:将“导出表格”打开为电子表格格式,以导出违规情况报告到要在Microsoft Office或Open Office平台上打开的电子表格。

重要!Linter窗口不会自动更新。如果源文件中有变化,请确保重新运行linter以查看更新的结果。

注意:在当前版本中,linter不支持OOC模式的多次运行。门楣大部分是其通常用全局合成来合成。

项目模式下的设计细化

项目中启用的RTL源文件在合成过程中会自动详细说明。你可以还手动详细说明了用于约束开发和RTL网表探索的源文件。这个消息窗口显示来自细化和编译的消息。您可以选择在Vivado IDE项目设置中详细说明期间使用的HDL语言选项。对于信息,请参阅常规设置。精化结果不会与设计一起保存。每次打开详细设计时重新阐述。但是,可以保存在详细设计中创建的任何约束。将设计源文件导入项目后,请使用以下任一方法精心设计并打开设计:

?选择流量?→?开放式精心设计。

?在流导航器的RTL分析部分,选择打开详细设计以加载详细阐述了网表、活动约束集和目标设备到内存中的情况。要指定要详细说明的设计名称,请使用以下任一方法:

?选择流量?→?开放式精心设计。

?在Flow Navigator中,从RTL Analysis右键菜单中选择New Elaborated Design。如果您的设计中存在断章取义的设计模块、IP核、块设计、DSP模块来源,打开详细设计时会显示该消息。该消息指示“OOC的链接IP运行”和“精化设置”对话框中的“加载约束”选项可能会影响打开详细设计的性能。您可以禁用这些设置以加快阐述。有关更多信息,请参阅精化设置。

打开详细设计时,Vivado design Suite会自动检查并编译RTL源文件,生成顶部原理图视图,并在中显示设计默认视图布局。

在大多数情况下,Vivado IDE会自动识别设计的顶部模块。在某些方面在可能有多个候选者的情况下,该工具会提示您选择顶部模块用于设计。您也可以手动定义顶部模块,方法是从右键单击“源”窗口中的菜单。

注意:在“源”窗口的“层次结构”视图中,顶部模块图标标识当前顶部单元Tcl命令在项目中细化设计模式以下是相关的Tcl命令:

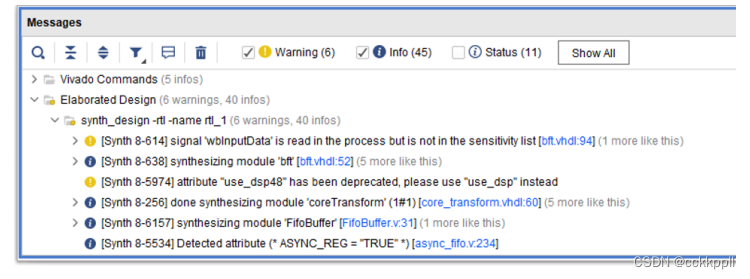

查看精化消息

消息窗口显示编译结果,并标记RTL中的异常情况详细设计部分下的源文件。您可以筛选“消息”窗口以显示来自的错误、警告或信息性消息RTL阐述的结果。为了启用或禁用错误、严重警告等的显示,“警告”或“信息性消息”,请选中“消息”窗口标题中的复选框。您可以在“消息”窗口中选择任何警告或错误消息来加载Vivado IDE文本中突出显示所选源代码的相应RTL源文件编辑

?网表视图:显示RTL层次结构和基元的可扩展逻辑树。

?层次结构视图:显示逻辑层次结构的图形表示。

?原理图视图:在可探索的原理图表示中显示逻辑和层次结构。

默认情况下,当您通过在流中运行“打开详细设计”来详细设计时导航器,RTL原理图显示整个设计。所有视图交叉选择提供探索和分析逻辑设计的独特能力。有关更多信息,请参阅Vivado Design Suite用户指南:使用Vivado IDE(UG893)。

精细化设计方案探索

您可以在RTL网表窗口中选择任何级别的逻辑层次结构,并将其显示在RTL中原理图窗口。要为任何选定的逻辑调用RTL原理图窗口,请执行以下操作之一以下内容:

?选择工具?→?略图的

?在“网表”窗口中,从右键单击菜单中选择“原理图”。

有关遍历、展开和探索RTL原理图的更多信息,请参见使用Vivado Design Suite用户指南中的示意图窗口:使用Vivado IDE(UG893)。

您还可以使用“查找”命令,使用一系列过滤技术。请参阅在Vivado Design Suite中查找设计或设备对象用户指南:使用Vivado IDE(UG893)获取更多信息。

使用层次窗口

Vivado IDE包括一个“层次”窗口,该窗口用于查看设计要调用任何选定逻辑的“层次结构”视图,请执行以下操作之一:

?选择工具?→?显示层次结构。

?在“网表”或“原理图”窗口中,从右键单击菜单中选择“显示层次”。这些窗口具有完全的交叉探测支持。在网表或原理图中选择的逻辑窗口在“层次”窗口中高亮显示。

探索RTL源文件

您可以在“网表”视图或“原理图”中选择任何逻辑元素,并打开的实例化RTL源文件中实例化的对象。您也可以打开逻辑的定义在RTL文件中定义。要打开RTL源文件中任何选定逻辑的实例化或定义,请选择对象,然后从右键单击菜单中选择“转到源”或“转到定义”。Vivado IDE打开相应的源文件,并突出显示特定实例。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 一文读懂可转债交易,利用可转债交易创造年化收益!

- 大数据框架数仓Doris学习网站,让你轻松掌握数据仓库技能。

- 【openwrt】【procd】Openwrt系统启动流程分析

- day22 二叉搜索树的最近公共祖先 二叉搜索树中的插入操作 删除二叉搜索树中的节点

- PWR 电源控制-stm32入门

- 只会 Python 不行,不会 Python 万万不行 。。。

- Jmeter的安装与快速使用(做并发测试)

- 从0开始学C++ 第六课:控制流程和循环结构

- 做无货源跨境电商必备:各电商平台商品采集API

- Openai的openai新版本调用方式