低功耗设计之Retention cell

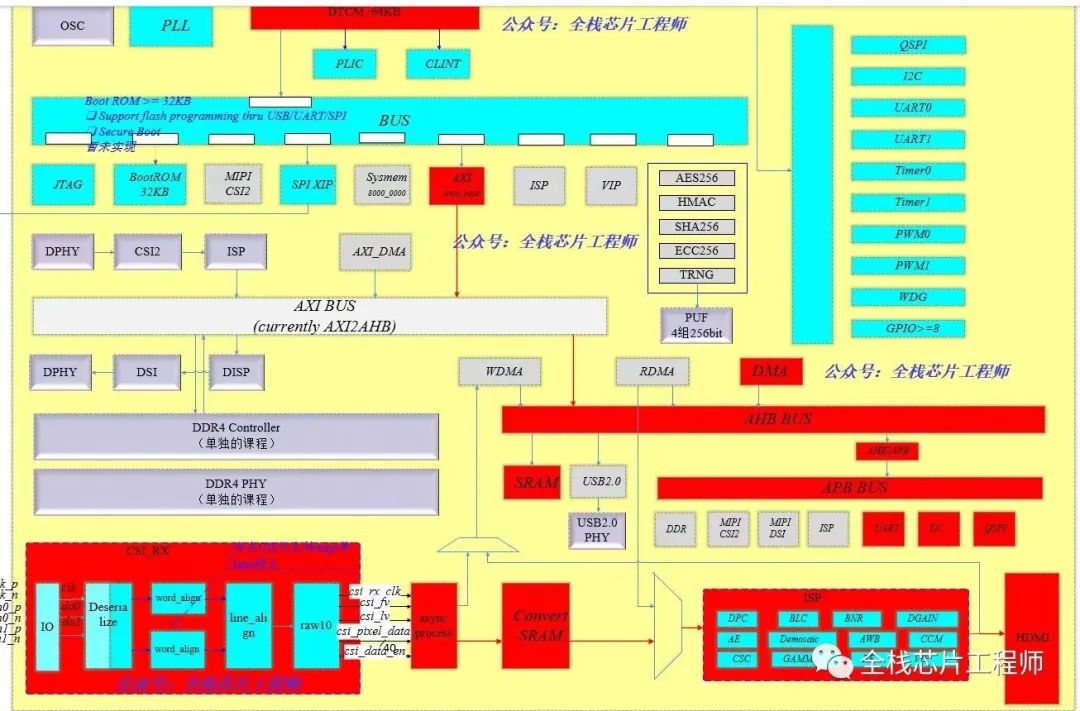

SoC芯片在需要休眠时候,可以关掉CPU总线等高速逻辑来降低功耗,但是重新上电唤醒又太慢怎么办?我们可以用retention cell来保存CPU的堆栈等关键寄存器数据,既满足了上电唤醒速度快的需求,也满足了掉电省功耗的要求。景芯SoC休眠掉电时,将关键数据保存在SRAM,SRAM采用双电源设计,这样设计不仅节省了面积,还降低了设计复杂度。

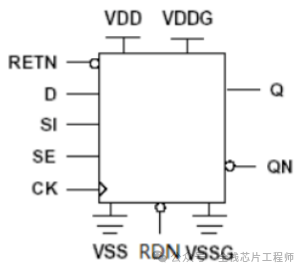

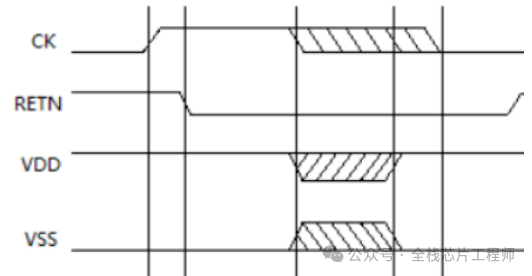

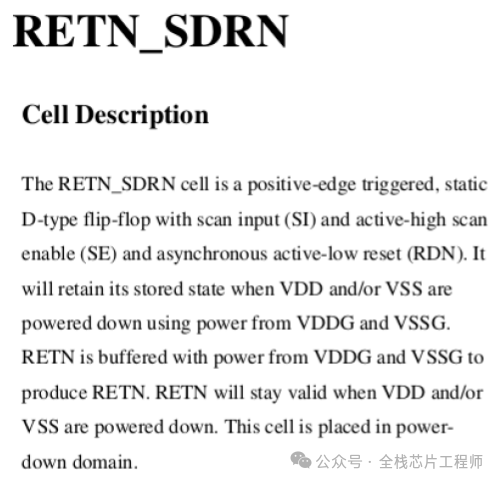

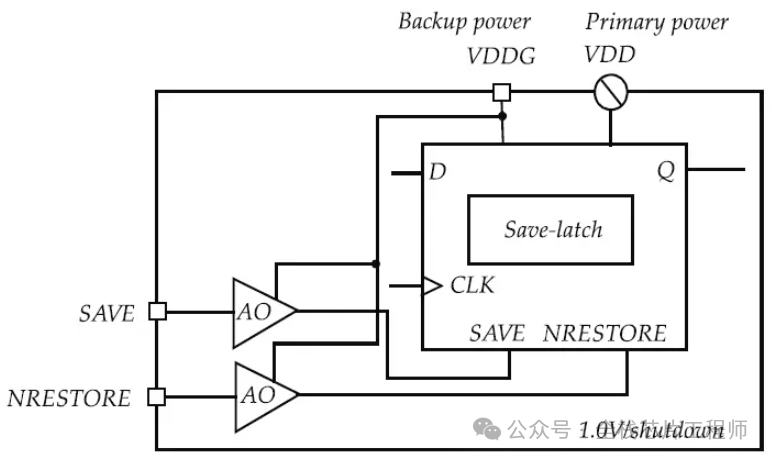

Retention cell能够在Primary电源VDD关闭的情况下保持内部状态,但其实并不是完全断电,还有backup VDDG电源。

请问,RETN的供电谁来决定?RETN可否断电?

答:RETN是由BUF驱动,且BUF由VDDG VSSG供电,VDD VSS掉电后,RETN需要保持有效,具体由PMU模块设计,景芯SoC提供了PMU设计。注意,景芯SoC是将RETN信号放在power shut domain的,这样可以尽量避免always on buffer的使用,为何要减少always on buffer的使用,景芯SoC训练营讲过很多了不在赘述。

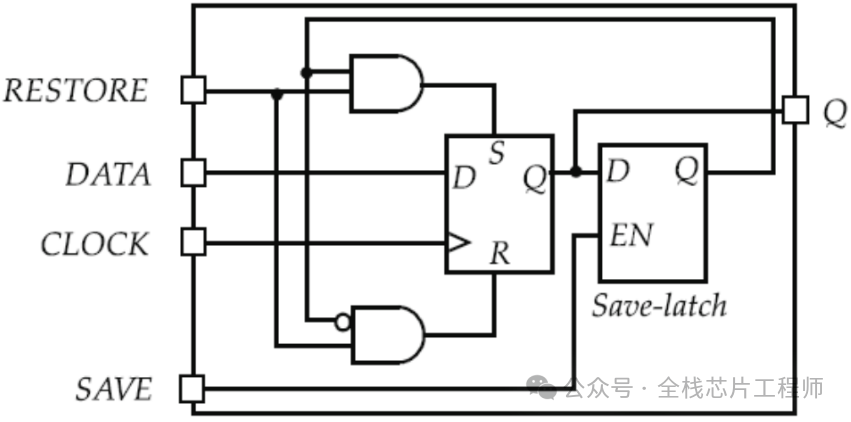

Retention cell相比普通寄存器多了一个save-latch,save-latch可以在关电的时候保存状态,在重新上电的时候恢复普通flip-flop的状态。Save-latch一般是一个hvt cell, 以节省静态功耗,注意,Save-latch是由备用电源VDDG VSSG供电。

正常情况下,Retention flip-flop和普通的flip-flop功能一样,但是会在SAVE信号有效时候将flip-flop输出锁存在Save-latch中,当电源关掉时,由于Save-latch是由backup电源供电,Save-latch能锁存SAVE保存的信号;当RESTORE信号拉成1时,Save-latch会把输出送给前面的flip-flop,就快速恢复下电时的状态,类似网页浏览器关闭了下次直接自动打开,非常丝滑。

请问,Retention cell能大量使用吗?大量使用有什么影响?欢迎加入全栈芯片工程师知识星球讨论。

景芯SoC芯片全流程设计训练营的宗旨:

【让每个学员都能设计一款SoC/MCU芯片】

【全网唯一】景芯SoC是一款用于【芯片全流程设计培训】的低功耗ISP图像处理SoC,采用低功耗RISC-V处理器,内置ITCM SRAM、DTCM SRAM,集成包括MIPI、ISP、USB、QSPI、UART、I2C、GPIO、以太网MAC控制器等IP,采用SMIC40工艺设计流片。

(一)SoC前端课程,您将学会

-

高速接口的Verilog设计实现

-

从图像算法到RTL设计实现

-

MIPI、ISP的Verilog实现与仿真

-

Lint、CDC检查及UVM验证

-

后仿真

仅前端一门课程内容就抵得上其他培训机构的5-6门课程。

(二)SoC中端课程,您将学会

-

DFT设计(芯片级)

-

Synthesis逻辑综合(芯片级)

-

低功耗UPF设计、CLP技术

-

formal验证等技术

仅中端一门课程内容就抵得上其他培训机构的4-5门课程。

(三)SoC后端课程,您将学会

-

低功耗设计

-

布局布线(低功耗FF flow)

-

StarRC/QRC

-

STA/Tempus

-

功耗分析

-

DRC/LVS设计

仅后端一门课程内容就抵得上其他培训机构的3-4门课程。

SoC培训营的知识星球

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 营销投放下半场,游戏行业如何寻觅进化空间?

- 前端(angular)在谷歌(chrome)浏览器使用高德地图api定位报错超时geolocation time out ,能定位但不安全的方法

- 计算机配件杂谈-鼠标

- 2024.1.3每日一题

- 在vue中使用高德地图点击打点,搜索打点,高德地图组件封装

- 设计模式-工厂模式

- JavaScript-事件-笔记

- ArkTS 状态管理@Prop、@Link

- linux 15day apache apache服务安装 httpd服务器 安装虚拟主机系统 一个主机 多个域名如何绑定

- Java初学