Verilog语法——6.测试文件使用for和random语句进行赋值

发布时间:2024年01月16日

参考资料

【明德扬_verilog零基础入门语法HDL仿真快速掌握-手把手教你写FPGA/ASIC代码设计流程中的应用】

6. 测试文件使用for和random语句进行赋值

6.1 for语句的使用

- 题目要求:

- 涉及到for语句的赋值语句:

//之前要先定义一个integer i

integer i;

//for赋值语句开始

for(i = 0;i < 99;i = i + 1)begin

din = (i==0) ?0:(din + 1);

din_sop = (i==0) ?1:0;

din_eop = (i==99)?1:0;

din_vld = 1;

din_err = 0;

#(CYCLE*1);//需要根据实际情况,放到for循环末尾或者最开始

end

小贴士

- verilog不支持c/c++中的自增语句i++,因此只能写成i=i+1

- for语句应该用在initial begin(…) end中,此处只展示关键代码

6.2 random语句的使用

6.2.1 random语句产生随机数

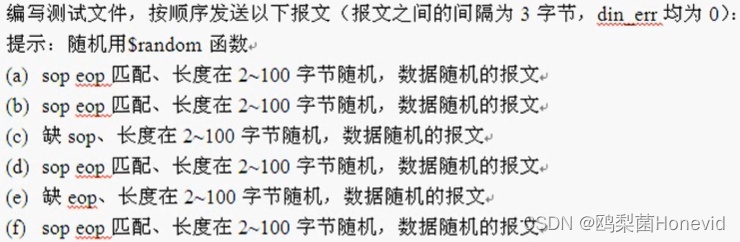

- 题目要求

- 含random语句产生随机数的代码

//之前要先定义一个integer i和长度变量,设置长度符合题目条件

integer i;

reg[6:0] len;

//对len长度变量进行规约

len = $random;//len是7位2进制数,范围是0-127,因此随机数范围也是0-127

len = len % 99;//mod操作,len只能取0-98之间的数

//len取0-98,下面取len+2的值,那么真实长度值的范围即2-100

//for赋值语句开始

for(i = 0;i < (len+2);i = i + 1)begin

din = $random;

din_sop = (i==0) ?1:0;

din_eop = (i==(len+1))?1:0;

din_vld = 1;

din_err = 0;

#(CYCLE*1);//需要根据实际情况,放到for循环末尾或者最开始

end

使用random生成随机数,关键在于如何生成指定范围内的随机数,上述代码提供了较好的思路:

- 例如生成随机数,要求范围在n~m

- 计算偏移后从0开始的范围,即0~m-n

- 生成随机数len,对m-n+1取余,则len的范围就在0-m-n

- len+n的范围就是n~m,符合要求

6.2.2 random语句产生随机概率

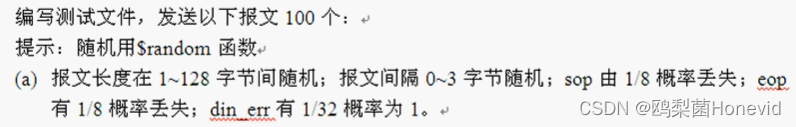

- 题目要求

- 含random语句产生随机概率的代码

//之前要先定义一个integer i和长度变量,设置长度符合题目条件

integer i;

integer J;

reg[2:0] sop_rand;

reg[2:0] eop_rand;

reg[4:0] err_rand;

reg[6:0] len_rand;

reg[1:0] gap_rand;

initial begin

//赋初值

din = 0;

din_sop = 0;

din_eop = 0;

din_vld = 0;

din_err = 0;

#(CYCLE*RST_TIME);

#(10*CYCLE);

for(j=0;j<100;j=j+1)begin

sop_rand = $random;

eop_rand = $random;

err_rand = $random;

//对len_rand长度变量进行规约

len_rand = $random;

//for赋值语句开始

for(i = 0;i < (len_rand+1);i = i + 1)begin

din = $random;

din_sop = (i==0 && sop_rand != 0) ? 1:0;

din_eop = (i==len_rand && eop_rand != 0) ? 1:0;

din_vld = 1;

din_err = (i==len_rand && err_rand != 0) ? 1:0;

#(CYCLE*1);//需要根据实际情况,放到for循环末尾或者最开始

end

din = 0;

din_sop = 0;

din_eop = 0;

din_vld = 0;

din_err = 0;

gap_rand = $random;

for(i=0;i<gap_rand;i=i+1)begin

#(CYCLE*1)

end

end

end

6.3 总结

注意

- for和random语句只能在测试文件中使用,设计文件中禁止使用

文章来源:https://blog.csdn.net/qq_48035645/article/details/135589483

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- test-02-test case generate 测试用例生成 EvoSuite 介绍

- ooTD I 撞色插肩长T真的怎么搭都好看

- 【亲测可行】如何申请并登录腾讯云免费服务器

- GO 的那些 IDE

- linux tar打包压缩命令学习

- vmware虚拟机不显示网络图标没有网络解决办法

- 高德地图添加marker、删除marker和点击marker里面的heml按钮

- 概率论与数理统计(期末复习)

- ANSYS Workbench注意事项

- 抖店的经营需要注意什么?时间在哪结果就在哪,新手做店必看教程