FPGA四选一的多路选择器(用三元运算符?:解决)

发布时间:2024年01月15日

? ? ?一.?三元运算符? :用法

?????? ?:符号通常用于条件运算符,表示条件判断。它类似于C语言中的三元运算符,用于根据条件选择不同的操作或值。

????????例如,在Verilog中,条件运算符?:可以用于if-else语句的简写形式。它的一般语法格式如下:

表达式 ? 结果1 : 结果2

????????如果表达式为真,则结果为结果1;否则结果为结果2。

在FPGA设计中,这种条件运算符通常用于逻辑电路的组合和时序逻辑设计。通过使用条件运算符,可以根据不同的条件选择不同的信号路径或值,从而实现更灵活和高效的逻辑功能。

????????需要注意的是,在FPGA设计中,条件运算符?:的具体实现方式可能因不同的硬件平台和编译器而有所不同。因此,在实际应用中,需要根据具体的硬件资源和设计要求选择合适的条件运算符或替代方案,并进行相应的优化和调整。

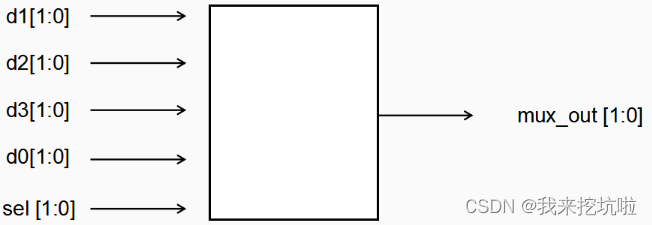

二.题目描述

????????制作一个四选一的多路选择器,要求输出定义上为线网类型

状态转换:

d0????11

d1????10

d2????01

d3????00

三.信号示意图

?四.波形示意图

五.代码

`timescale 1ns/1ns

module mux4_1(

input wire [1:0]d1,d2,d3,d0,

input wire [1:0]sel,

output wire[1:0]mux_out

);

assign mux_out = sel == 0 ? d3 : sel == 1 ? d2 : sel == 2 ? d1 : d0 ;

endmodule?六.前仿真代码

`timescale 1ns/1ns

module testbench();

reg clk=0;

always #5 clk = ~clk; // Create clock with period=10

//initial `probe_start; // Start the timing diagram

// A testbench

reg [1:0]d1=0;

reg [1:0]d2=0;

reg [1:0]d3=0;

reg [1:0]d0=0;

reg [1:0]sel=0;

wire [1:0]mux_out;

initial begin

d1 <= 0;

d2 <= 1;

d3 <= 2;

d0 <= 3;

#10

sel <= 0;

#10

sel <= 1;

#10

sel <= 2;

#10

sel <= 3;

#50 $finish; //stoprunning

end

//Sub-modules

mux4_1 m1(

.d0(d0),

.d1(d1),

.d2(d2),

.d3(d3),

.sel(sel),

.mux_out(mux_out)

);

initial begin

$dumpfile("out.vcd");

// This will dump all signal, which may not be useful

//$dumpvars;

// dumping only this module

//$dumpvars(1, testbench);

// dumping only these variable

// the first number (level) is actually useless

$dumpvars(0, testbench);

end

endmodule

文章来源:https://blog.csdn.net/weixin_66634995/article/details/135595386

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- Mybatis使用详解

- 一张三通道的图片的tensor类型的数据的标准差和平均值的计算,为Normalize()函数的归一化做准备

- Instagram账号被封?必须了解的原因与防封技巧

- 真是一场酣畅淋漓的程序员Citywork!

- SSA-CNN-SVM麻雀算法优化卷积神经网络支持向量机回归预测,多变量输入模型,要求2019及以上版本。2.评价指标包括: R2、MAE、RMSE和MAPE等,代码质量极高,方便学习和替换数

- 技术变革与裁员潮下程序员的挑战与应对策略

- export: `=/usr/local/jdk1.8/jre‘: not a valid identifier解决办法

- 实现 TS 内置的 Pick<T, K>

- C++学习笔记(三十五):c++ 函数指针及lambda表达式

- 山海鲸开发者揭秘:智慧工厂如何推动制造业实现质的飞跃