汽车ECU的虚拟化技术初探(四)--U2A内存管理

目录

1.内存管理概述

为了讲清楚U2A 在各种运行模式、特权模式下的区别,其实首先应该搞清楚不同模式下可以操作的寄存器有哪些。

但是看到这个寄存器模型就头大。

再加上之前没有研究过G4MH的内核,所以这里暂且留个坑。

我们还是来看看继续往下看,先来看看内存管理。

U2A是没有MMU的,那么它是如何实现虚拟化所需要的MMU机制的呢?

MPU,大家见得多了,memory protection unit,用于防止未授信程序、突发异常事件等访问系统资源,来保证整个MCU的正常运行。

在U2A的虚拟化模式中,MPU还被细分成了三个块内容,如下:

- Layered Memory Protection

2. 内存保护功能

我们这里先来看看功能安全,44章节功能安全 44.5 memory protection,了解常规模式下面memory protection的功能。?

- Memory访问控制

????????通过设置保护区域的上下边界进行访问控制

- CPU运行模式的访问管理

????????通过CPU中的几个状态位用于控制对资源的访问,并且根据每个程序的可靠性级别,将这些位组合使用以执行适当的保护

- 通过SPID进行保护

????????使用SPID (system protection identifier)来检查区域是否匹配。

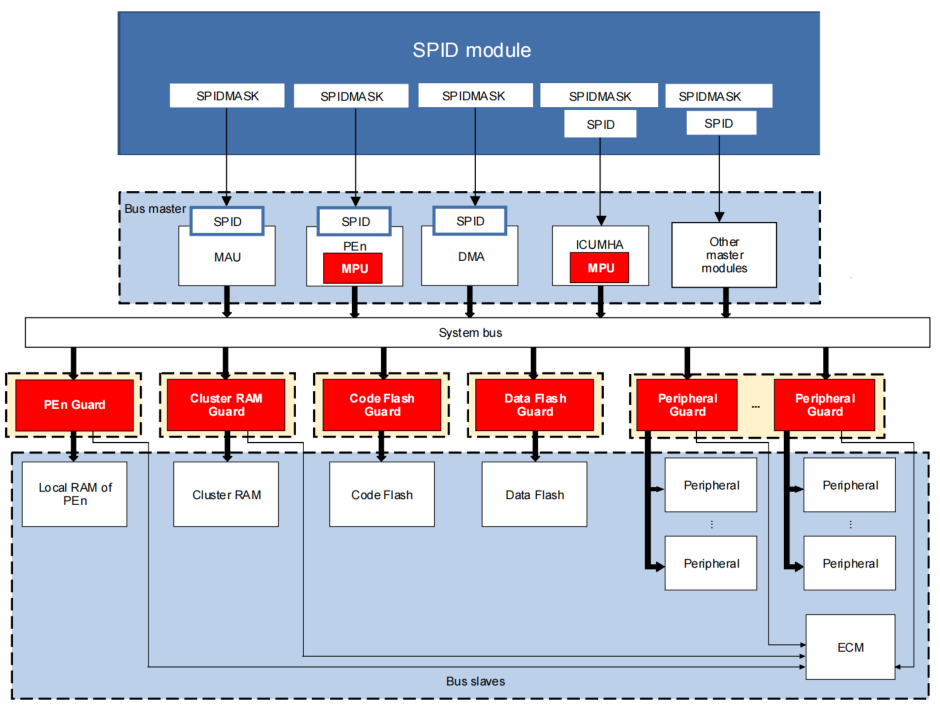

根据芯片手册介绍,Memory Protection整体架构如下:

该内存保护架构由几部分组成:SPID模块、每个核里的MPU、外设的Slave Guard以及memory的Slave Guard。

- MPU:所有CPU均通过MPU进行访问权限控制,它们不会发起访问MPU禁止的地址的相关请求;

- Slave Guard:在总线层面上保护指定的memory或者外设,防止未授权访问;可以看到针对不同外设、memory有不同的guard。例如PE Guard(针对CPU内部RAM的保护)、CRG(针对Cluaster RAM保护)、针对外设的PG。

- SPID:System Protection identifier,是一种软件任务的标识符,它分两种情况:一种主机内部自带SPID寄存器,可以直接配置,例如DMA、CPU(也叫PE,proces element);另一种是在SPID模块里配置。

2.1 SPID

我们首先来看SPID,有如下功能:

- 每个总线主机的SPID可以软件灵活配置;

- 一个SPID可以分配给一个主机或者多个主机

- 通过SPIDMASK来限制主机的使用

- SPID的配置可以上锁,冷复位或系统复位解锁,就和英飞凌SMU一样,配好了就锁住。

那么具体应该怎么使用呢?先看框图:

SPID寄存器用于配置bus master,比较分散的是,CPU、DTS/DMAC和MAU等主机的SPID寄存器配置是在自己模块内部配置,如Gb Ether等SPID值的配置就是在在SPID模块内部,如上图所示。

首先我们来看总共有多少个寄存器可以用于配置SPID。我们继续来看示例:

在默认情况下,每一个Bus Master的SPID值如下:

注意,最左侧这一列就相当于给主机分配一个ID值,这个与英飞凌TC3xx固定Master Tag ID还是有所区别。从上图我们可以看到,在U2A中作为master看待的外设、内核总计15个,总计32个寄存器可以配置ID值,默认状态下Reserved的是4-16、18、20、21、30共计17个寄存器,

但是可不可以把这些reserved分配给其他同一个主机呢,答案是肯定的,如下:

进一步,可不可以把一个SPID分配给多个外设呢,当然也是可以的,如下图:

上图中,RHSIF0\FlexRay\Ether均使用了24这个SPID,CPU2占据了FlexRay1 22这个SPID。

?那么要给Bus Master分配 SPID,需要按照如下步骤:

- 设置SPIDKCPROT寄存器使能SPID寄存器配置功能;

- 设置SPID掩码寄存器(BMnSPIDMSK)定义每个bus master可以定义的SPID值

- 设置SPID掩码锁存寄存器保证SPID掩码寄存器不被修改;

- 根据SPID掩码寄存器设置SPID寄存器的值;

- 设置SPIDKCPROT寄存器关闭SPID寄存器配置功能;

- 配置内存保护/保护设置,以防止由SPID和其他标识符识别的错误访问。

那么配置了SPID,是不是就可以保证访问限制。不然,还需要Slave Guard的配置。

2.2?Slave Guard

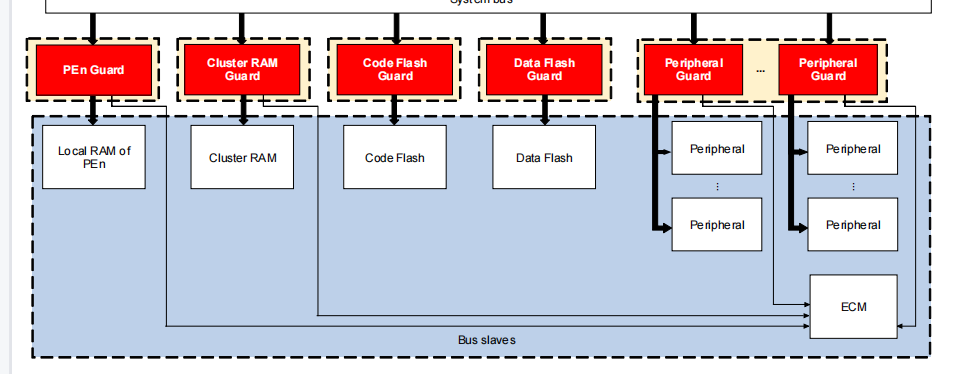

从系统架构图,我们可以看到不同种类的Guard Type。

- PEG

PE Guard,用于每个PE(Process Element)控制Local RAM和INTC1是否可以被其他bus master访问

- CRG

Cluster RAM Guard,用于 Inter-VM 通信或者Cluster RAM的访问

- PG

Peripheral Guard,用于保护外设访问保护

那么需要slave guard属性配置如下:

| 优先级 | 保护属性 | 内容 |

| High | SEC | 使能后,禁止non-secure主机访问 |

| ... | DBG | 使能后,允许debug主机访问目标slave |

| ↓ | UM | 该属性关闭后,user mode下所有主机都不能访问slave |

| SPID[m] | 使能后,与该slave定义的SPID相等的master SPID就可访问该slave | |

| WG | 使能后,master就可以写目标slave | |

| Low | RG | 使能后,master就可以读目标slave |

?具体每个Slave Guard我们后面再讲。

3.小结

可以看到,U2A的内存保护设计还是很灵活的,目前在用法上仅仅使用了MPU。

后续如果有用到SPID了,我再详细描述。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- NFS的介绍与管理

- 系列三十三、如何将一个springboot jar做成批处理文件

- 了解EMI滤波器:从基础到应用?|深圳比创达电子

- Everything-一切尽在掌握之中

- 关于链表去重的操作

- U-Boot学习(2):U-Boot编译和.config配置文件生成分析

- 【Jenkins】远程API接口介绍

- 寒假作业(蓝桥杯2016年省赛C++ A组第6题)

- 李沐《动手学深度学习》线性神经网络 softmax回归

- 5分钟搭建属于你个人的chatgpt网站,申请内测API-key,chatgpt