【USTC】verilog 习题练习 36-40

36??条件运算符

题目描述

Verilog中有一个跟C语言中类似的三目条件运算符( ? : ),其语法格式为:

(condition ? if_true : if_false)

该表达式可以用于为其它信号赋值,例如:signal = condition ? if_true : if_false;

该语句等同于:

if(condition)? signal = if_true;

else???????? signal = if_false;

因涉及到3个操作数,并且能实现条件运算的功能,因此称为三目条件运算符。

下面是几个使用该运算符的例子:

(0 ? 3 : 5)???? // 条件为假,因此表达式的值为5

(sel ? b : a)?? ?// 二选一选择器

always @(posedge clk)???????? // 触发器

? q <= toggle ? ~q : q;

always @(*)?????????????????? // 有限状态机(FSM)

? case (state)

??? A: next = w ? B : A;

??? B: next = w ? A : B;

? endcase

assign out = ena ? q : 1'bz;? // 三态门

((sel[1:0] == 2'h0) ? a : (sel[1:0] == 2'h1) ? b : c ) //嵌套使用

试设计一计算最小值功能的Verilog模块,给定四个无符号数,求最小值。提示:

1. 可以综合使用比较运算符(< or >)和条件运算符(? :)。

2. 有必要的话,可以定义中心变量

输入格式

8bit a,b,c,d

输出格式

8bit min, 为 a,b,c,d的最小值

module top_module (

input [7:0] a, b, c, d,

output [7:0] min

);

wire [7:0] min1,min2,min3;

assign min1 = ( a > b ) ? b : a;

assign min2 = ( c > d ) ? d : c;

assign min3 = ( min1 > min2 ) ? min2 : min1;

assign min = min3;

endmodule37?归约运算符

题目描述

您已经熟悉了两个值之间的位运算,例如a&b或a^b。有时,您需要创建一个对一个向量的所有位进行操作的逻辑门,如(a[0]&a[1]&a[2]&a[3]…),如果向量很长的话,也会很麻烦。归约运算符可以对向量的位进行AND、OR和XOR运算,产生一位输出:

& a[3:0] // AND: a[3]&a[2]&a[1]&a[0]. Equivalent to (a[3:0] == 4'hf)

| b[3:0] // OR: b[3]|b[2]|b[1]|b[0]. Equivalent to (b[3:0] != 4'h0)

^ c[2:0] // XOR: c[2]^c[1]^c[0]

这些是只有一个操作数的单目运算符(类似于NOT运算符!和~)。您还可以反转这些门的输出来创建NAND、NOR和XNOR门,例如(~&d[7:0])。

当传输数据使用的是一个不完美的渠道时,经常使用奇偶校验作为一种简单的方法来检测错误。创建一个将为8位字节计算奇偶校验位的电路(这将在字节中添加第9位)。我们将使用“偶数”奇偶校验,其中奇偶校验位只是所有8个数据位的异或。

那么,让我们进入正题:

输入格式

8位输入信号in

输出格式

1位输出信号parity=^in,可以直接通过归约运算符完成。 是的,你没有看错,真的有用的题干大概就这么一句……

module top_module (

input [7:0] in,

output parity);

assign parity = ^in;

endmodule38?D触发器

题目描述

D触发器是一种在时钟信号的边缘(通常是上升沿)存储位并定期更新的电路。在Verilog中,时序逻辑电路描述(一般语法为:always@(posedge clk))都会生成组合逻辑块加D触发器的电路结构。

D触发器是最简单的“组合逻辑后跟一个触发器”形式,其中组合逻辑部分只是一根导线。

创建verilog模块,实现一个D触发器。

输入格式

时钟clk,1位的d

输出格式

1位的q

module top_module (

input clk, // Clocks are used in sequential circuits

input d,

output reg q );//

// Use a clocked always block

// copy d to q at every positive edge of clk

// Clocked always blocks should use non-blocking assignments

always @(posedge clk) begin

q <= d;

end

endmodule39?寄存器

题目描述

寄存器在本质上来说就是触发器,我们一般将由多个触发器构成的向量信号成为寄存器。试设计一个在时钟上升沿出发的8bit位宽的寄存器。

输入格式

一位宽线网型变量clk,时钟信号; 八位宽线网型变量d,寄存器输入信号;

输出格式

八位宽寄存器型变量q,寄存器输出信号

module top_module (

input clk,

input [7:0] d,

output reg [7:0] q

);

// 请用户在下方编辑代码

always @(posedge clk) begin

q <= d;

end

//用户编辑到此为止

endmodule

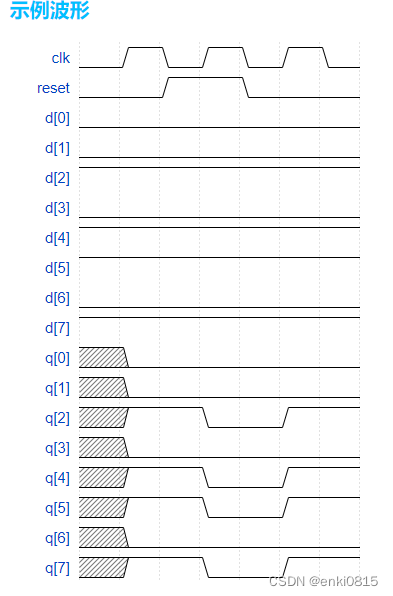

40?有复位功能的寄存器

题目描述

创建一个带有复位信号(reset)的8bit位宽的寄存器,在触发信号(clk)的上升沿,当复位信号为高电平时,寄存器输出0,否则与输入信号d同步。

Hint:

在同一个always进程块中,同一触发信号只能使用一种边沿,即上升沿和下降沿不可同时使用。(例如:always@(posedge clk or negedge clk),这种写法是错误的)

输入格式

时钟信号clk, 同步复位信号reset, 8bit宽信号输入d

输出格式

8bit宽信号输出q

module top_module (

input clk,

input reset, // Synchronous reset

input [7:0] d,

output reg [7:0] q

);

//your code

always @(posedge clk) begin

if (reset) begin

q <= 8'b0;

end else begin

q <= d;

end

end

endmodule本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!