MCU FT61F14x入门

目录

前言

??FT61F14x是辉芒微电子的微控制器,是一款8位基于EEPROM的RISC MCU。官方提供CMIDE3.0.9可用于编译调试,本文主要讲解其开发环境及部分外设使用,资源见附件。官网链接:https://www.fremontmicro.com/#/home

一、CMIDE的使用

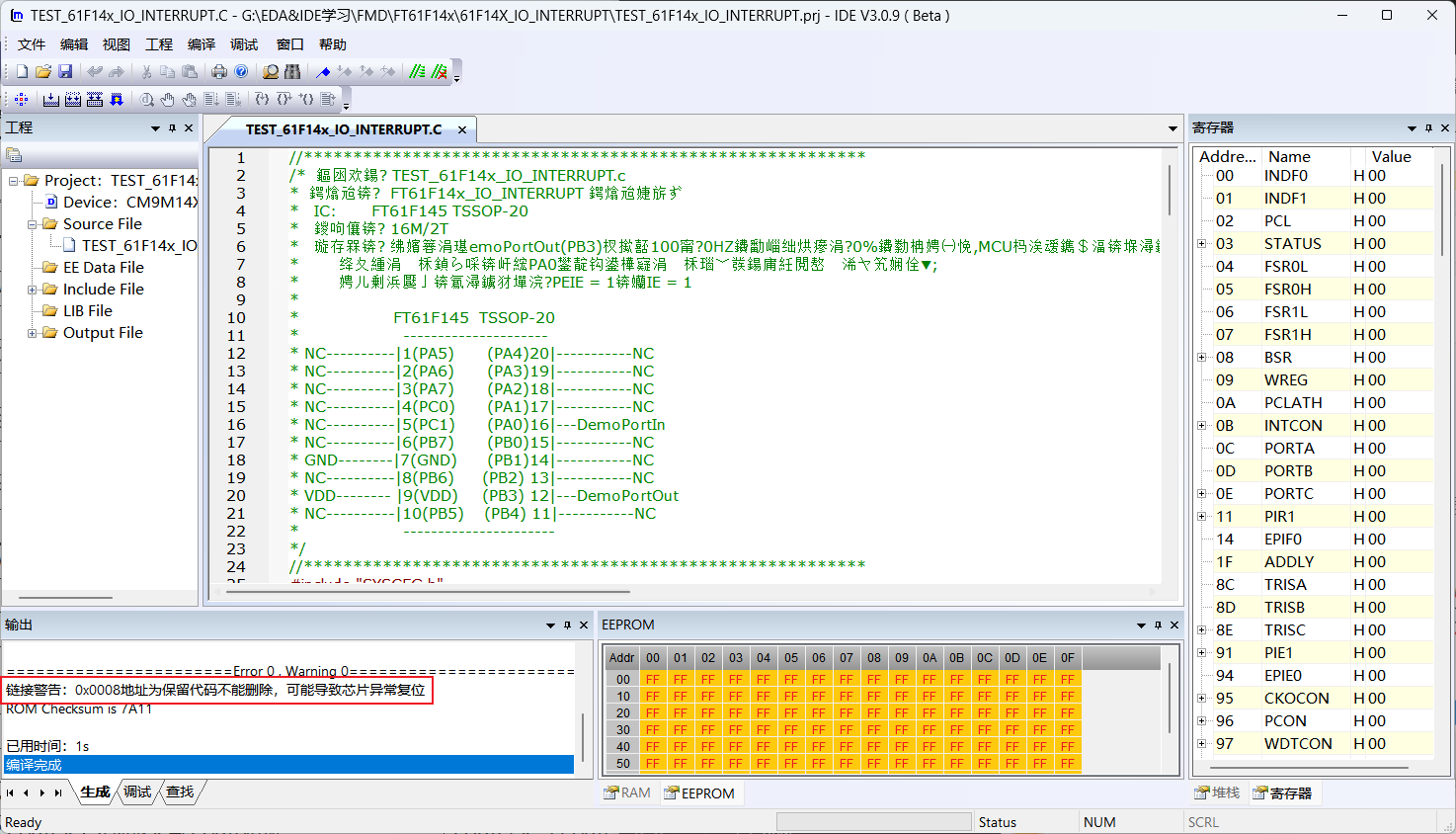

??首先需要新建工程,直接编写并编译可能会出现以下链接警告

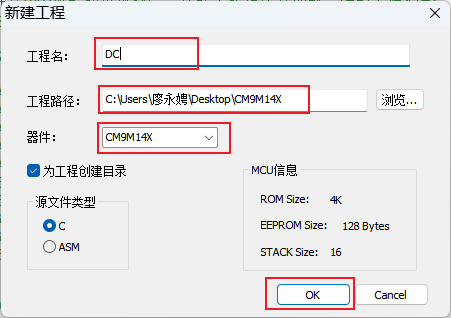

??点击工程->新建工程,设置工程名以及工程路径,然后选择相应的芯片类型,最后点击OK就可以一键生成工程

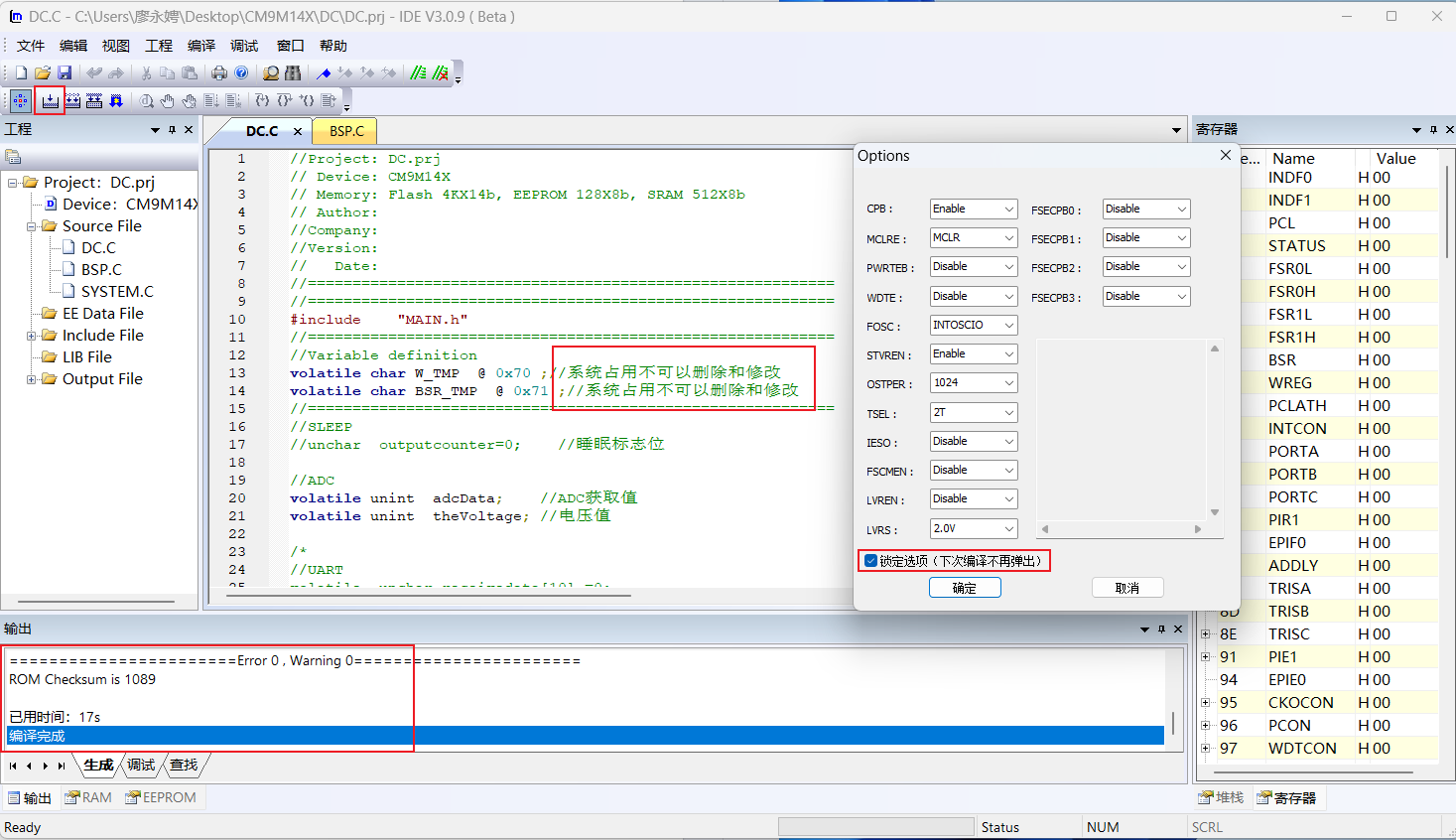

??对生成工程直接点击编译,弹出Options选项配置,可以按照下图修改,点确定便可编译成功。

注意:提示系统占用不可以删除和修改的地方,不要删除,否则会提示链接报警

二、系统时钟与睡眠

2.1 上电复位 (POR)与系统复位

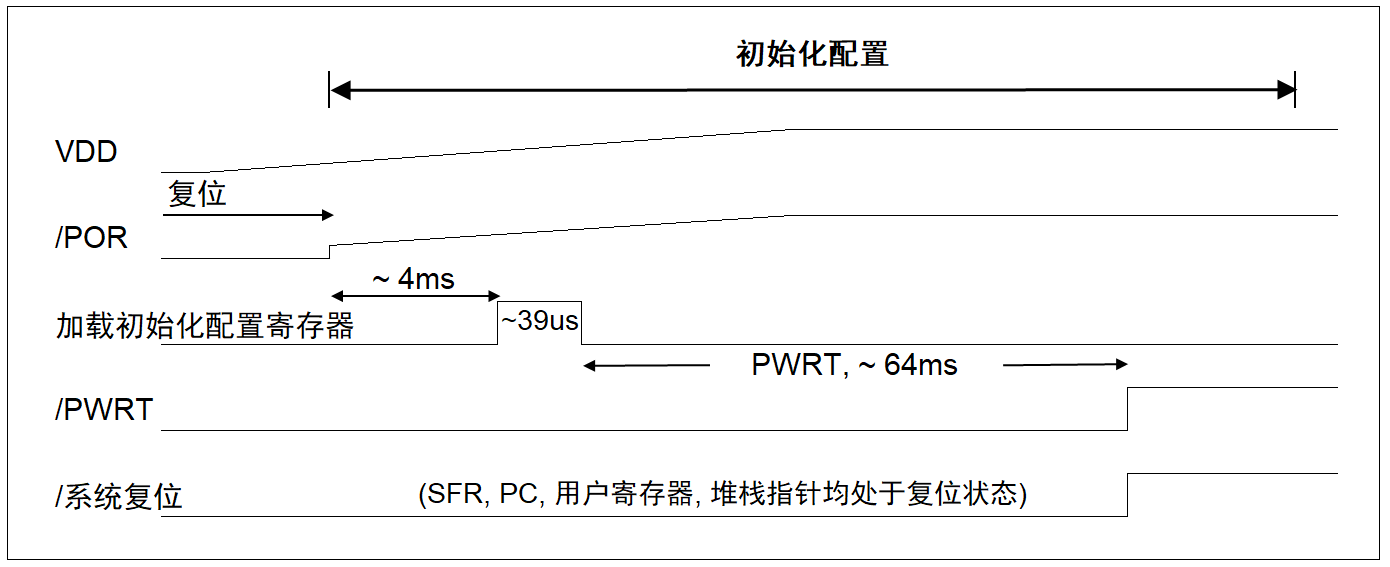

??上电过程,即 VDD 从低于 Power-On-Reset 电压(VPOR)上升至高于 VPOR 的过程。当 CPU 重新上电时,VDD 可能没有完全掉电至 0V。初始化配置由CMIDE 界面设置,不能通过指令修改。初始化配置时序如下:

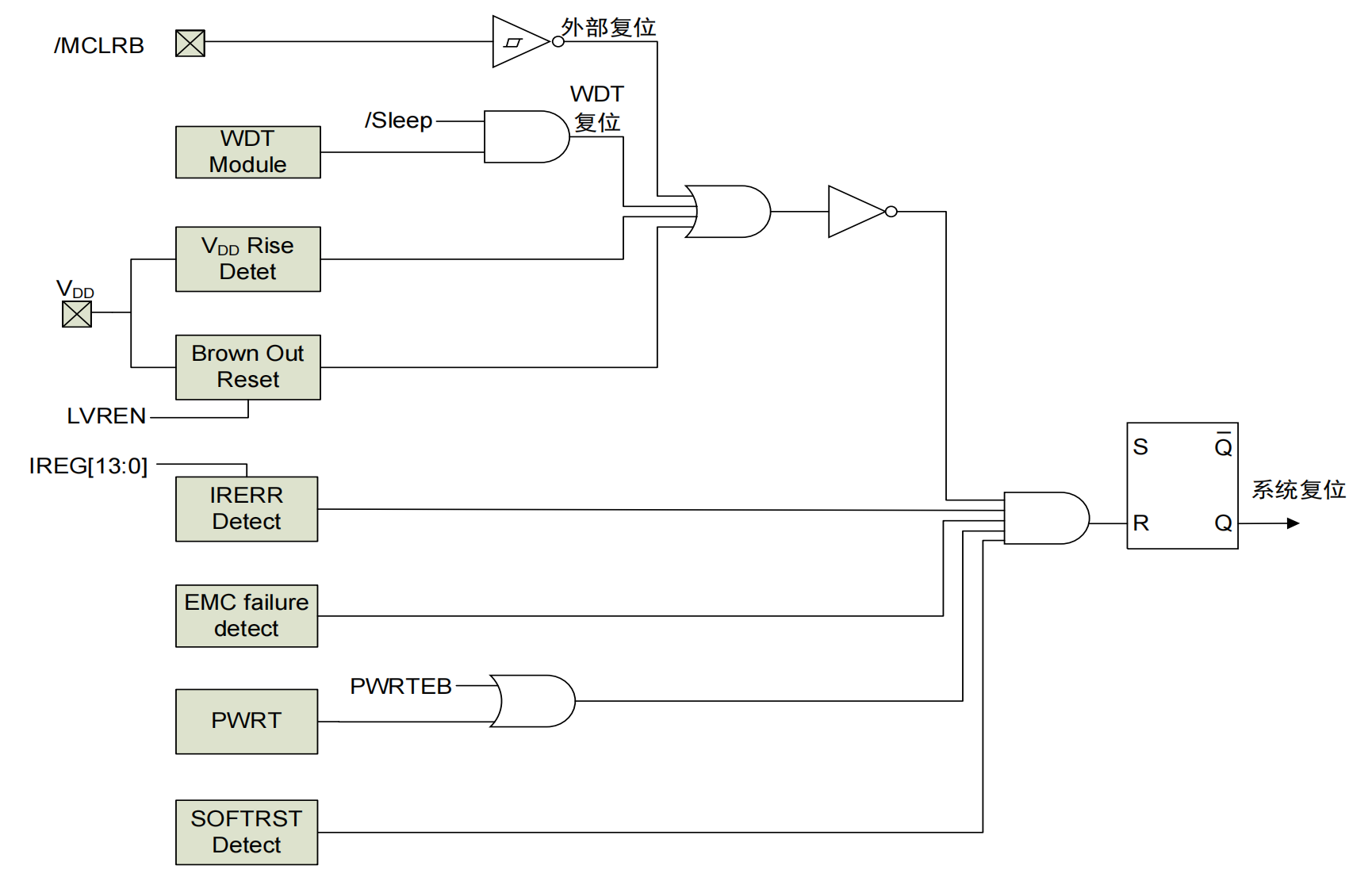

??与 POR 不同,系统复位(system reset) 并不会完全复位。系统复位时,CPU 是否启动初始化配置过程则取决于复位触发类型。若启动初始化配置则空闲等待4ms,然后重新加载初始化配置寄存器值,如果使能 PWRT 将额外延时64ms,随后系统正常启动。在系统复位中:

- 除初始化配置寄存器外,POR 过程中被重置的寄存器在系统复位时也会被同样重置;

- 程序计数器 PC = 0x00, 指令寄存器 = “NOP”, 堆栈指针 = “TOS” (栈顶);

??除仿真调试的 OCD(On-Chip Debugger) 模块外,以下 7 种事件可触发系统复位:

- 欠压复位 (BOR / LVR) – 总会启动初始化配置;

- 非法指令复位;

- 看门狗复位 (WDT,CPU 处于非 SLEEP 状态);

- EMC 复位– 总会启动初始化配置;

- 软件复位 (执行指令 “RESET”);

- 堆栈溢出复位 (上溢或下溢);

- 外部 I/O 复位 (/MCLRB) – 总会启动初始化配置 ( ≥ VerB 芯片)。

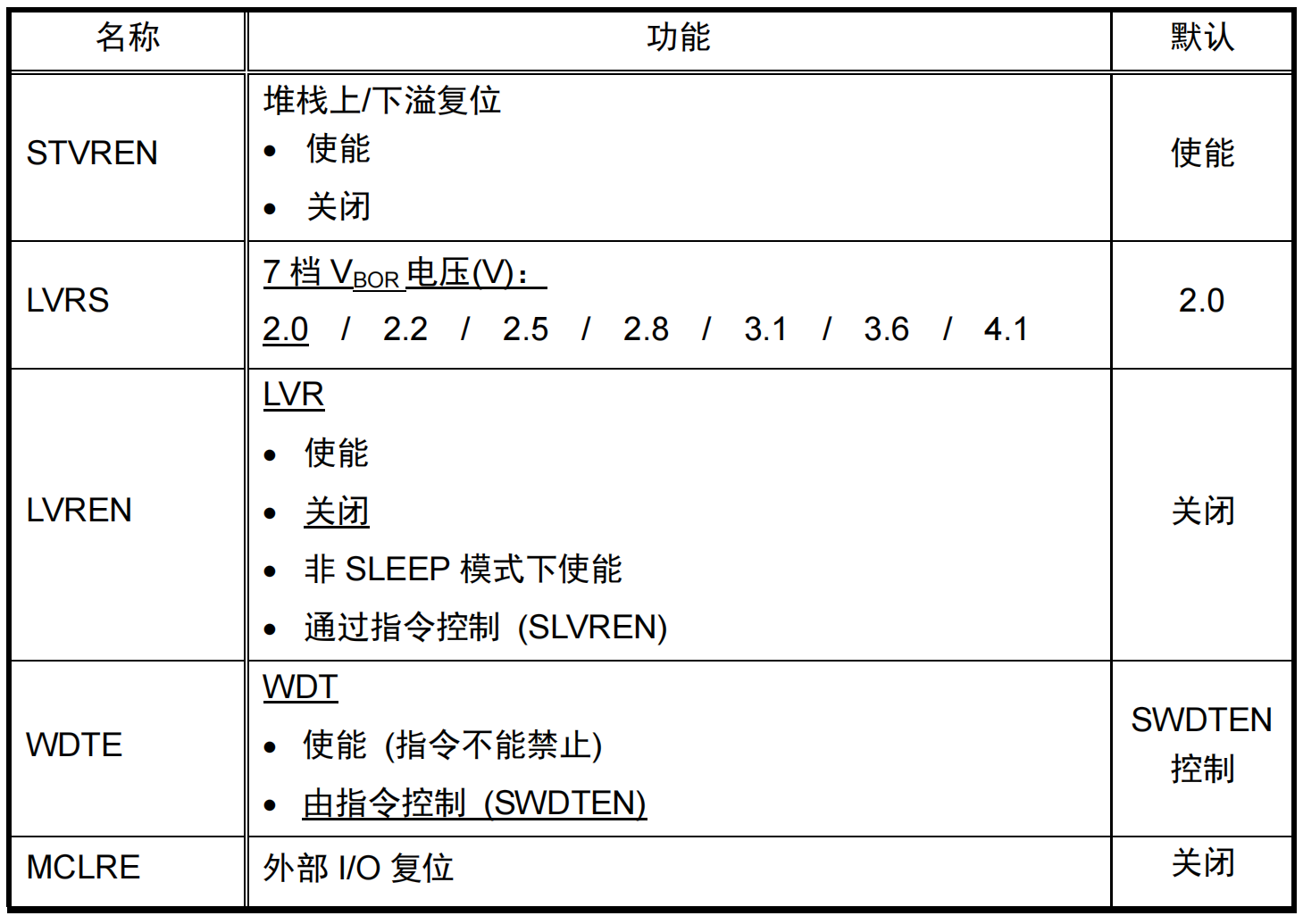

??系统复位的大多数设置均由 IDE 界面配置,而不能通过指令修改。系统复位相关寄存器汇总:

2.2 振荡器和系统时钟

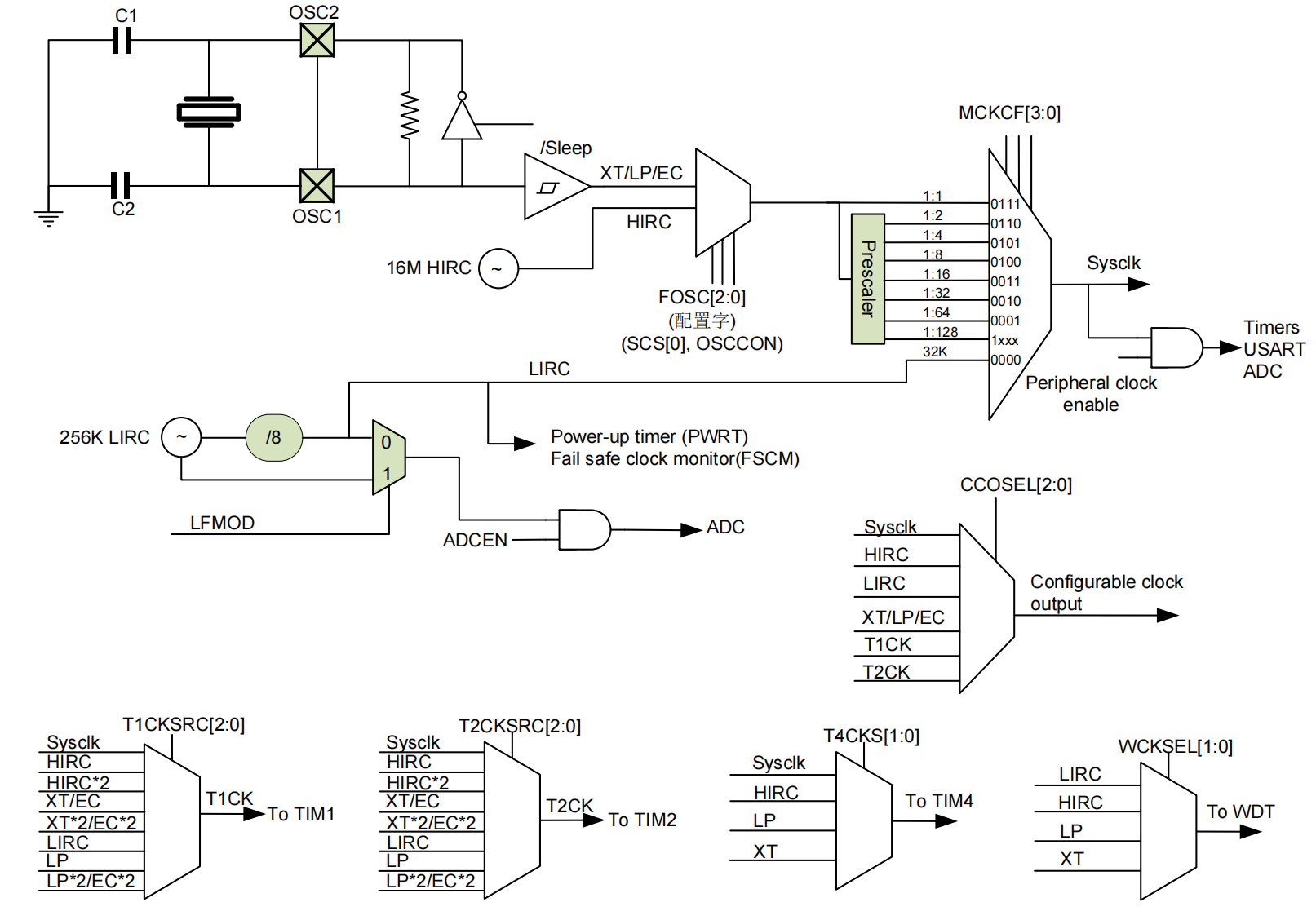

??系统时钟(SysClk) 可通过指令选择为内部高速振荡器 HIRC 16MHz,内部低速振荡器 LIRC 32KHz,或外部振荡器。如果选择外部振荡器,那么由初始化配置寄存器 “FOSC”选定3 种外部振荡器之一。系统时钟还可通过指令进一步选择为内部或外部振荡器的分频 。系统时钟用于产生指令时钟(Instruction Clock):

????????指令时钟 = SysClk / N ; N = 2 for 2T, 4 for 4T

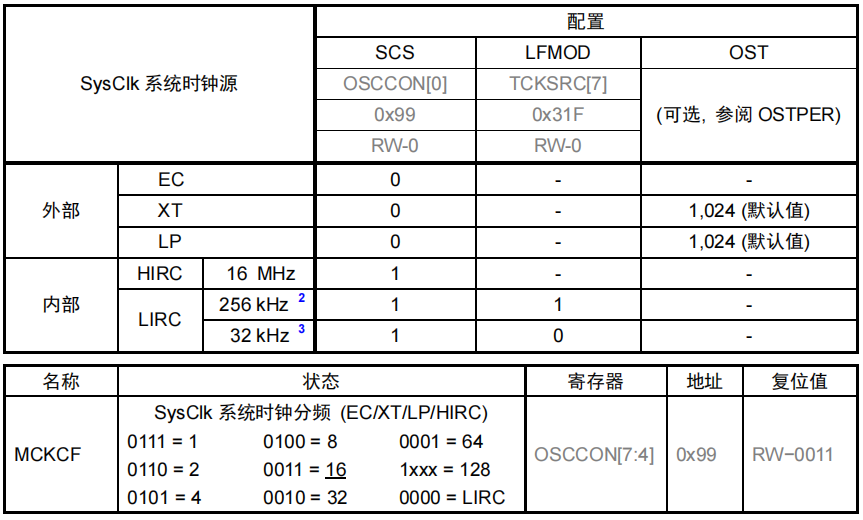

??SysClk 系统时钟源设置相关用户寄存器:

??通常我们选择内部时钟即SCS=1,不分频即MCKCF=0111,使用OSCCON寄存器如下(SCS为OSCCON的BIT0位设置):

OSCCON = 0B01110001; //WDT 32KHZ IRCF=111=16MHZ

//Bit0=1,系统时钟为内部振荡器

//Bit0=0,时钟源由FOSC<2:0>决定即编译选项时选择

2.3 SLEEP睡眠模式 (POWER-DOWN)

??睡眠模式下,指令时钟关闭,指令执行停止,大多数模块掉电以降低功耗。除指令时钟外,其他模块可根据需求在 SLEEP 模式下保持运行:

??SLEEP示例:

SLEEP(); //SYSCFG.h里定义#define SLEEP() asm("sleep")

NOP(); // 中断方式唤醒

??从睡眠中唤醒有 2 个基本原则:

- 基于时间,即 CPU 在一定的时间后醒来。建议选择 LIRC 作为计时的时钟源,因为 LIRC 比 HIRC的功耗更低。

- 基于事件,即触发 POR,系统复位,仅唤醒而不产生中断,以及产生中断的事件,如 LVD,ADC,EEPROM 写完成,外部管脚中断。

注意:

- 如果在执行 SLEEP 指令之前发生中断(中断标志位置 1 且其中断使能,但全局中断 GIE 禁止),则SLEEP 指令将作为 NOP 执行,不会进入睡眠模式。

- 由于同步延时,将中断标志位清 0 之后,至少要等两条指令才可以执行 SLEEP 指令,否则不会进入睡眠模式。

- 从睡眠中唤醒将清零 WDT。

- 使用中断方式从 SLEEP 中唤醒时,将先执行下一条指令,然后再调用中断服务程序。为了避免重复执行,建议紧跟 SLEEP 的后面写为 NOP 指令。

2.4 低电压检测/比较器 (LVD)

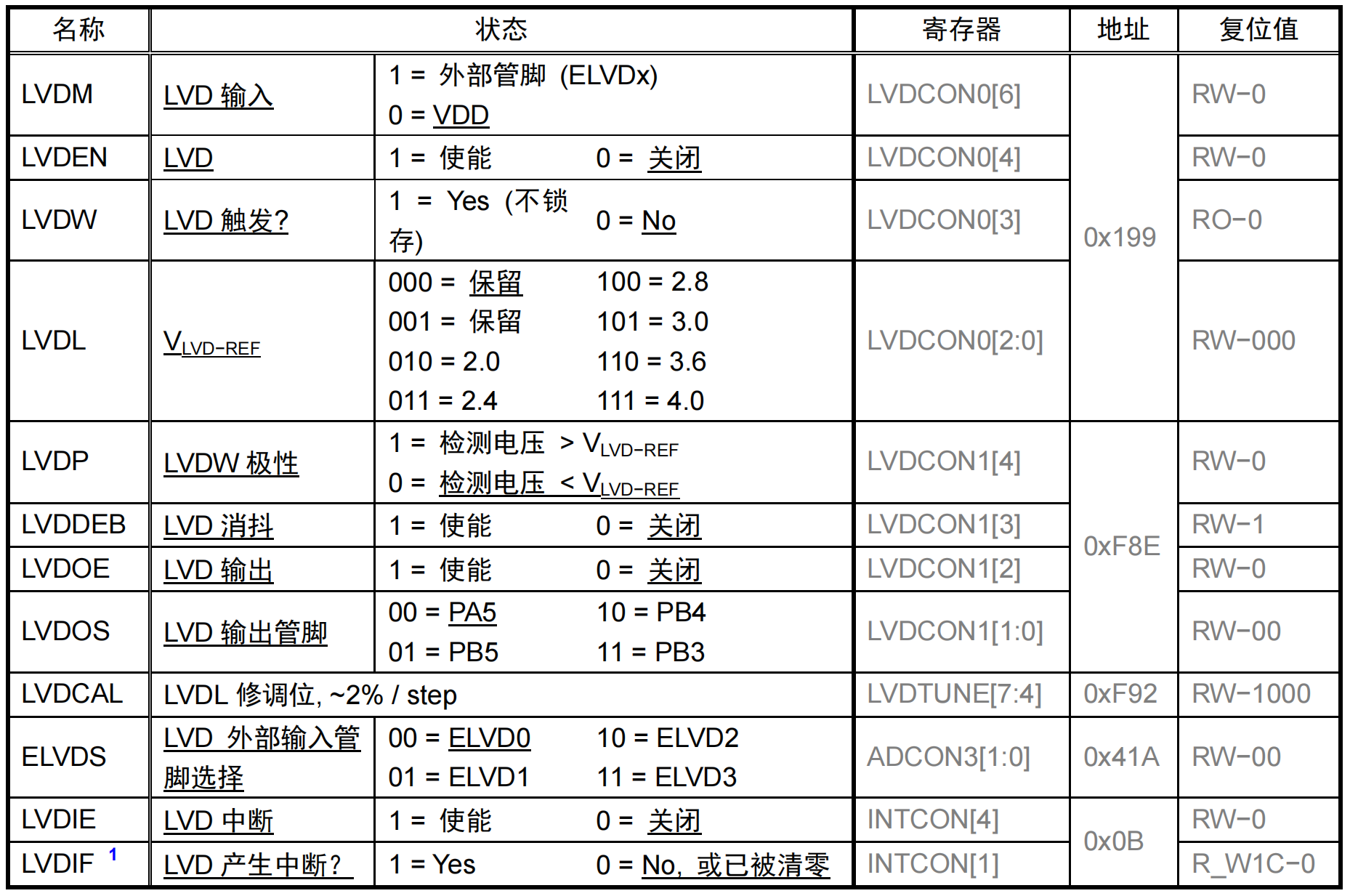

??LVD 的工作原理与LVR类似,但是所有控制位和参数选择位均由用户指令设置,而不是初始化配置时。LVD 相关寄存器汇总:

三、I/O端口与中断

四、串口USART

五、定时器

??

六、ADC

七、EEPROM

??

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- LINUX--基础IO

- 利用 Azure Data Bricks的免费资源学习云上大数据

- 深度学习在交通标志识别中的应用

- 使用HttpSession和过滤器实现一个简单的用户登录认证的功能

- GoZero微服务个人探究之路(二)Go-Zero官方api demo示例探究

- 机器学习——主成分分析(PCA)

- python的import功能,你需要了解的导入机制

- <软考高项备考>《论文专题 - 76 风险管理(8)》

- L1-077 大笨钟的心情(Java)

- HTS318 红外热释传感器处理芯片 PIR控制芯片 用于红外感应灯、走廊灯等