vivado编译设置、执行设置、bit流生成设置

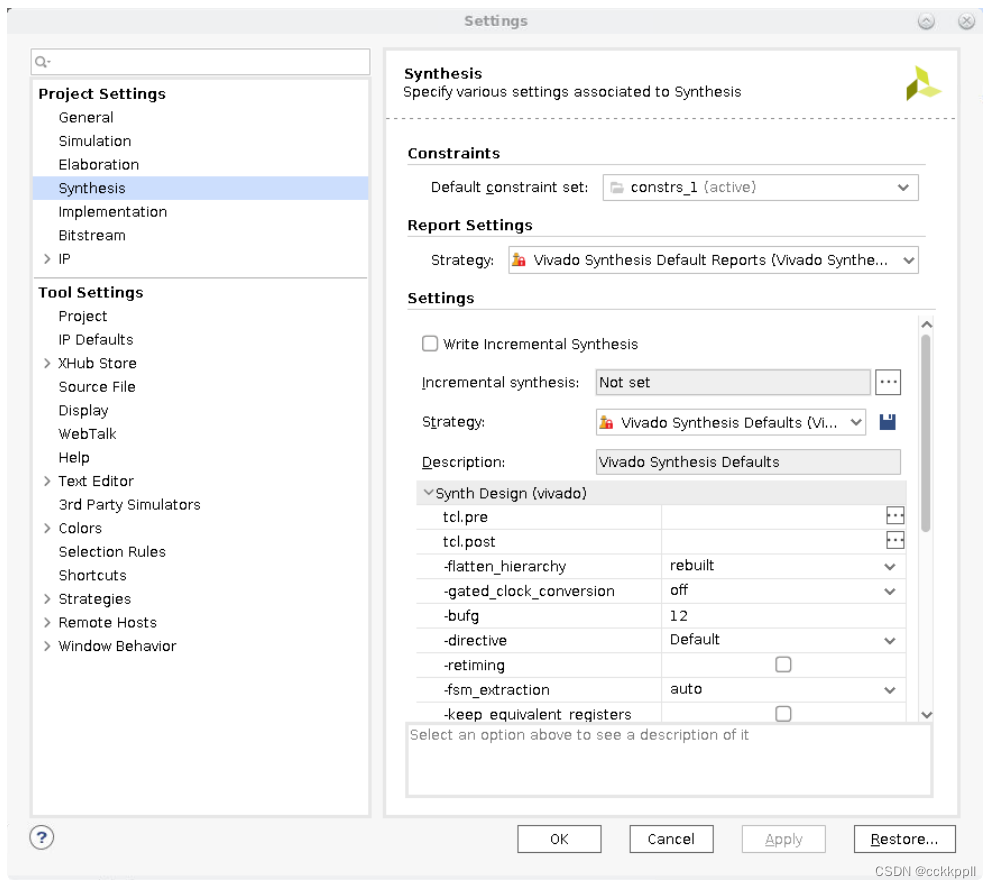

合成设置

使用“合成设置”可以指定约束集、合成策略、合成选项,以及要生成的报告。选项由选定的定义综合策略或综合报告策略,但您可以用自己的策略覆盖这些策略设置。您可以选择一个选项来查看对话框底部的描述。了解更多有关“合成设置”的信息,请参阅Vivado中的“使用模拟设置”部分设计套件用户指南:综合(UG901)。

注意:您可以在项目中预先合成IP,这会减少合成运行时间。有关的信息使用这种自下而上的综合流程,请参阅Vivado Design Suite用户指南:使用IP进行设计(UG896)。提示:您可以使用Tcl.pre和Tcl.post在合成之前和之后添加要来源的Tcl脚本文件夹。有关更多信息,请参阅Vivado Design Suite用户指南:使用Tcl脚本(UG894)。

实施设置

使用“实现设置”可以指定约束集、实现战略、实施选项以及要生成的报告。选项由定义所选的实施策略或实施报告策略,但您可以覆盖这些与您自己的设置。例如,可以使用选项运行可选步骤,例如功率优化和物理合成。您可以在中选择一个选项以查看描述对话框底部。有关“实施设置”的更多信息,请参阅自定义Vivado Design Suite中的实施策略用户指南:实施(UG904)。提示:您可以使用tcl.pre和tcl.post文件在每个阶段都可用。有关更多信息,请参阅Vivado DesignSuite用户指南:使用Tcl脚本(UG894)。

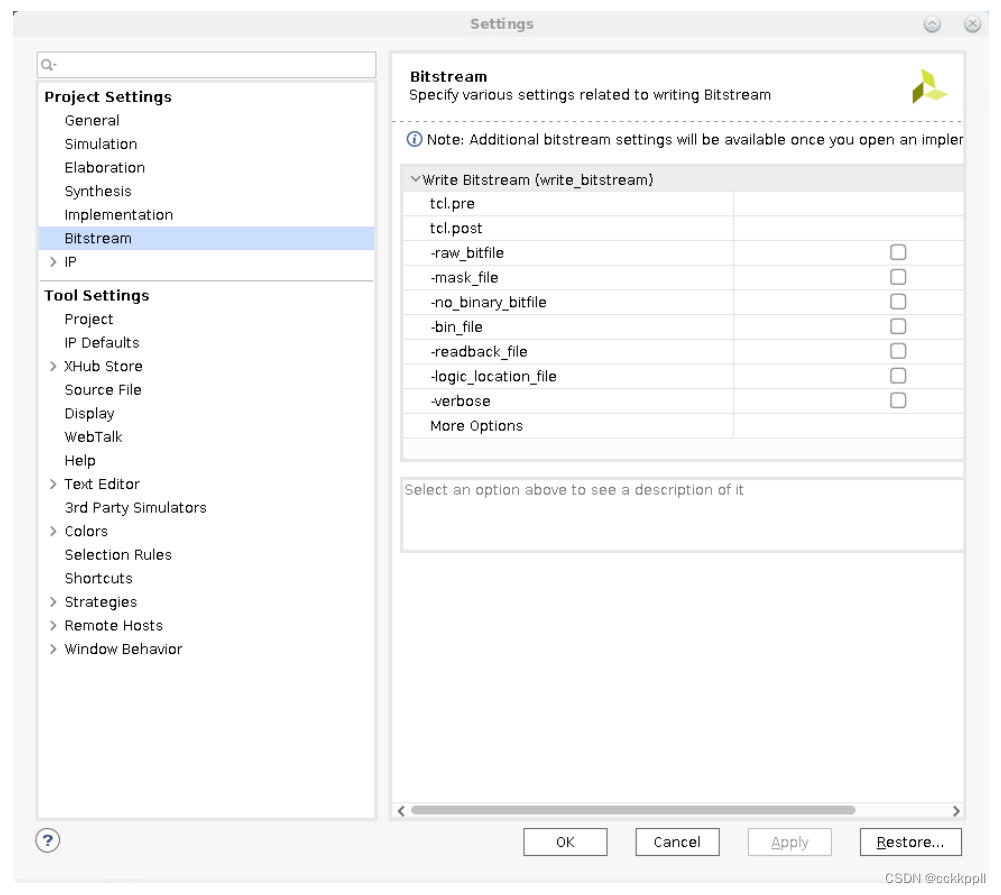

比特流设置

比特流设置使您能够在生成比特流之前定义选项。你可以选择一个选项可以在对话框底部查看说明。有关的更多信息关于比特流设置,请参阅Vivado中的“更改比特流文件格式设置”部分设计套件用户指南:编程和调试(UG908)。

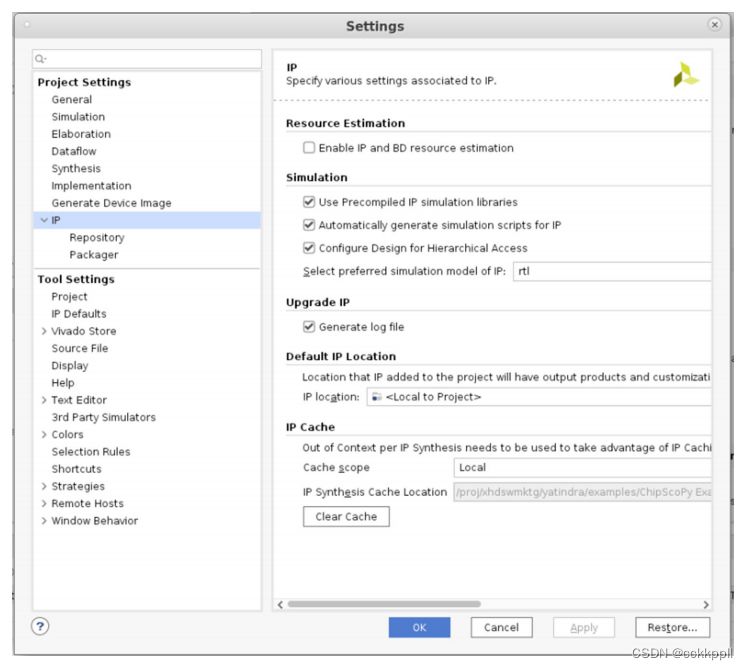

IP设置

IP设置包括以下小节:

?存储库:指定要添加到IP存储库列表中的目录。IP可以通过您或从第三方供应商处获得。单击“添加”添加存储库后,您可以请参阅每个存储库中的IP。

?Packager:设置打包新IP的默认值,包括供应商、库和分类法。此选项卡还允许您设置打开IP打包程序时的默认行为,并允许您可以指定要自动筛选的文件扩展名。

注意:如有必要,您可以在IP打包过程中更改打包IP的默认值。有关IP设置的更多信息,请参阅Vivado Design中的“使用IP设置”部分Suite用户指南:使用IP(UG896)进行设计。IP设置和Vivado IP目录仅在使用RTL项目或在使用“入门”页面中的“管理IP”时。使用管理IP时,IP的子集除非创建了项目,否则设置是可用的。

用于配置项目设置的Tcl命令

以下是用于为项目配置不同属性的相关Tcl命令。这个示例显示了如何为项目配置目标语言属性:

建议:您可以设置多个属性,包括项目或合成或实现运行。了解属性名称和目标的最佳方法是在中执行操作Vivado IDE,并在Tcl控制台中查看相应的Tcl命令。

使用Tcl脚本创建项目

您可以使用write_project_tcl命令生成一个tcl脚本,该脚本将重新创建当前项目。脚本将保留项目设置和源,但可能不会保留输出产品或设计状态。作为在Vivado IDE中创建项目的替代方案,您可以使用Tcl创建项目剧本Vivado IDE中运行的大多数操作都会导致执行Tcl命令。Tcl命令出现在Vivado IDE Tcl控制台中,也在Vivado.jou和vivado.log文件。vivado.jou文件只包含命令和vivado.log文件包含命令和任何返回的消息。您可以使用这些文件来开发脚本用于项目模式。请参阅Vivado Design Suite用户附录A中的输出文件指南:使用Vivado IDE(UG893)获取有关Vivado.jou和日志文件所在位置的信息书面的有关Tcl命令的更多信息,请参阅《Vivado Design Suite Tcl命令参考指南》(UG835)。以下是创建项目、添加各种源、配置设置的示例脚本,启动合成和实现运行,并创建一个比特流。

提示:您可以在Tcl脚本中使用行末尾的反斜杠(\)字符来分隔一行指示线路的延续。反斜杠后面的行作为前一行的一部分进行处理。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 前端数据结构与算法总结<week three>

- 机器视觉技术与应用实战(平均、高斯、水平prewitt、垂直prewitt、水平Sobel、垂直Sobel、拉普拉斯算子、锐化、中值滤波)

- Linux系统——yum有趣的玩法

- 教你如何确保服务器文件传输是安全的

- FaceNet: 人脸识别和聚类的统一嵌入

- vue整理面试题

- AI全栈大模型工程师(十六)智能体架构:Agent

- 软考网络工程师考试大纲(2018年最新版)

- Docker(三)使用 Docker 镜像

- 文件重命名:特殊符号影响你找文件吗?来看看这个解决方法