数字式竞赛抢答器Verilog代码Quartus软件AX301开发板

发布时间:2023年12月30日

名称:Quartus数字式竞赛抢答器Verilog代码AX301开发板(文末获取)

软件:Quartus

语言:Verilog

代码功能:数字式竞赛抢答器设计

设计一个可容纳四组参赛者同时抢答的数字抢答器

要求:(1)能断第一抢答者并报警指示抢答成功,其他组抢答均无效

(2)设计倒计时时钟,若提前抢答则对相应的抢答组发出警报。

本代码已在AX301开发板验证,开发板如下,其他开发板可以修改管脚适配:

1. 工程文件

2. 程序文件

3. 程序编译

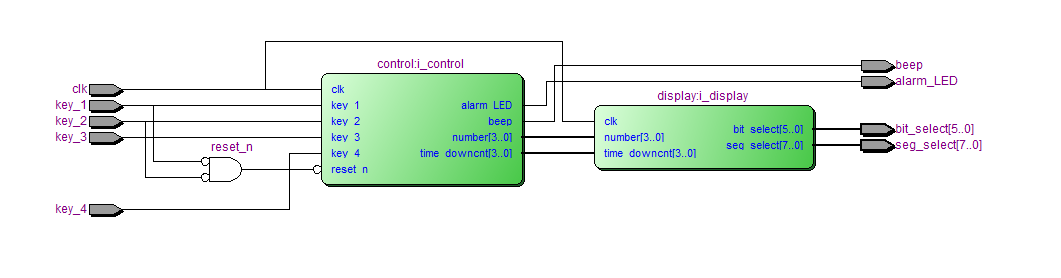

4. RTL图

5. 管脚分配

6. Testbench

7. 仿真图

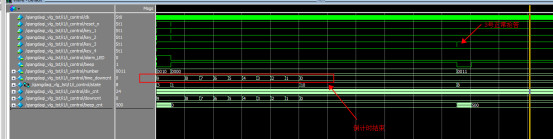

整体仿真图

控制模块仿真

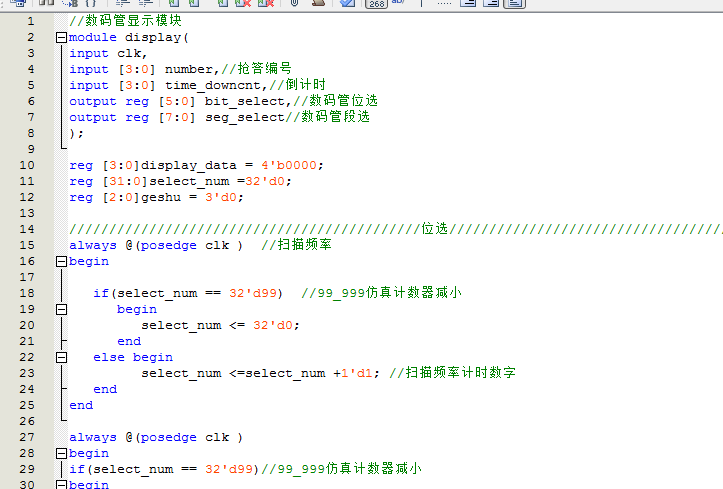

显示模块仿真

部分代码展示:

//数字式竞赛抢答器设计 //设计一个可容纳四组参赛者同时抢答的数字抢答器。 //(1)能判断第一抢答者并报警指示抢答成功,其他组抢答均无效; //(2)设计倒计时时钟,若提前抢答则对相应的抢答组发出警报 module?qiangdaqi?( input?clk,//50MHz //input?reset_n,//复位 input?key_1,//抢答键 input?key_2,//抢答键 input?key_3,//抢答键 input?key_4,//抢答键 output?alarm_LED,//高电平亮,提前抢答指示灯 output?beep,//蜂鸣器,低电平响 output?[5:0]?bit_select,//数码管位选 output?[7:0]?seg_select//数码管段选 ); wire?[3:0]?number;//抢答编号 wire?[3:0]?time_downcnt;//倒计时 wire?reset_n; assign?reset_n=~(key_1==0?&&?key_2==0);//两个按键同时按下作为复位信号 //控制模块 control?i_control?( .?clk(clk),//50MHz .?reset_n(reset_n),//复位 .?key_1(key_1),//抢答键 .?key_2(key_2),//抢答键 .?key_3(key_3),//抢答键 .?key_4(key_4),//抢答键 .?alarm_LED(alarm_LED),//高电平亮,提前抢答指示灯 .?beep(beep),//蜂鸣器,低电平响 .?number(number),//抢答编号 .?time_downcnt(time_downcnt)//倒计时 ); //数码管显示模块 display?i_display( .?clk(clk), .?number(number),//抢答编号 .?time_downcnt(time_downcnt),//倒计时 .?bit_select(bit_select),//数码管位选 .?seg_select(seg_select)//数码管段选 ); endmodule

源代码

?扫描文章末尾的公众号二维码

文章来源:https://blog.csdn.net/diaojiangxue/article/details/135300360

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- Opencv_棋盘格标定相机

- Python实战:获取瑞幸咖啡全国门店和职能部门,竟有接近1.2万个门店

- WorkPlus局域网即时通讯软件的领航者,连接高效协作的利器

- 基于ssm高校勤工助学系统论文

- 物联网协议Coap之C#基于Mozi的CoapServer实现解析

- python2.x编码Unicode字符串

- 【AIGC风格prompt】风格类绘画风格的提示词技巧

- vscode无法自动补全

- 物料采购合同管理系统(JSP+java+springmvc+mysql+MyBatis)

- JAVA小游戏“飞翔的小鸟”