Vivado下配置DDR3的MIG IP核————官网案例学习

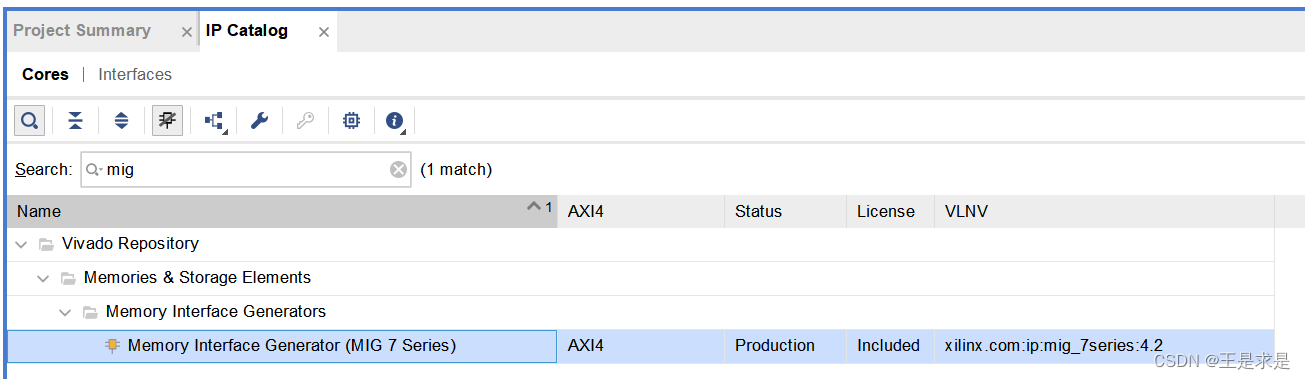

1.双击 Memory Interface Generator(MIG 7 Series)

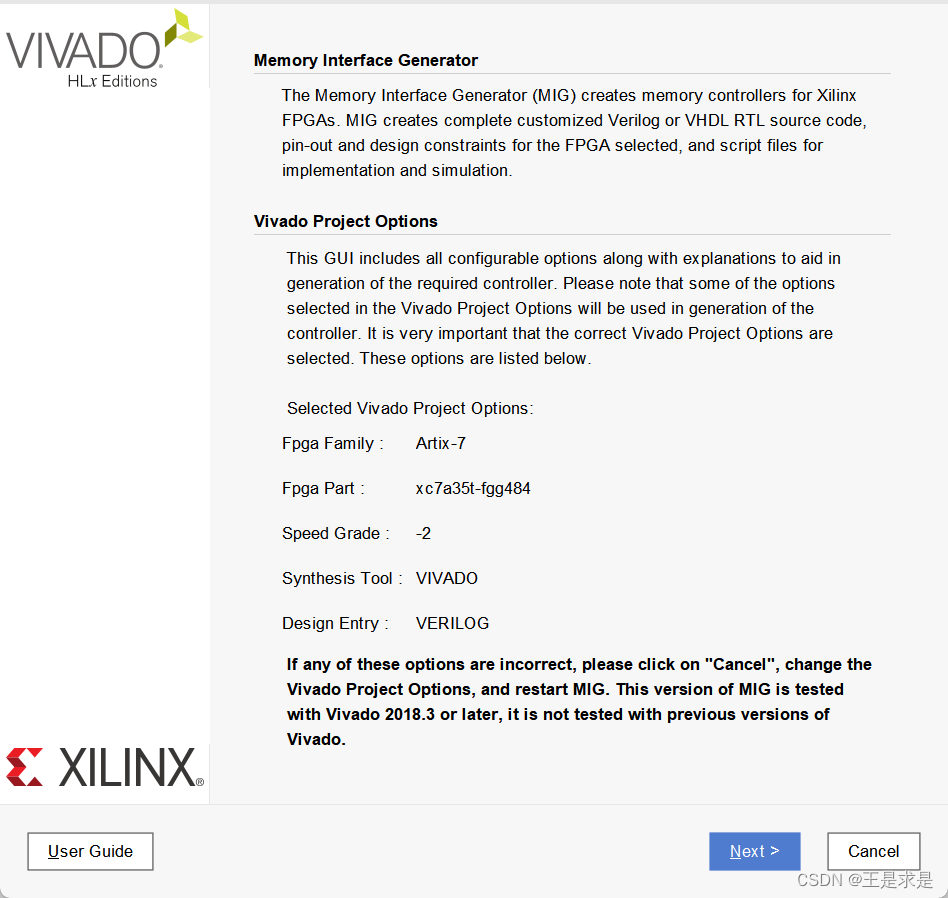

2.next

2.next

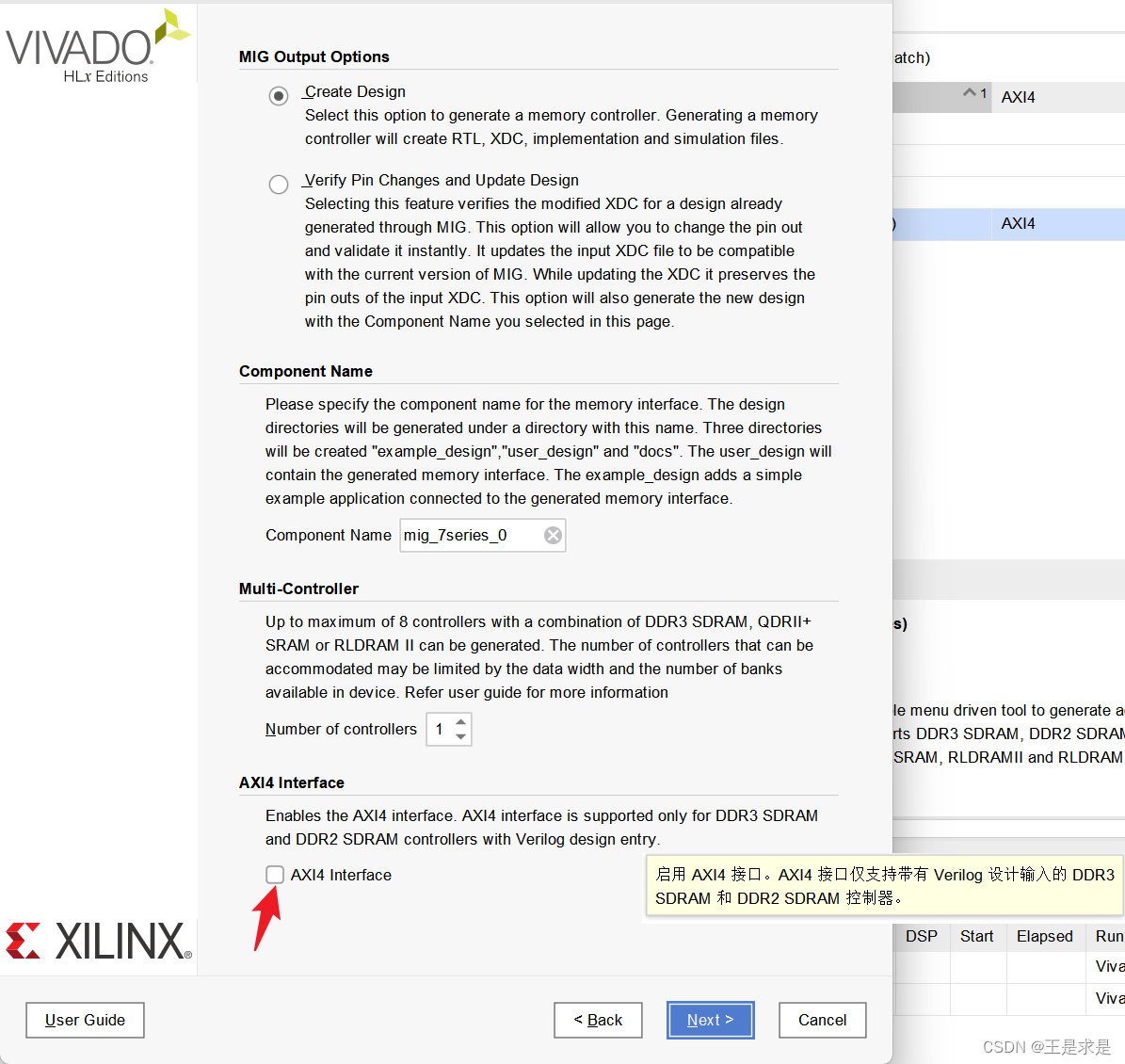

3.注意下面箭头处无需勾选,倘若勾选,则是选择AXI接口,本次使用的是native接口

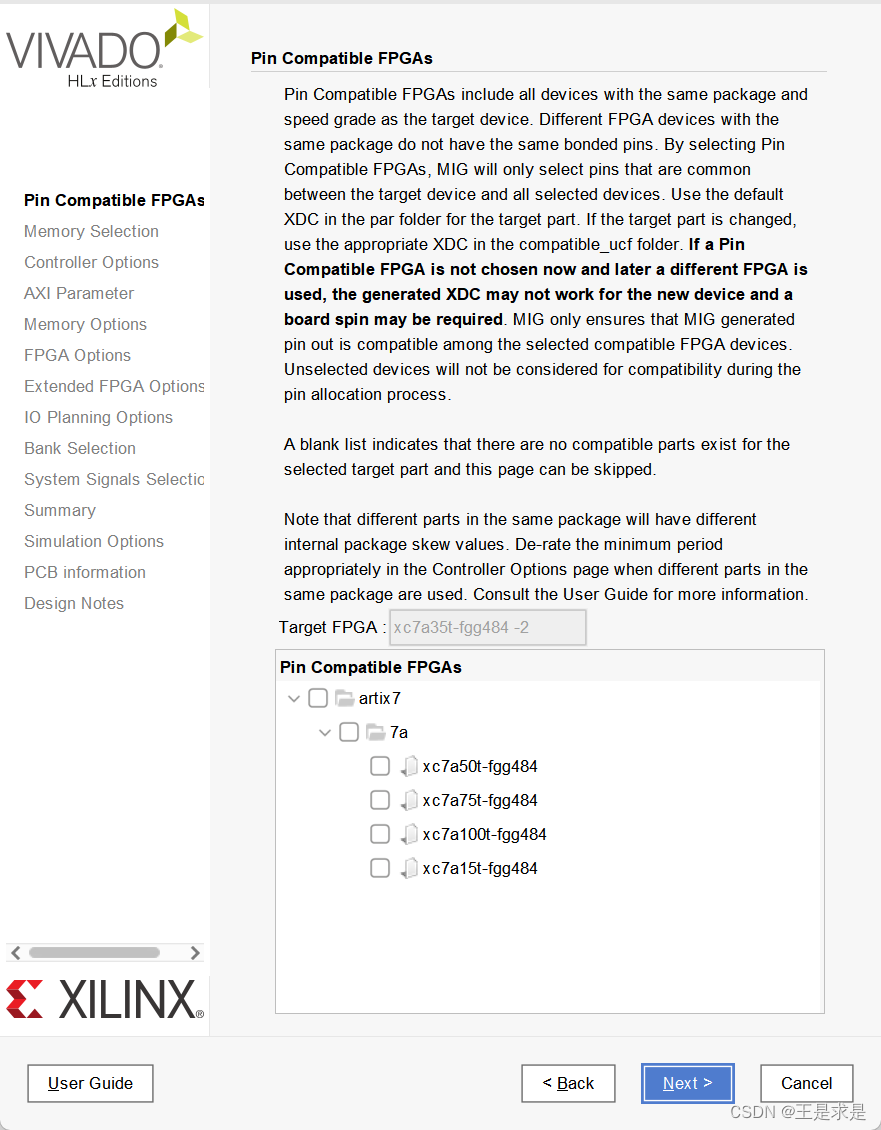

4.next,此处无需考虑兼容其他器件。

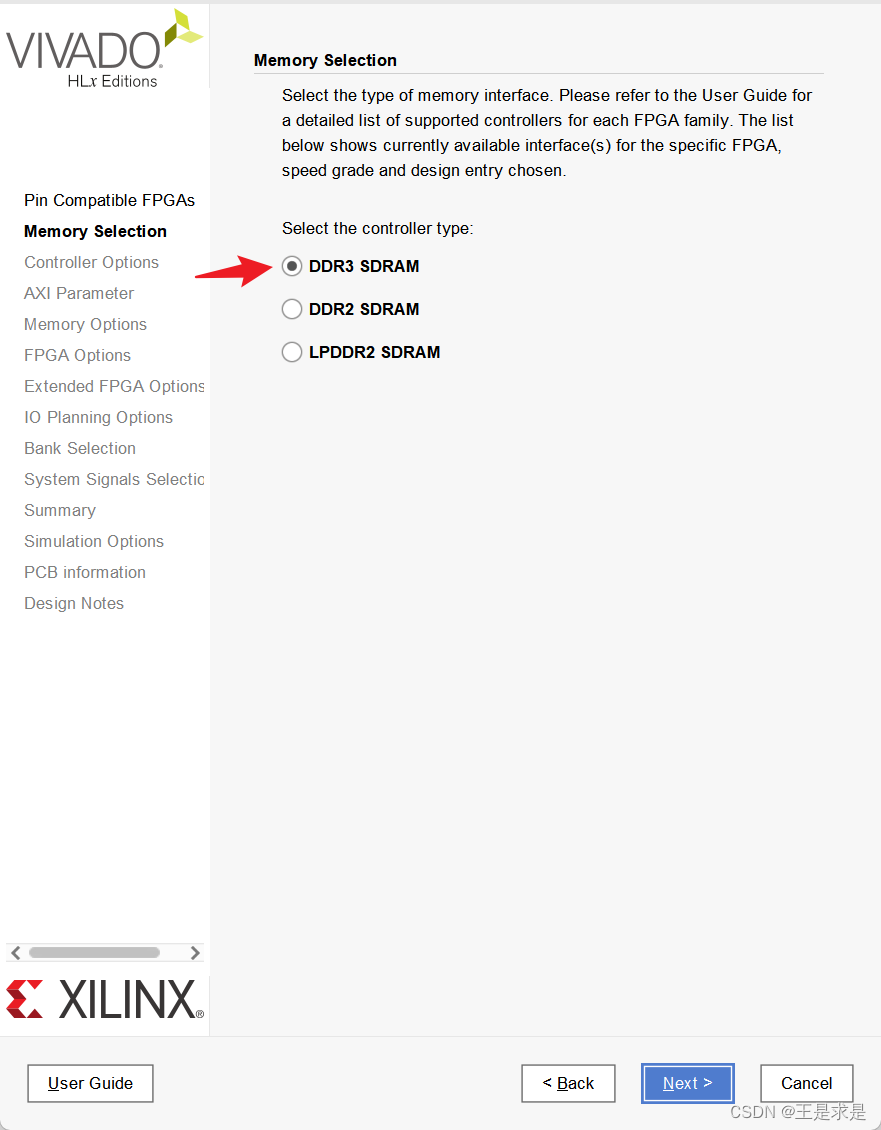

5.选择DDR3

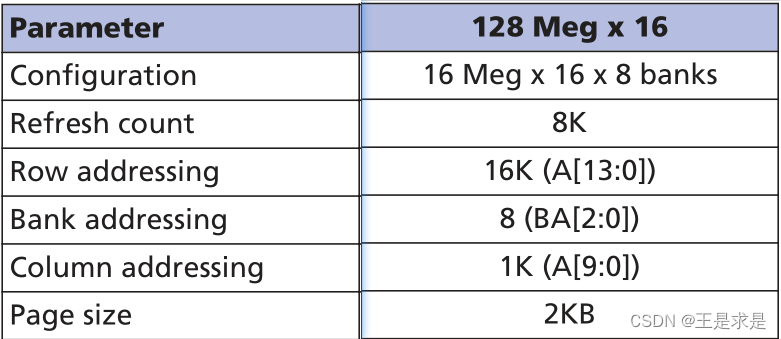

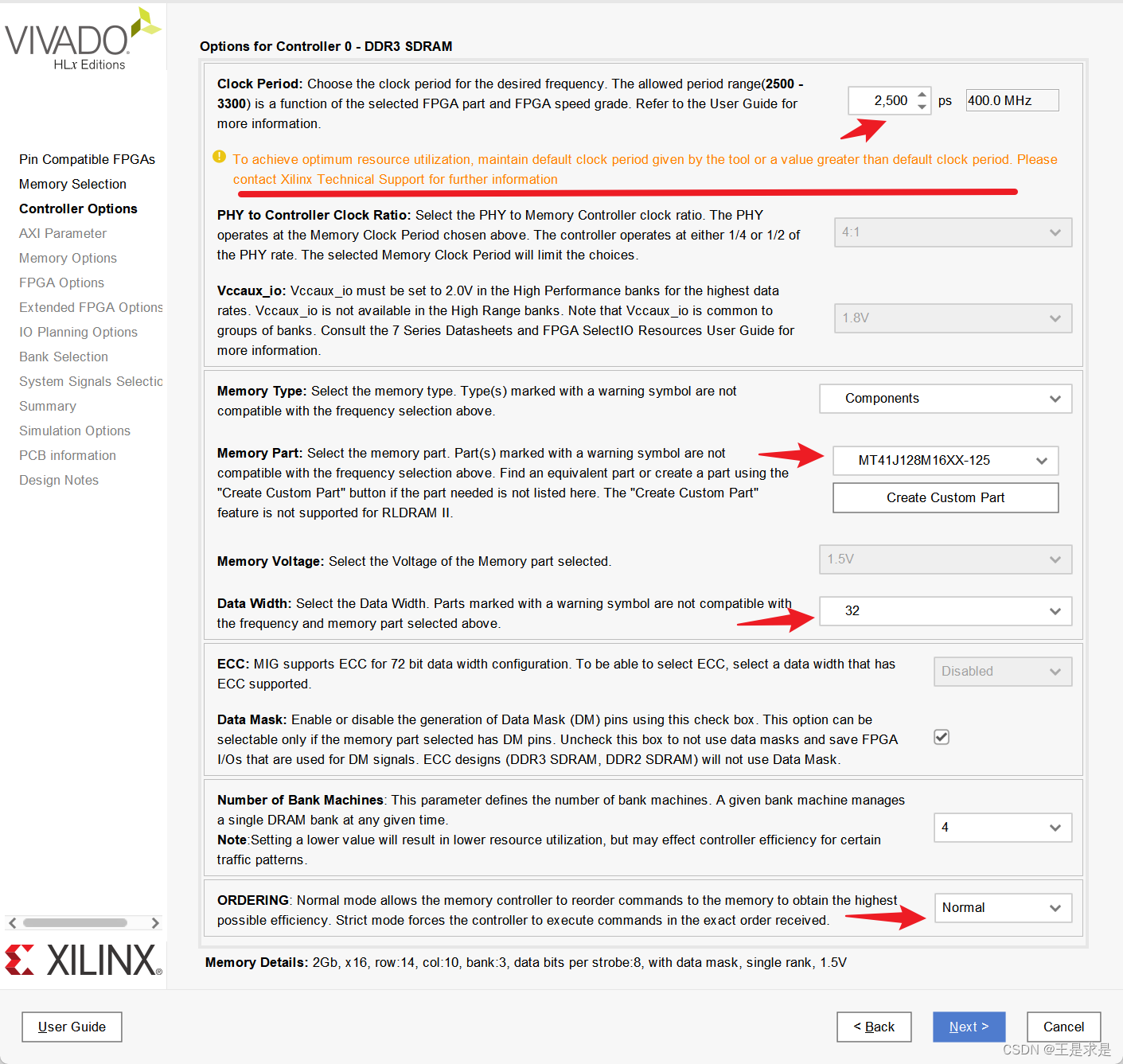

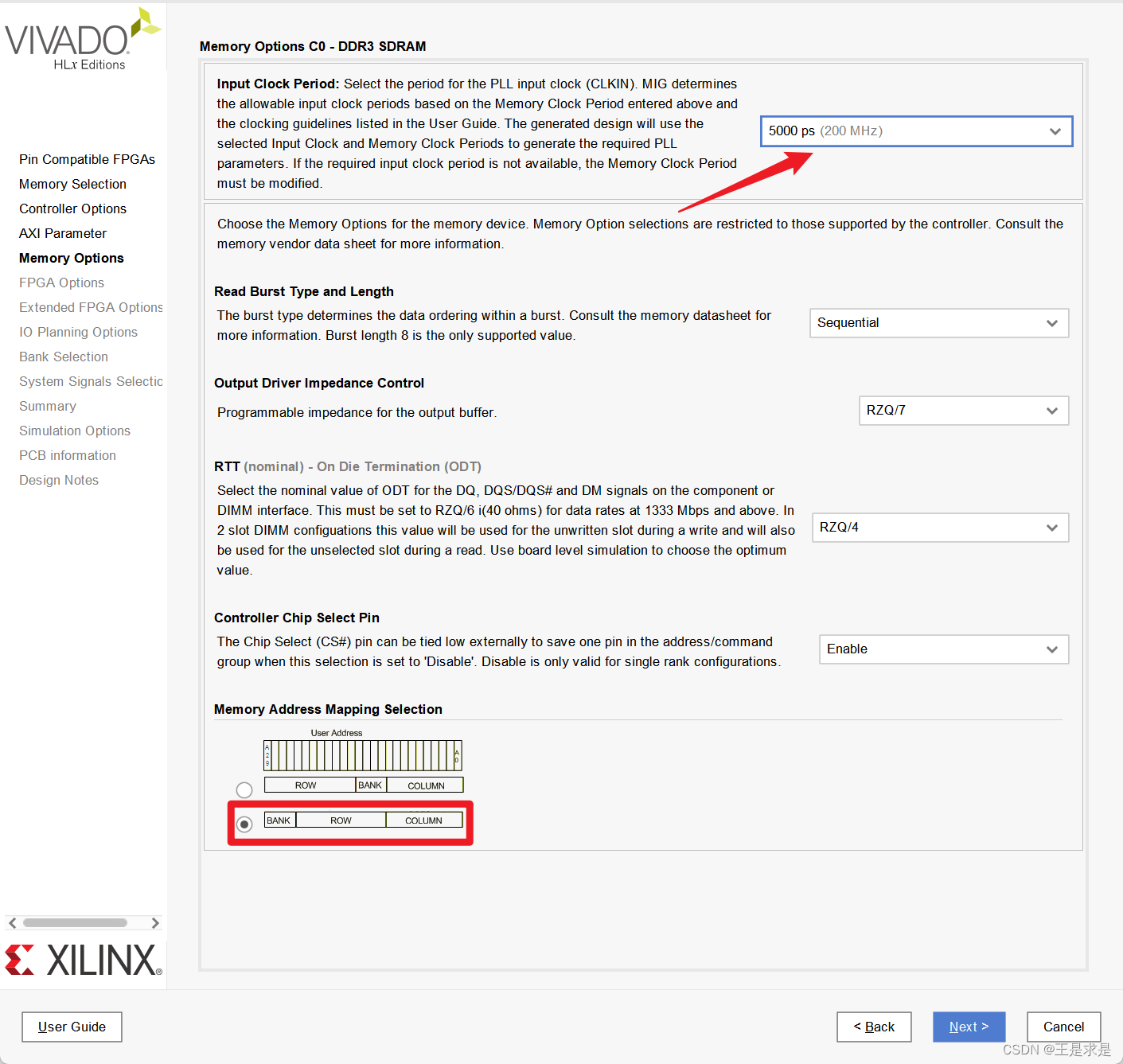

6.第一个箭头,是指DDR3能够运行的周期(2500ps),即最大频率(400MHz)。尽管此芯片可以实现的最大频率(1/125*1000=800MHz),但是,由于此芯片所能提供的最大速度为400MHz,因此填写2500ps。

第二个箭头,代表DDR3的型号。MT41J是指镁光的一种DDR3型号。

![]()

第三个箭头,因为我们是两片DDR3芯片,所以是32位。

第四个箭头,选择normal,这样的好处是可以节省资源,其他默认不变。

上面打勾的是进行掩膜。可以防止数据误写入。

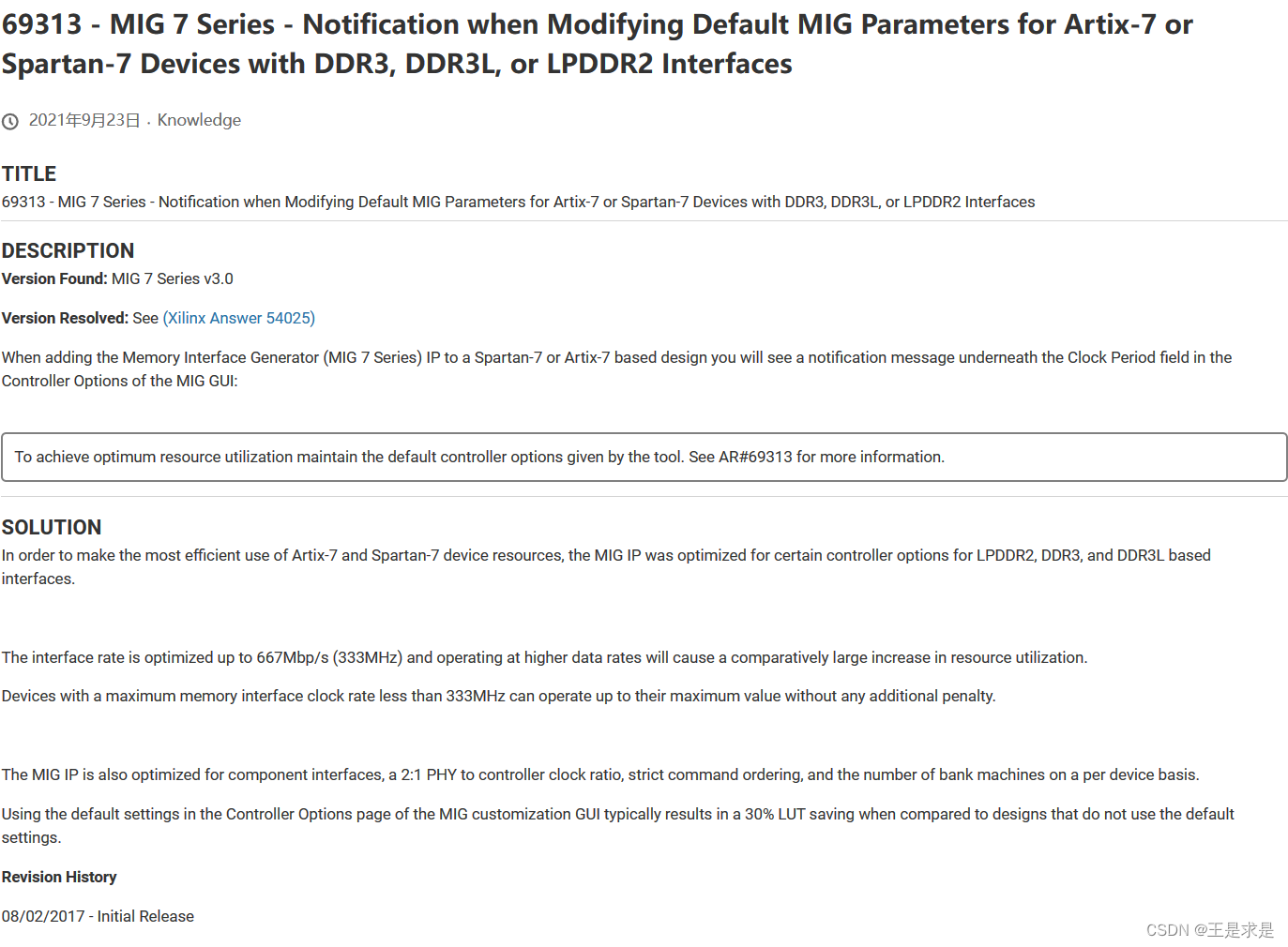

下面两幅图,是对黄色字及上面红线的解释说明。

7.箭头是指系统时钟,这个时钟是工作时钟可以选择200MHz,也可以是其他的。红色框更加有利于MIG核进行数据写入DDR3中。

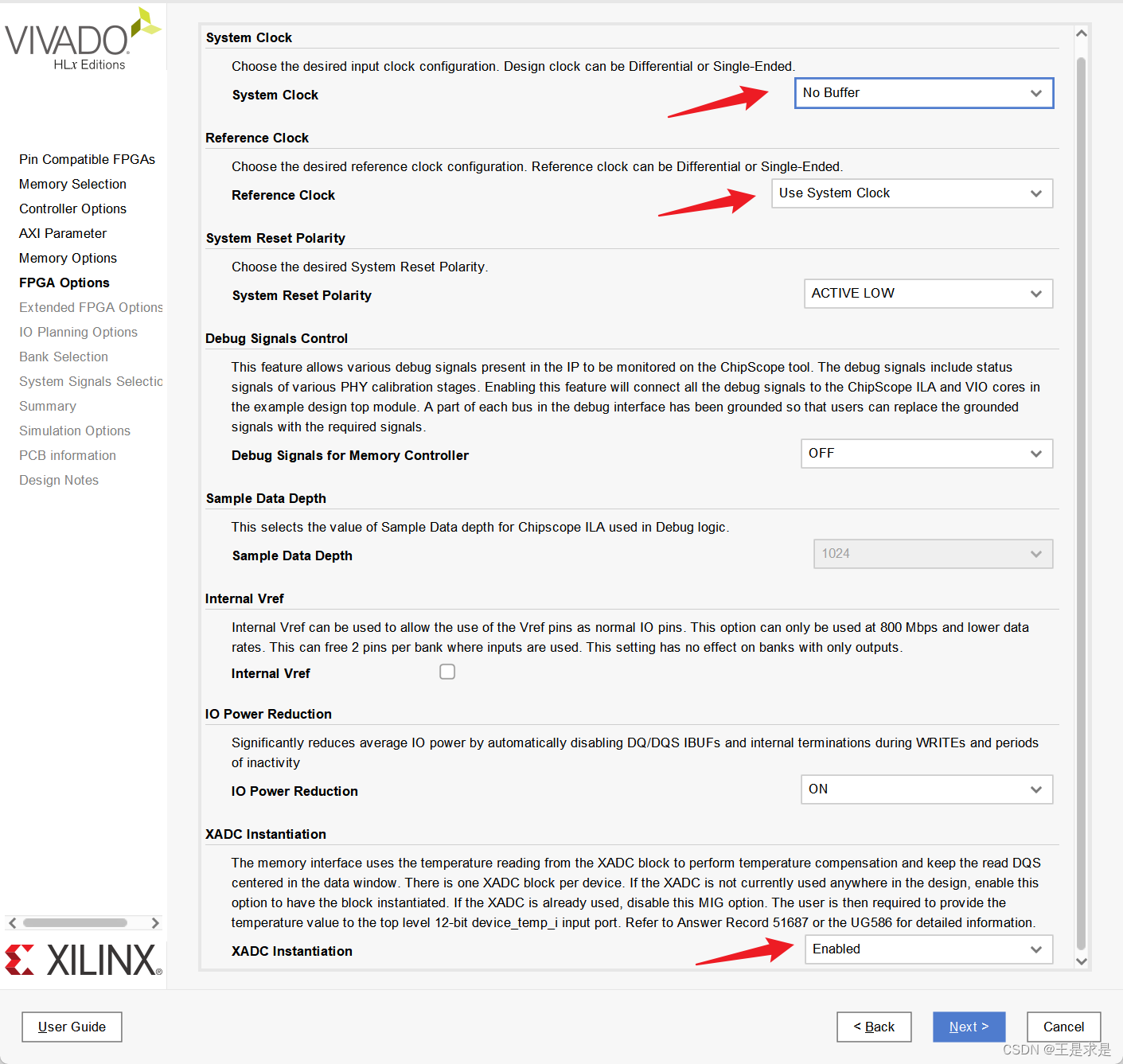

8.第一个箭头,表示是对system clk的操作,有三种选择(Differential、Singled-Ended和No buffer).前两种表示FPGA外部电路提供的时钟信号(差分时钟,单端时钟),最后一种代表的是FPGA内部经由锁相环生成的时钟信号。一般在设计开发板,为了节约引脚数目,此信号会由FPGA内部锁相环生成更为方便。

第二个箭头是指参考时钟有四种,前三种和系统时钟的配置是一致的。第四种表示,如果系统时钟也是200MHz二者可以共用一个时钟。这也就说明,参考时钟是固定200Hz。这里需要注意2020.2版本的设置IP核时有Bug,第二次打开,系统时钟会变化为400MHz,因此参考时钟找不到Use System Clock选项。

第三个箭头是XADC进行温度采集的,百度翻译如下:

内存接口使用 XADC 模块的温度读数来执行温度补偿,并使读取的 DQS 保持在数据窗口的中心。每个设备有一个 XADC 块。如果 XADC 当前未在设计中的任何位置使用,请启用此选项以实例化模块。如果已使用 XADC,请禁用此 MIG 选项。然后,用户需要向顶层 12 位 device_temp_i 输入端口提供温度值。有关详细信息,请参阅答复记录 51687 或 UG586。

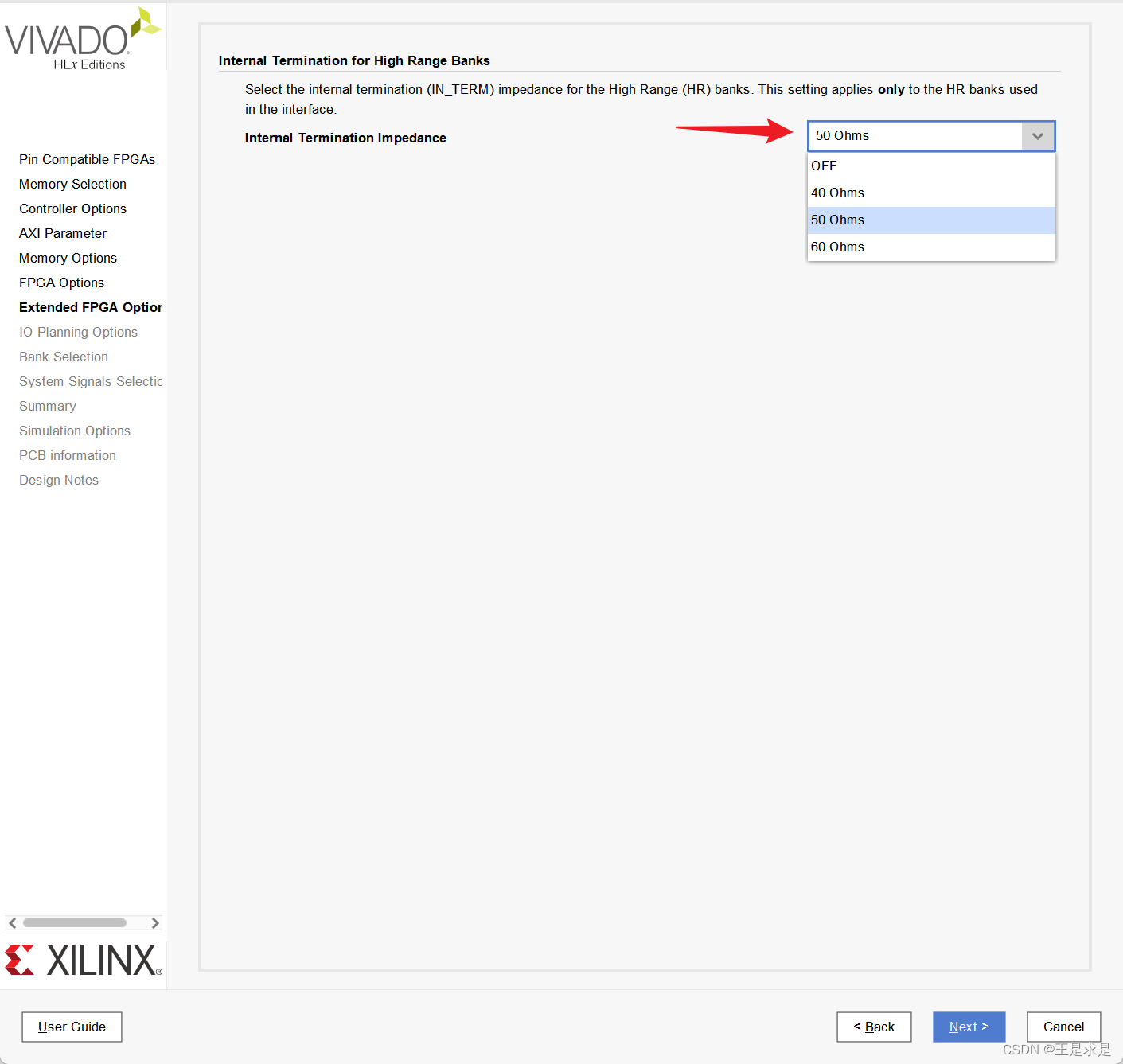

9.这个是设置信号线的阻抗匹配,和开发板的设置有关,一般阻抗越大,其线宽越窄,更加有利于布线,这里根据开发板PCB布线自行设置。

9.这个是设置信号线的阻抗匹配,和开发板的设置有关,一般阻抗越大,其线宽越窄,更加有利于布线,这里根据开发板PCB布线自行设置。

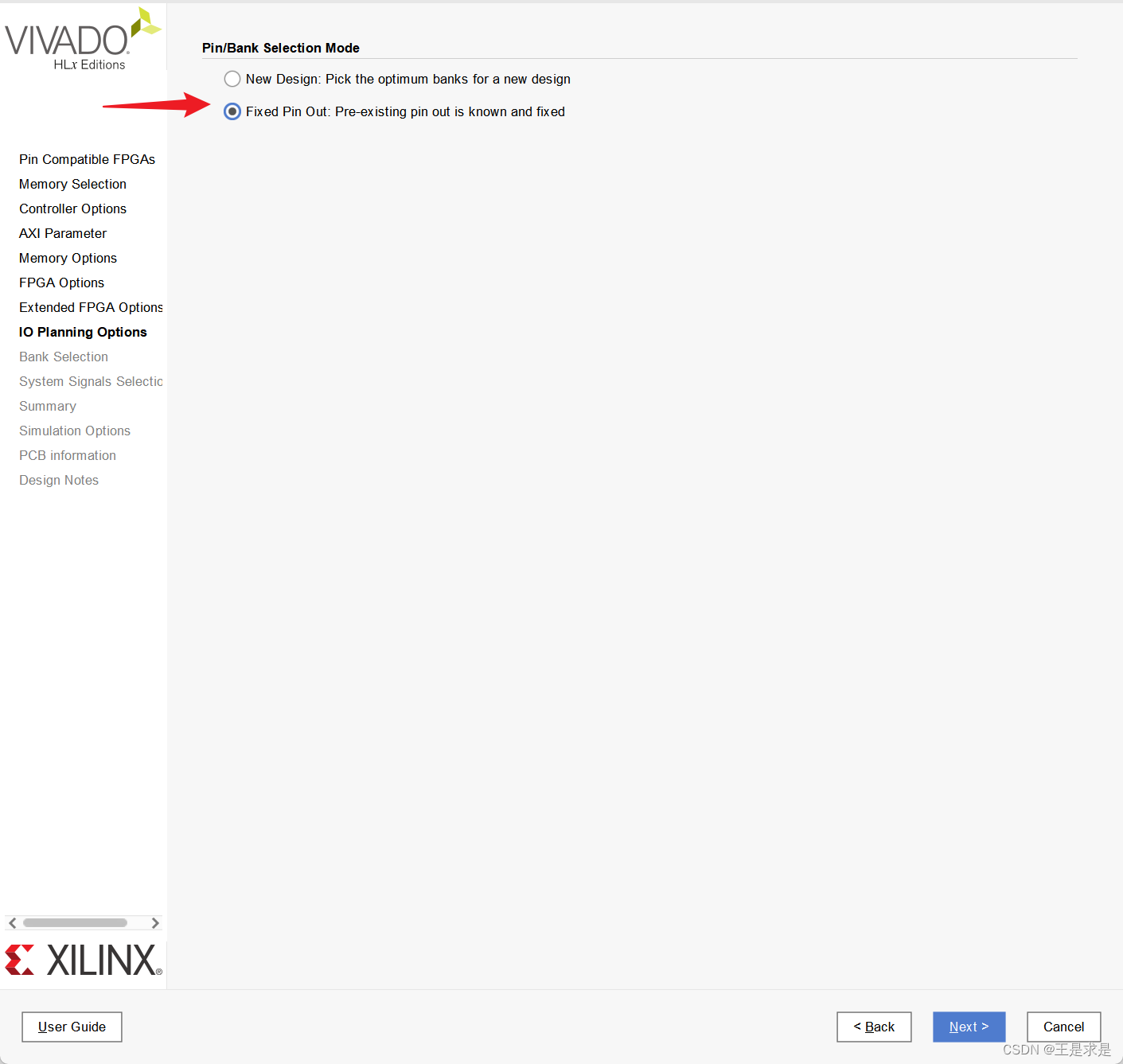

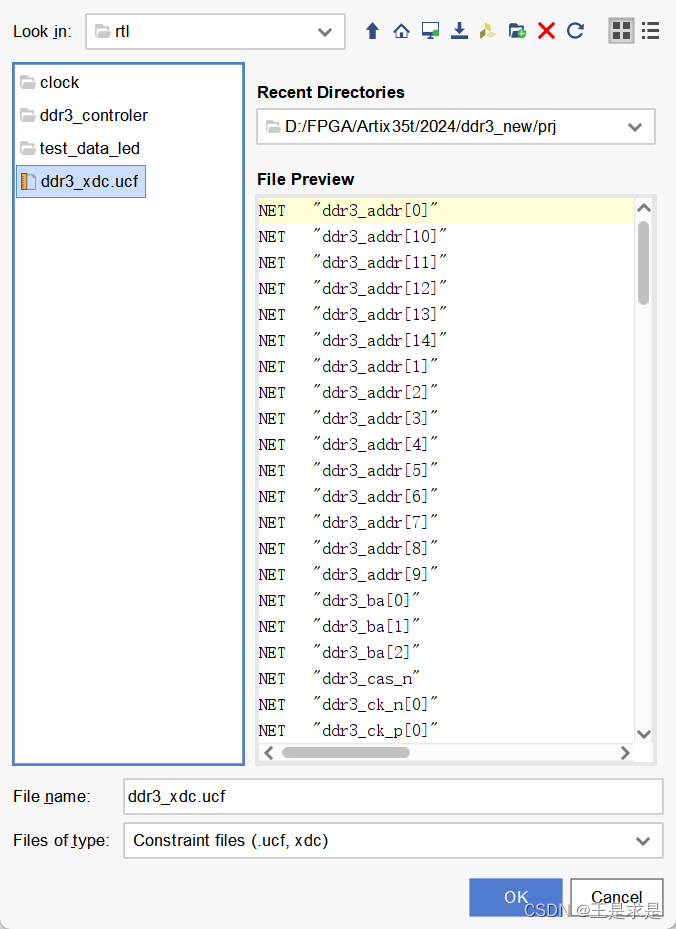

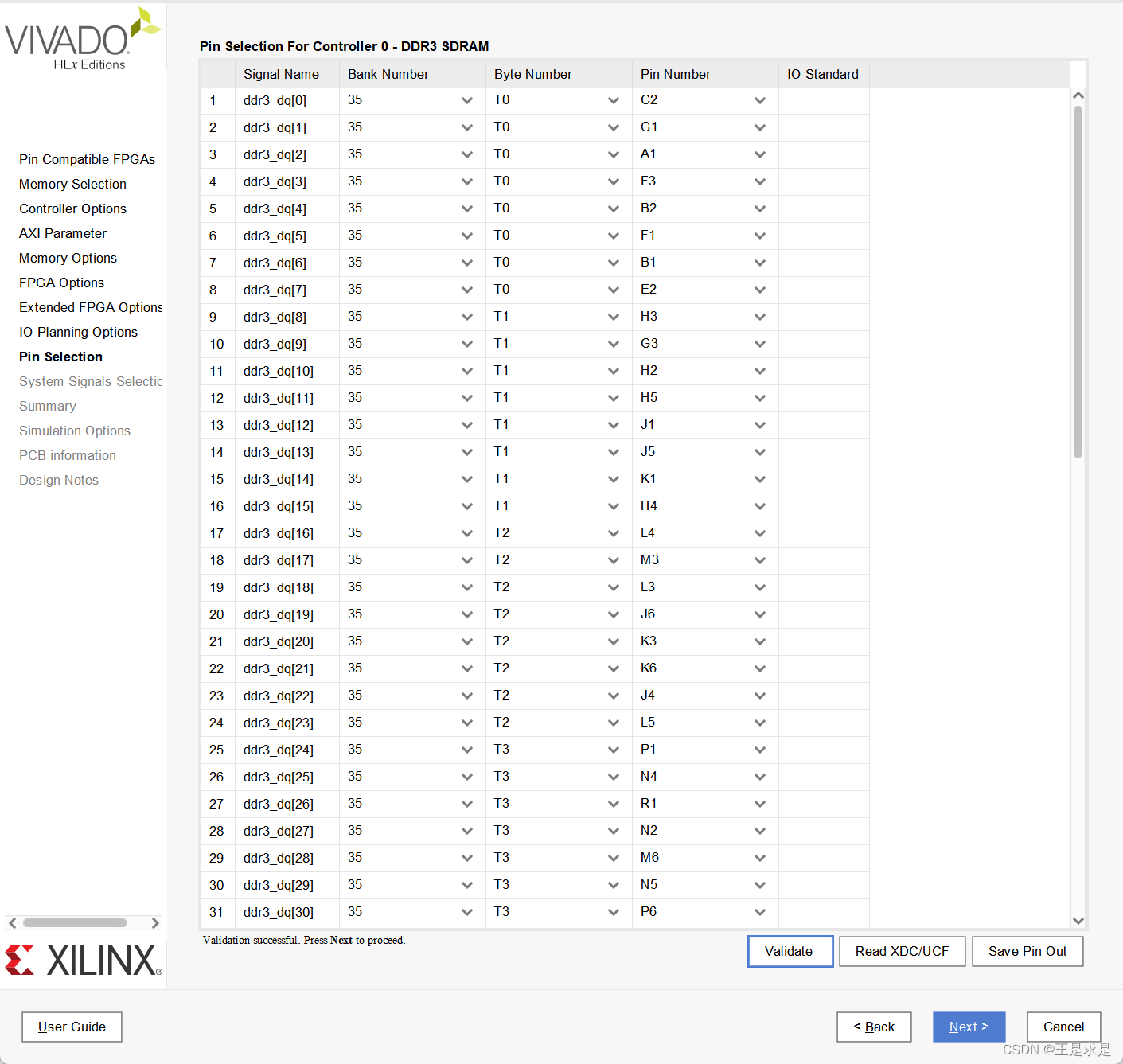

10.引脚分配问题。根据开发板引脚原理图进行配置即可,我使用的是正点原子达芬奇Pro,从他家的官网可以找到其ddr3引脚管理(ddr3_xdc.ucf)

11.进行配置

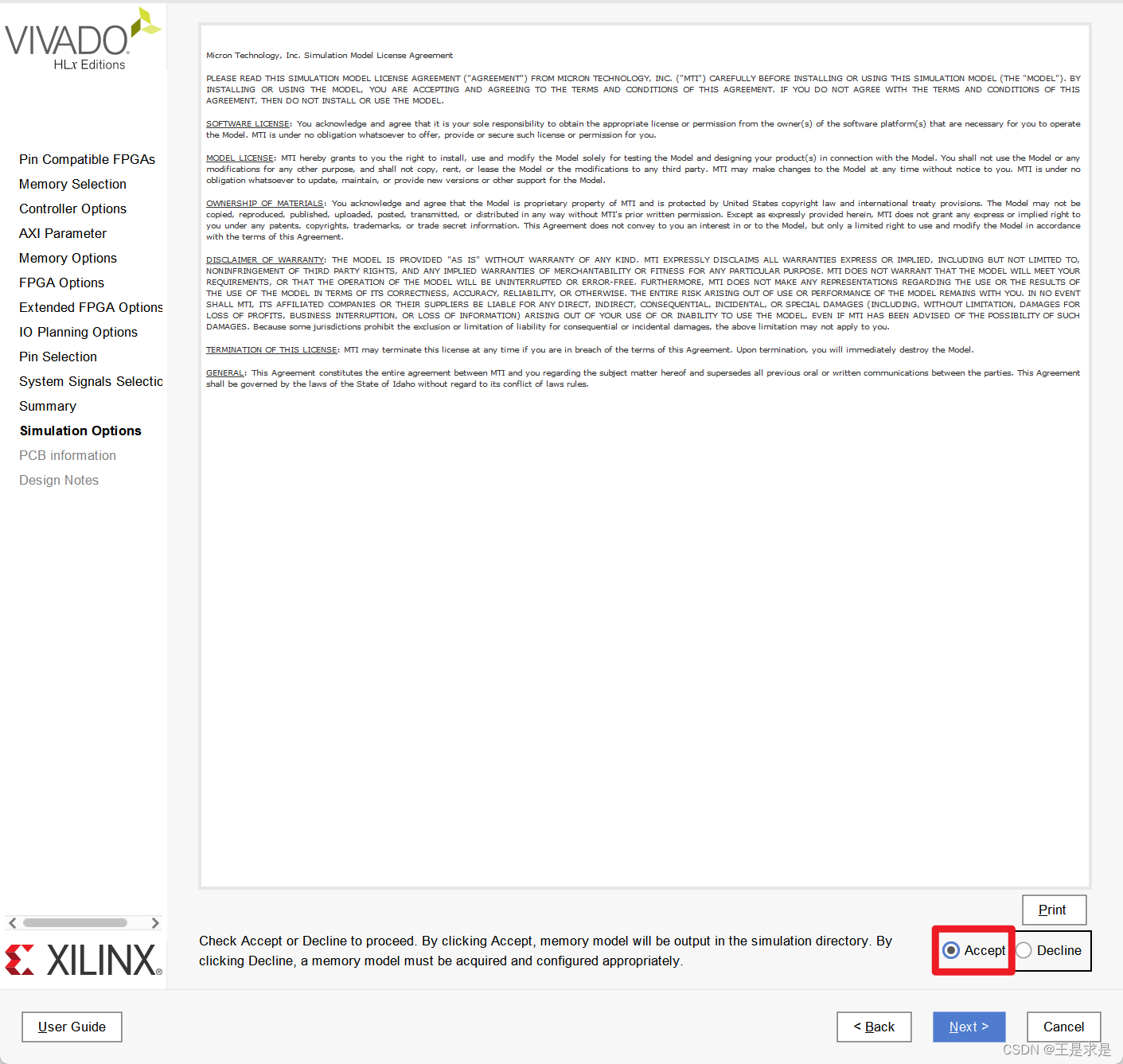

12.一路next,accept即可。

13.选择Global。

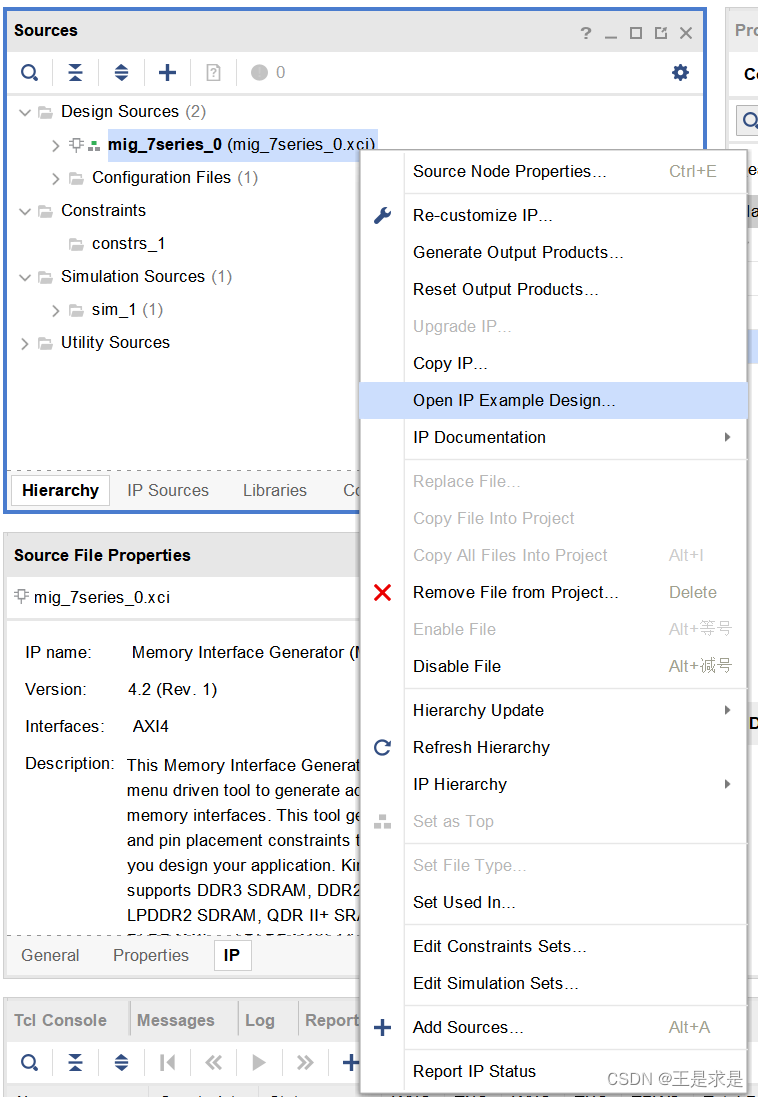

14.生成官方example,之所以这样操作,是考虑到后面可以能会按照同一流程,进行DDR3的配置,不同工程,不同器件。首先运行一下官网案例,观察能否初始化成功,然后再将官网案例打包成一个类似于RAM的形式,进行数据操作。

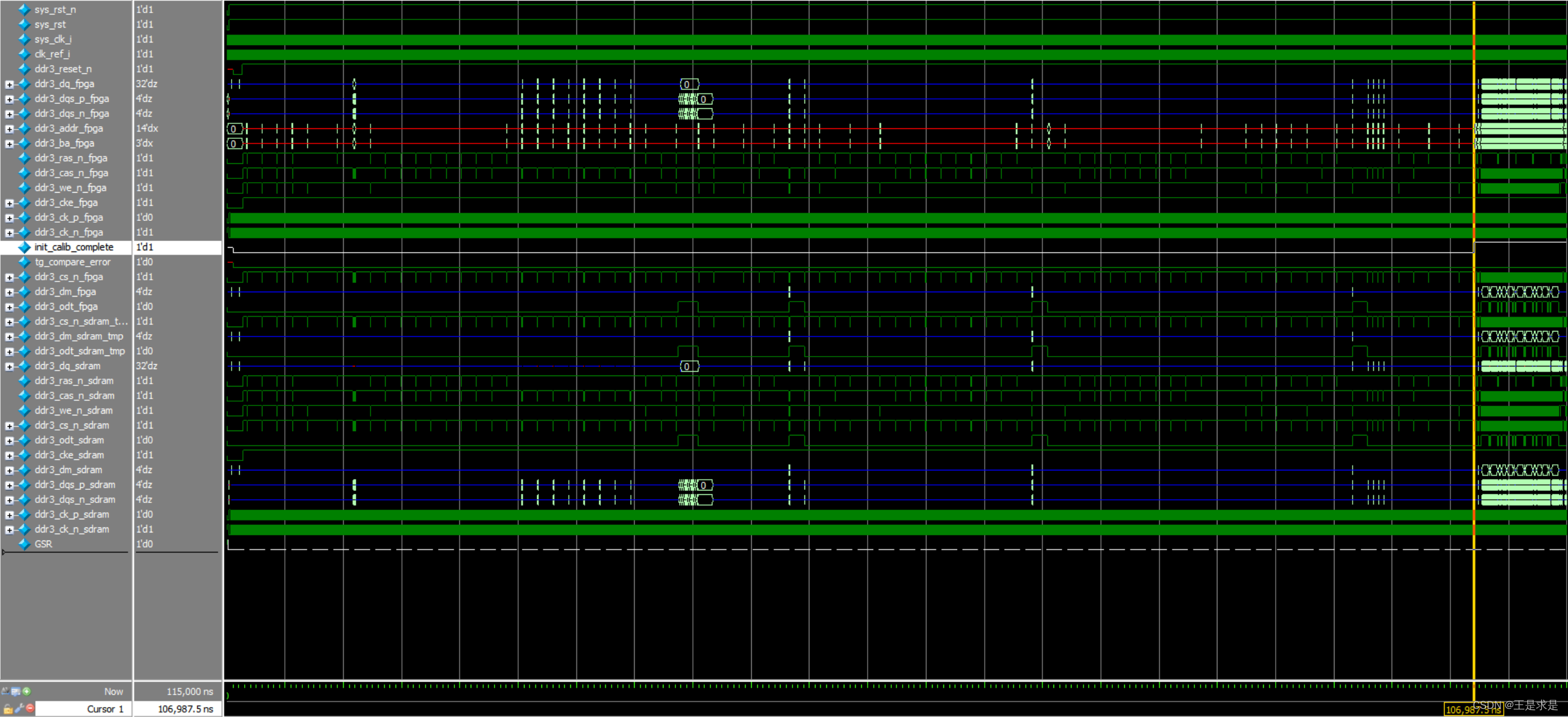

15.运行官网案例进行仿真,在上一个博客中,已经介绍了vivado和modelsim联动,有兴趣可以看看。vivado的仿真也能用,但是速度太慢,还容易导致电脑宕机。标白处为初始化信号,在此版本下,花了106us才完成初始化。

至此MIG的Native官方案例生成成功。

至此MIG的Native官方案例生成成功。

主要参考:小白fpga、1_【正点原子】达芬奇Pro之FPGA开发指南 V2.1.pdf

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 网络(七)路由协议以及相关配置

- InnoDB底层的一些主要数据结构

- 在Windows中使用VirtualBox安装Ubuntu虚拟机Oracle VM VirtualBox——备赛笔记——2024全国职业院校技能大赛“大数据应用开发”赛项

- yolov8 opencv dnn部署 github代码

- 【React】class组件生命周期函数的梳理和总结(第一篇)

- 找不到mfc140.dll无法继续执行怎么办?总结5个修复方法

- Spring Boot 2.x 到 3.2 的全面升级指南

- Linux 系统上发行版和相应的卸载软件的命令

- 《向量数据库指南》——向量数据库两股新势力,云是方向

- 大神怎样优雅的捕获一个异常,写个try catch的方式都这么优雅!