FPGA之 寄存器、触发器、锁存器

发布时间:2024年01月17日

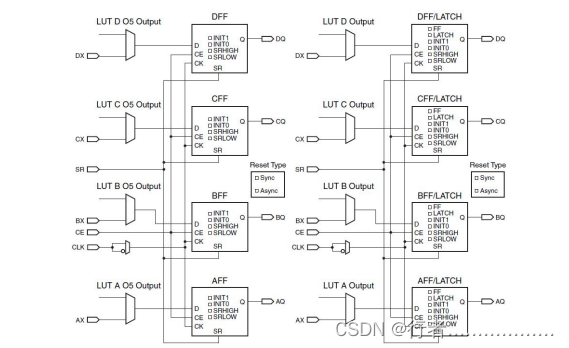

每个slice有8个存储元素,每个存储元素如下图所示:

?其中四个为DFF/LATCH,可以配置为边沿触发D型触发器或电平敏感锁存器输入上图。D输入可以通过AFFMUX, BFFMUX, CFFMUX或DFFMUX的LUT输出直接驱动,也可以通过AX, BX, CX或DX输入绕过函数发生器的 BYPASS slice输入直接驱动。当配置为锁存器时,当CLK 为低电平时,锁存器是透明的。

另外四个为仅为DFF,它们只能配置为边沿触发的D型触发器。D输入可以由LUT的O5输出驱动,也可以由AX, BX, CX或DX输入的BYPASS slice输入驱动。当原始的四个存储单元配置为闩锁时,这四个附加的存储单元将无法使用。触发器代码如下,当敏感型号 CLK 上升沿到来把 B 值赋给

Aalways@(posedge CLK)

A<=B;

锁存器代码如下,当C为1 时候把 B 赋值给 A,锁存器应该尽力避免,因为会影响到电路时序收敛,对毛刺敏感,容易导致意想不到的错误。

always@(*)

if(C==1'bl)

A<=B;

避免锁存器的代码

always@(*)

if(C==1'bl)

A<=B;

else

A<=1'b0;

文章来源:https://blog.csdn.net/lsh11111/article/details/135654690

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 计算机网络——第三层:网络层

- 【C++】结构体、重载

- tensorrtx-yolo版tensorrt环境安装

- 数据库中修改表的语句

- pytorch安装+出现ModuleNotFoundError: No module named ‘torchvision‘的解决办法

- 力扣hot100 环形链表 快慢指针 计步器

- 使用克魔助手进行iOS数据抓包和HTTP抓包的方法详解

- 设计模式——策略模式

- python:改进型鳟海鞘算法(SSALEO)求解23个基本函数

- 【科普】家长们:如何早期发现孩子的听力问题?