计算机硬件系统设计——运算器设计

计算机硬件系统设计——运算器设计

文章目录

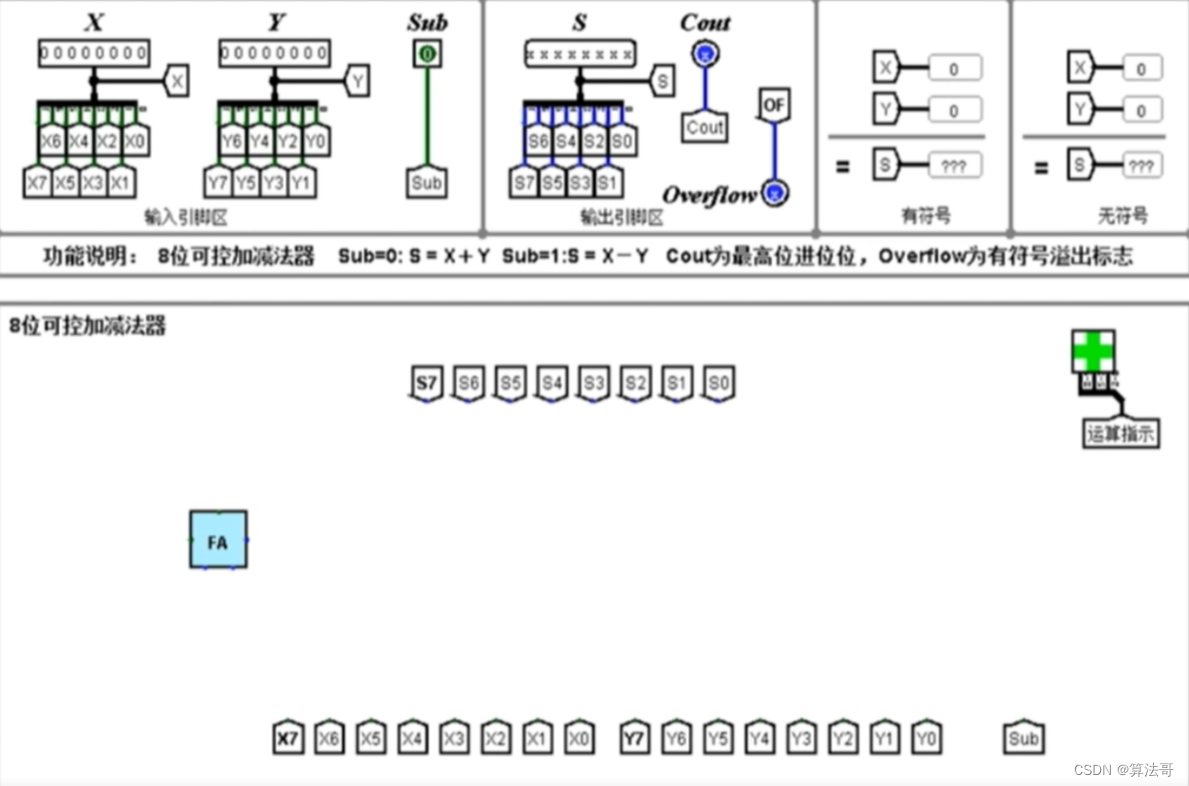

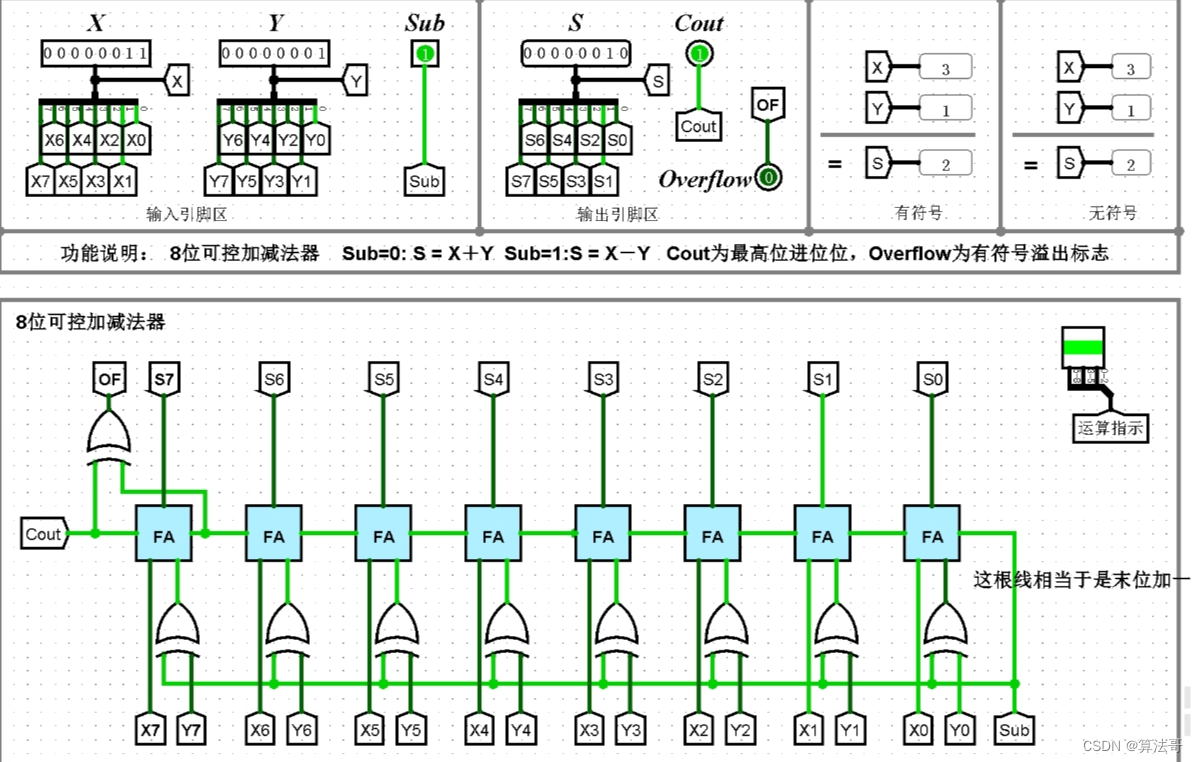

8位可控加减法器

实验界面如下:

上图中的上面部分为电路的控制区域,下面为电路的连线区域。

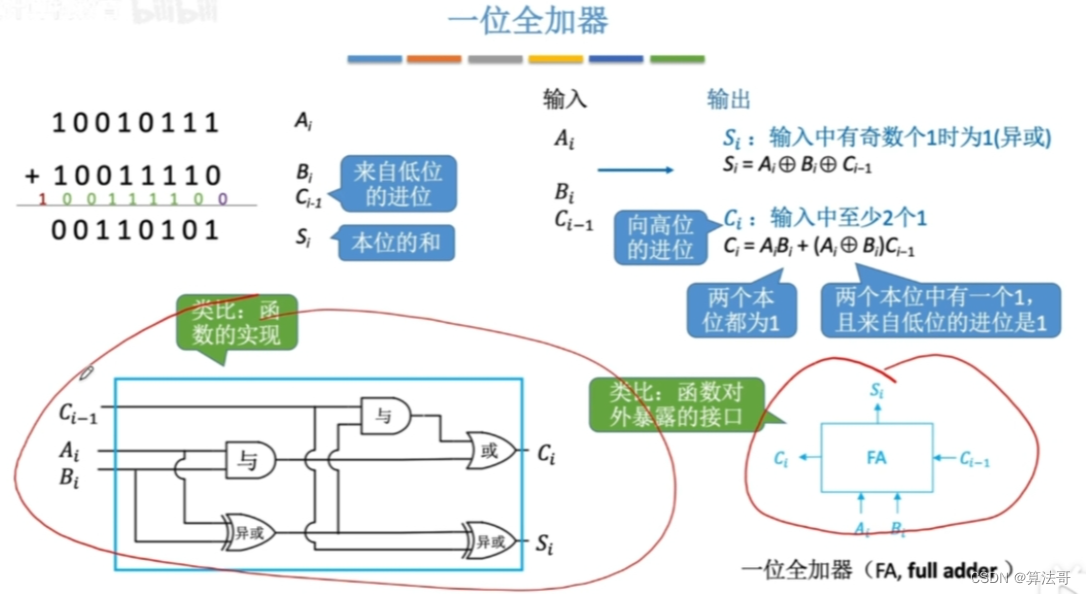

首先可以看到实验中给我们提供了一片已经封装好的FA全加器电路,在这里我们来回顾一下全加器电路。

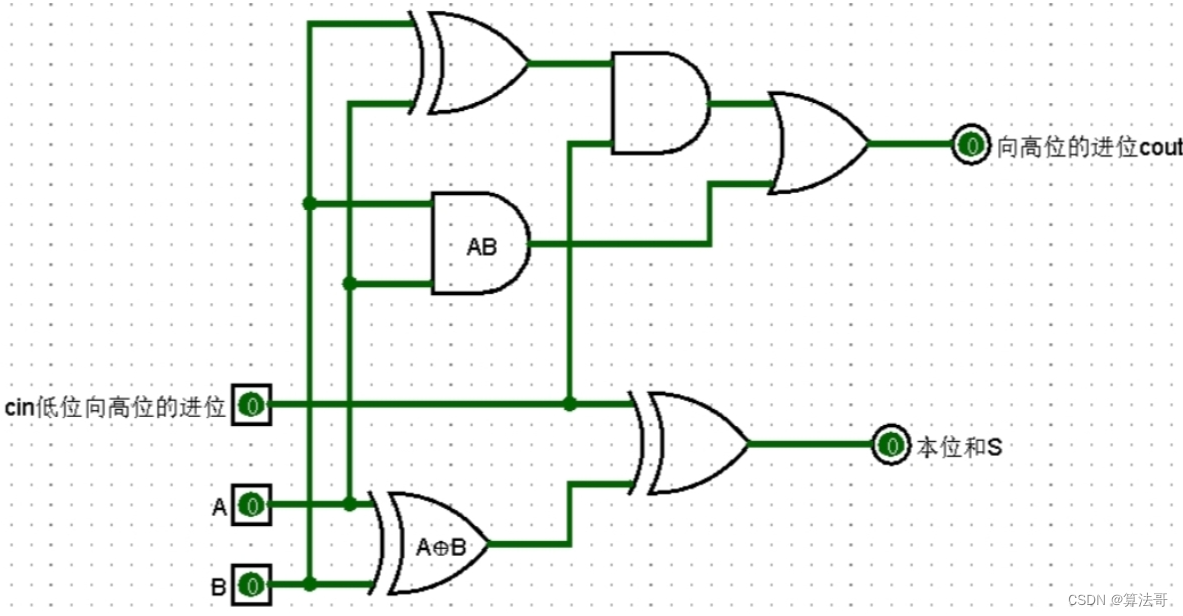

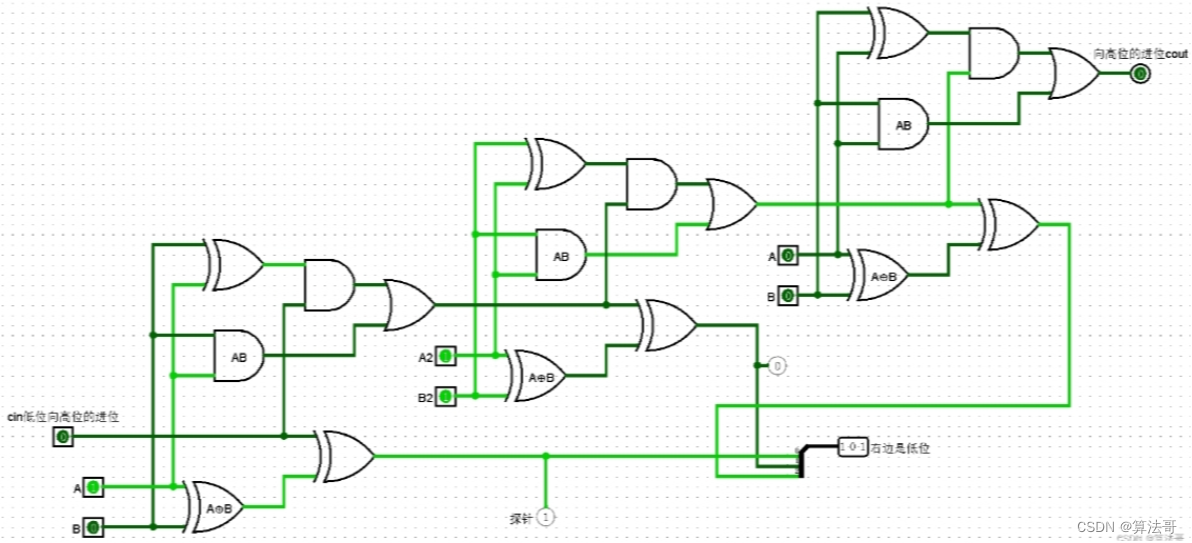

A、B分别为输入的两个一位二进制数,从封装好的FA电路下端进行输入。FA电路的左右两端均为低位向高位的进位,而上端输出的S是本位和。下面是该一位全加器的具体电路图:

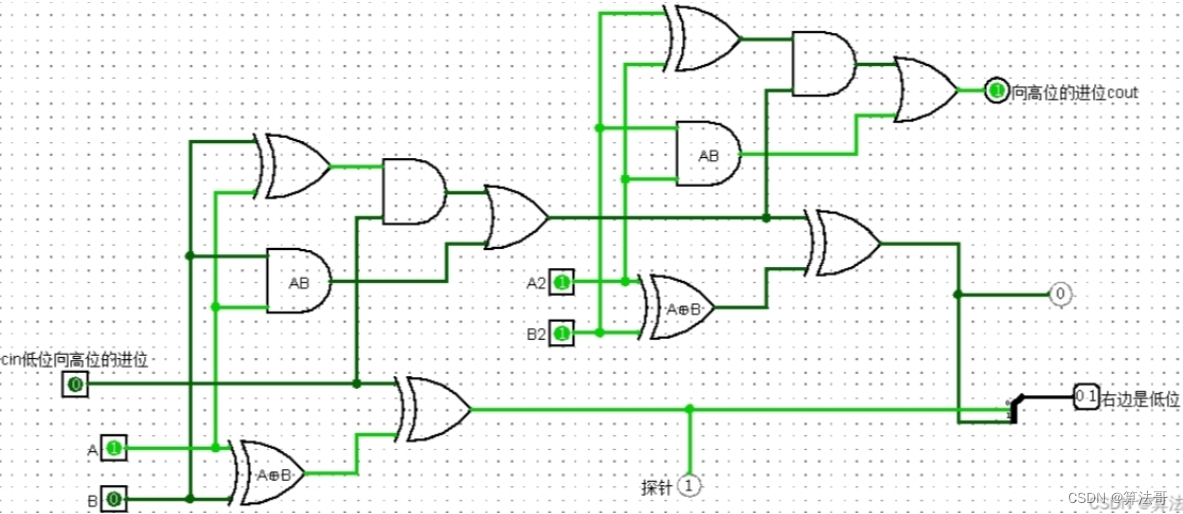

例如:下图将两个一位全法器相连,即可进行2位二进制的加法运算,若A输入为11,B为10,即结果为01,并向高位的进位为1。

2位加法器:

同理,3位加法器如下:

3位加法器:

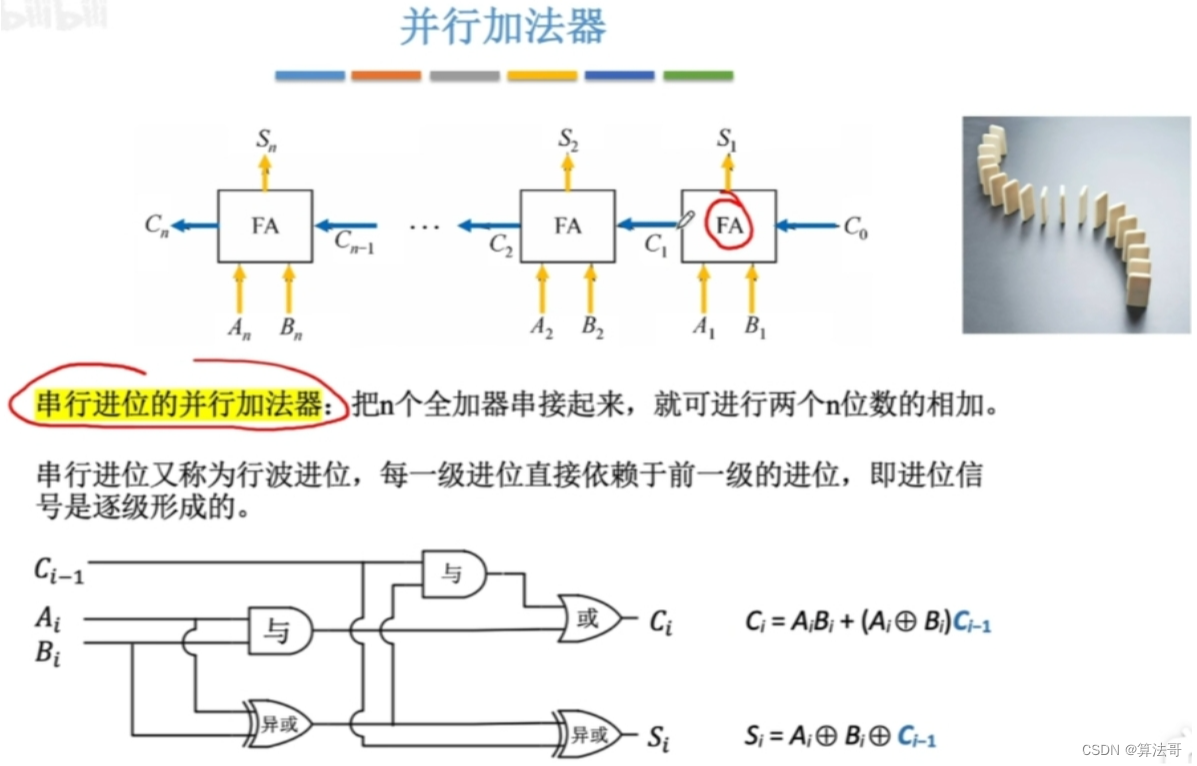

由以上的知识可得,把n个全法器相连可得到n位加法器。而把n个全法器相连得到的n位加法器就称为串行进位加法器,串行进位又称为行波进位,每级进位直接依赖于前一级的进位,即进位信号是逐级形成的。

串行进位加法器(把n个全加器相连得到的n位加法器)

所以,要实现8位的加法器,我们只需要让8个一位全加器串接起来,就可以实现两个8位二进制数的相加。

理解了加法实现后,我们再来看看计算机中的二进制减法是如何实现的。

二进制数的运算都是用它的补码来参与运算的,正数的原码、反码和补码都是一样的,而负数的补码是其原码从右往左找到第一个1,这个1左边的所有**“数值位”**按位取反得到。

例如:X-Y即[X]补-[Y]补可以转变成[X]补+[-Y]补,所以要实现减法,本质上就是加上一个负数。

[X]补与[-X]补之间的互换规则为:全部位按位取反、末位+1或者从右往左找到第一个1,这个1左边的全部位按位取反。所以当Sub的值为1时,即进行减法运算,此时将Y每位的值与Sub进行异或,就能达到按位取反的操作。

CF是最高位(符号位)的进位,次高位进位是数据的最高位向符号位的进位。

而OF判断溢出的值等于CF与次高位进位的异或值。

因此8位可控加减法器的电路图如上。

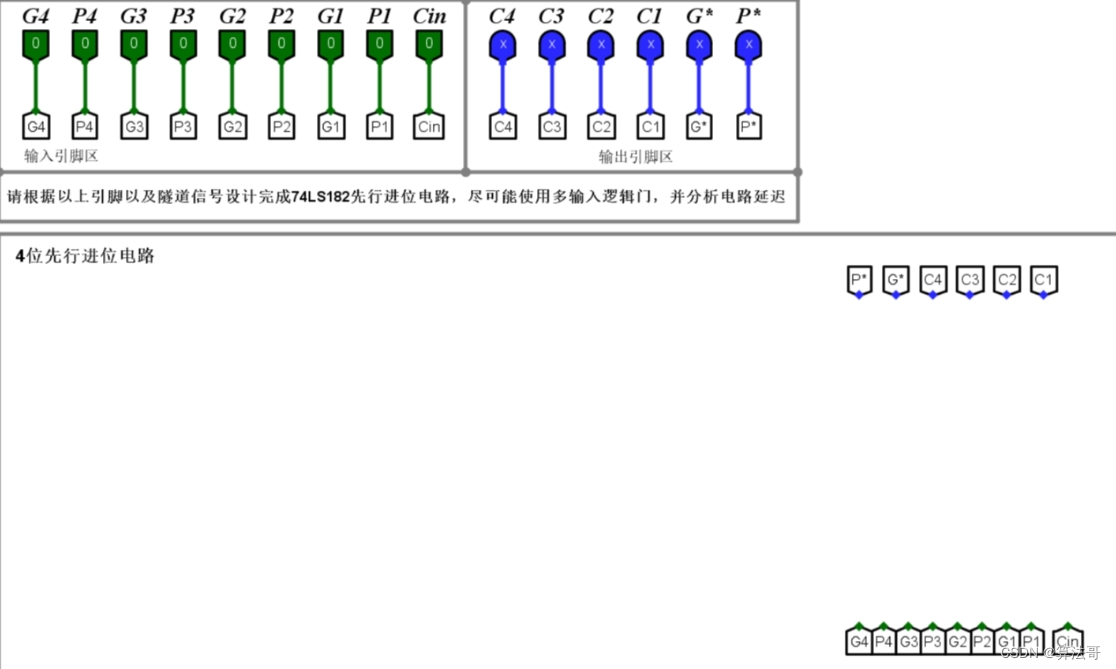

4位先行进位电路74182

实验电路框架如下:

在第一个实验中做的8位可控加减法器就是一种串行进位加法器,低位运算产生进位所需的时间将影响高位运算的时间。因此,串行进位加法器的最长运算时间主要是由进位信号的传递时间决定的,位数越多延迟时间就越长,而全加器本身的求和延迟只为次要因素,所以加快进位产生和提高传递的速度是关键。

并行进位加法器

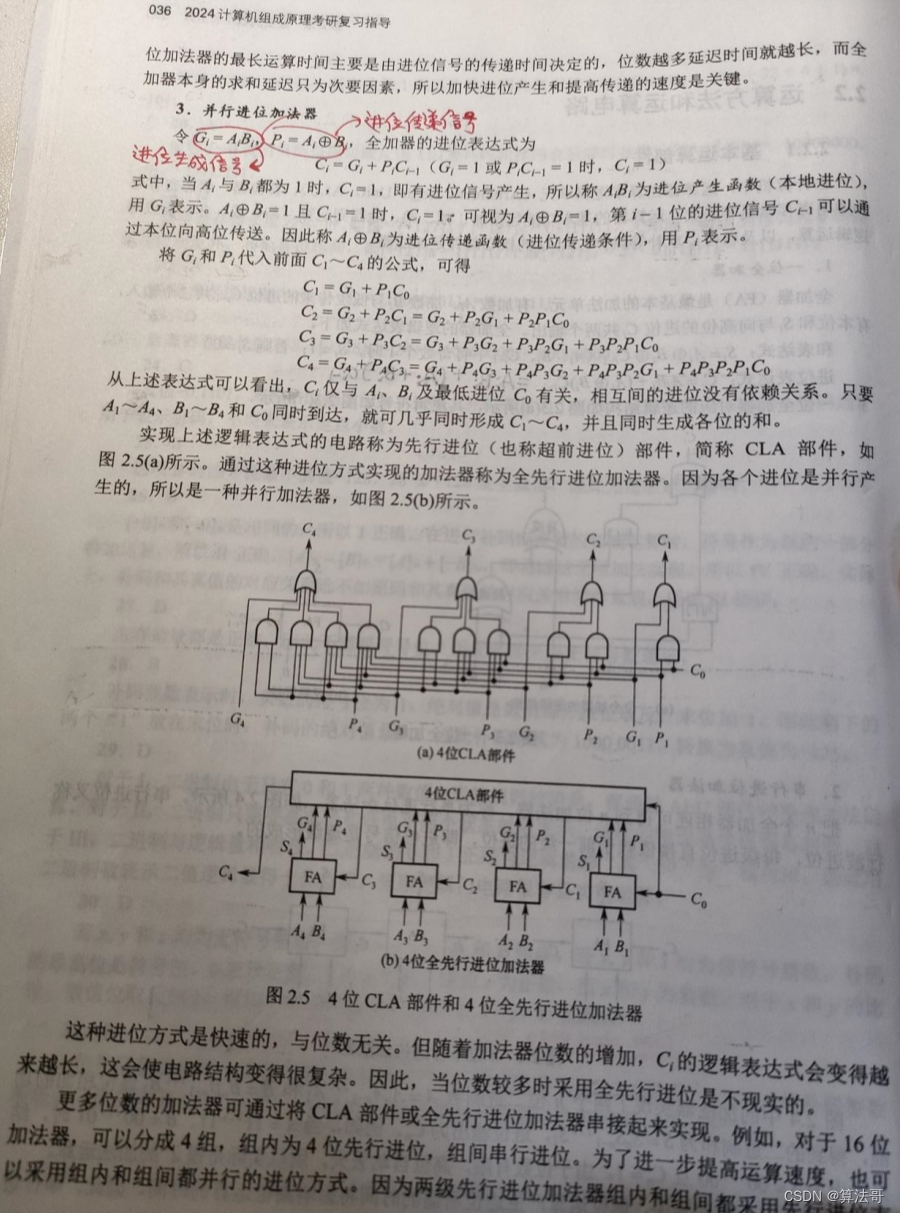

由上面C1~C4的公式,就可以画出下面的电路图:

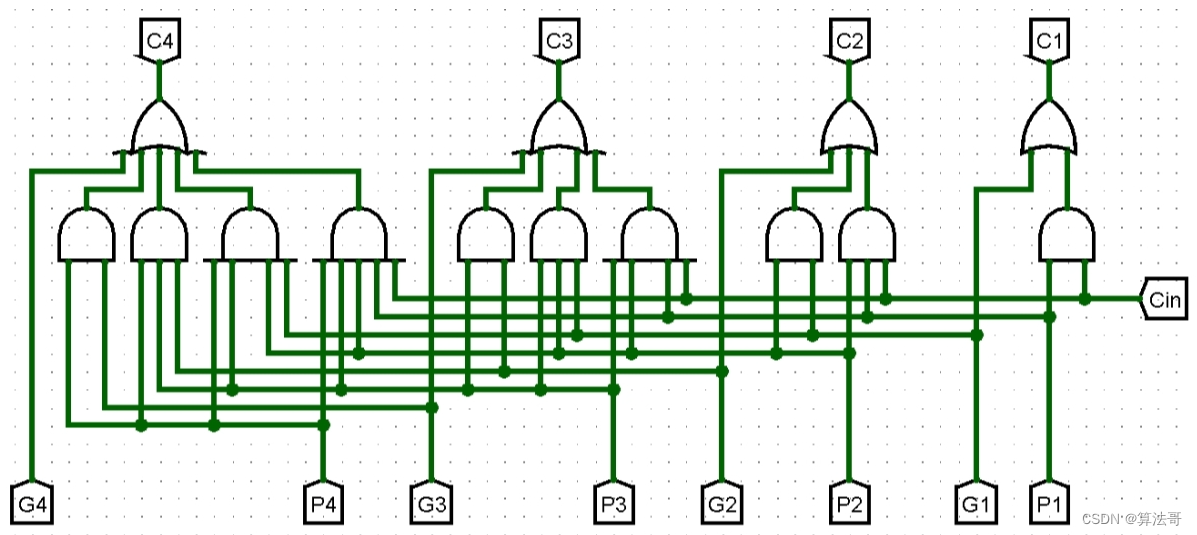

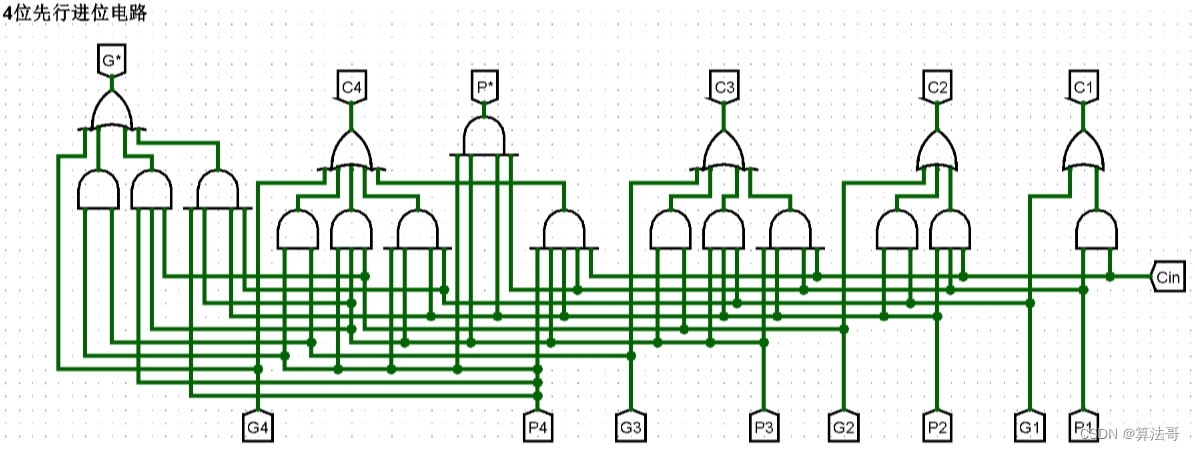

实验中的G*为进位产生信号等于G4+P4G3+P4P3G2+P4P3P2P1

P*为进位传递信号等于P4P3P2P1

所以4位先行进位电路74182的电路图如下:

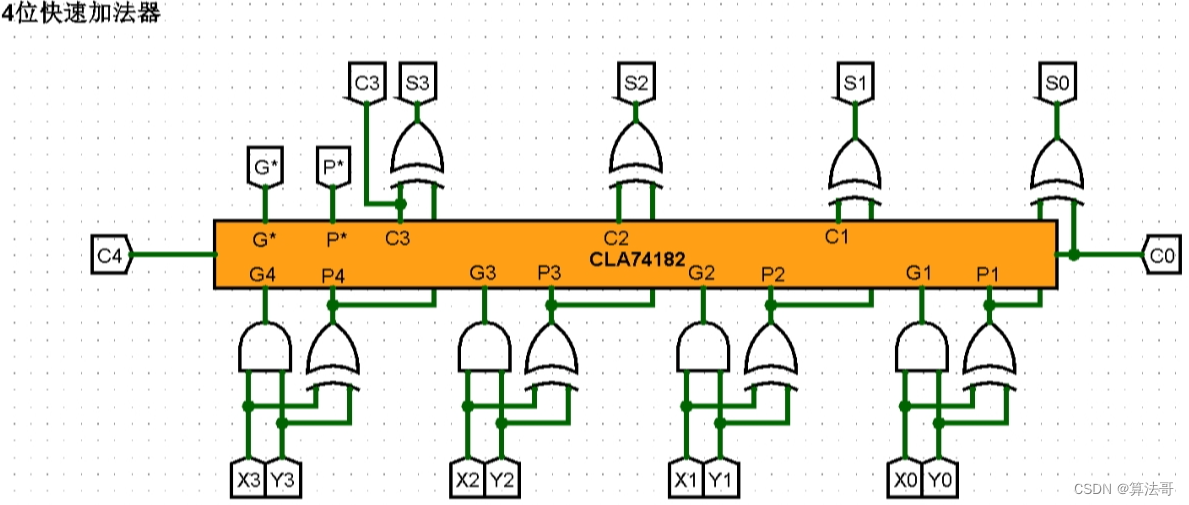

4位快速加法器

图中的CLA74182为先行进位电路74182(就是把上一个电路图封装起来的样子),然后因为CLA需要输入的是P1 G1 P2 G2 P3 G3 P4 G4,所以把X0和Y0异或后输进去就是P1,X0和Y0与一下就是G1,然后S是和表达式等于X⊕Y⊕Ci-1。依照这些逻辑表达式就能很快将4位快速加法器的电路画好,如下图所示:

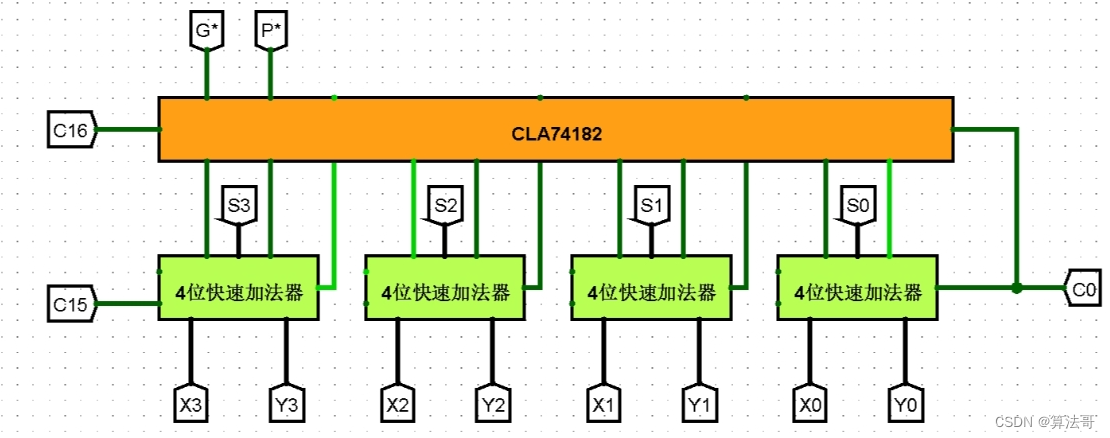

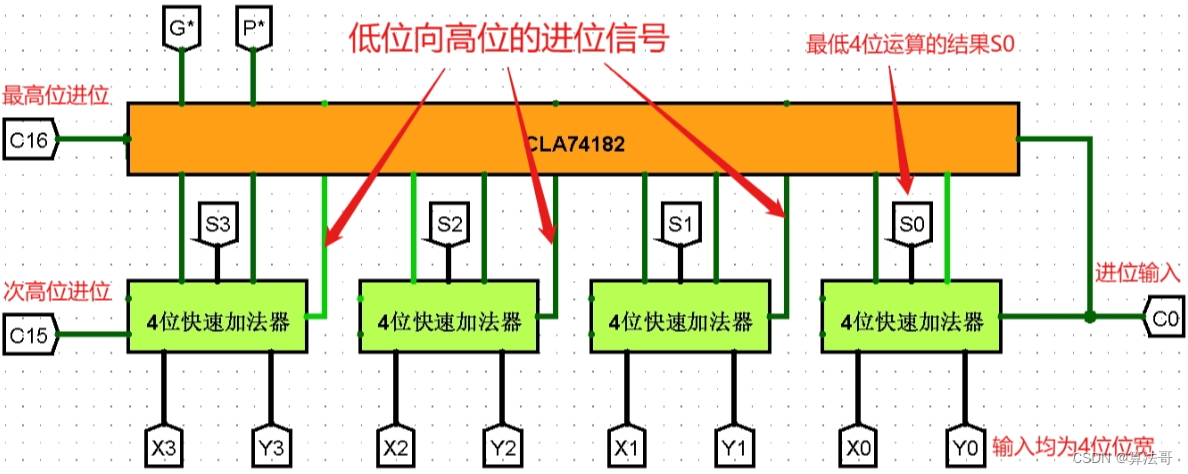

16位快速加法器设计

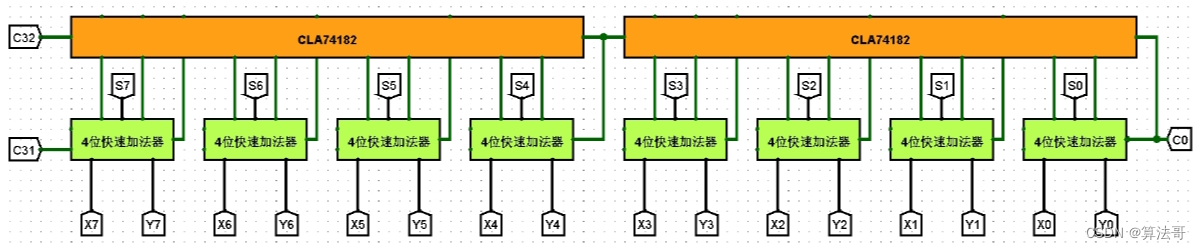

32位快速加法器设计

32位快速加法器设计原理与16位快速加法器设计原理一样,只需要把两块16位快速加法器串在一起即可,如下图:

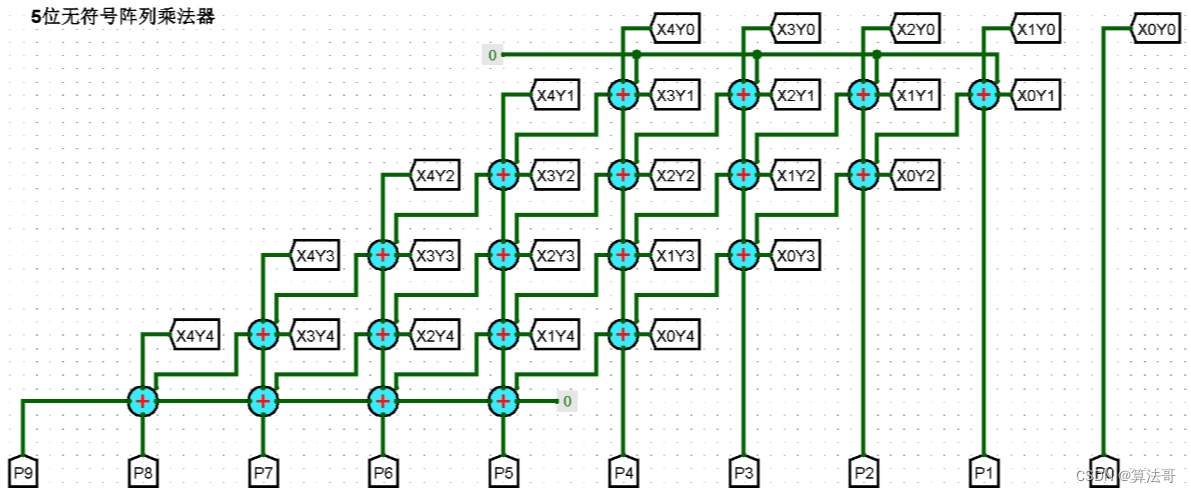

5位无符号阵列乘法器

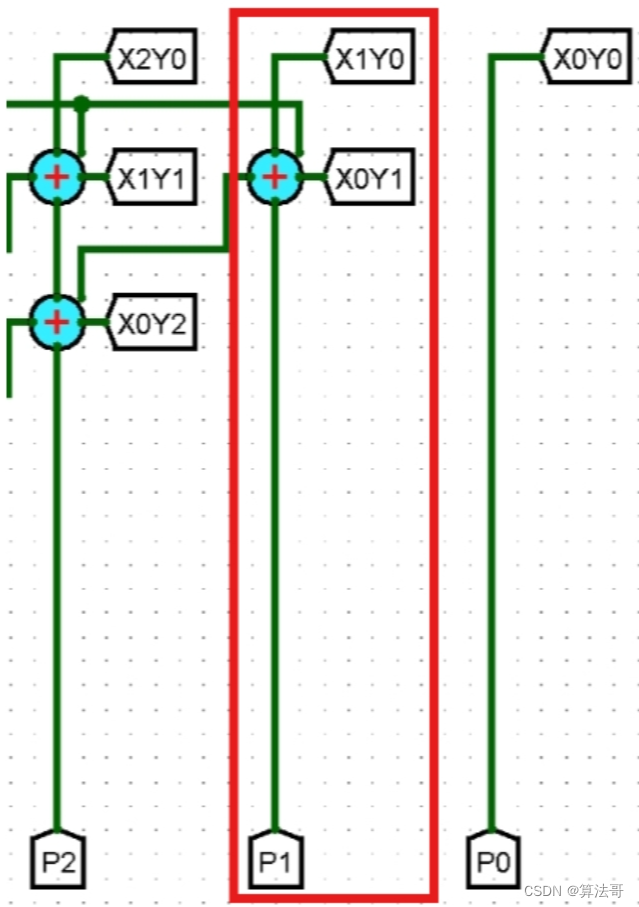

先上电路图:

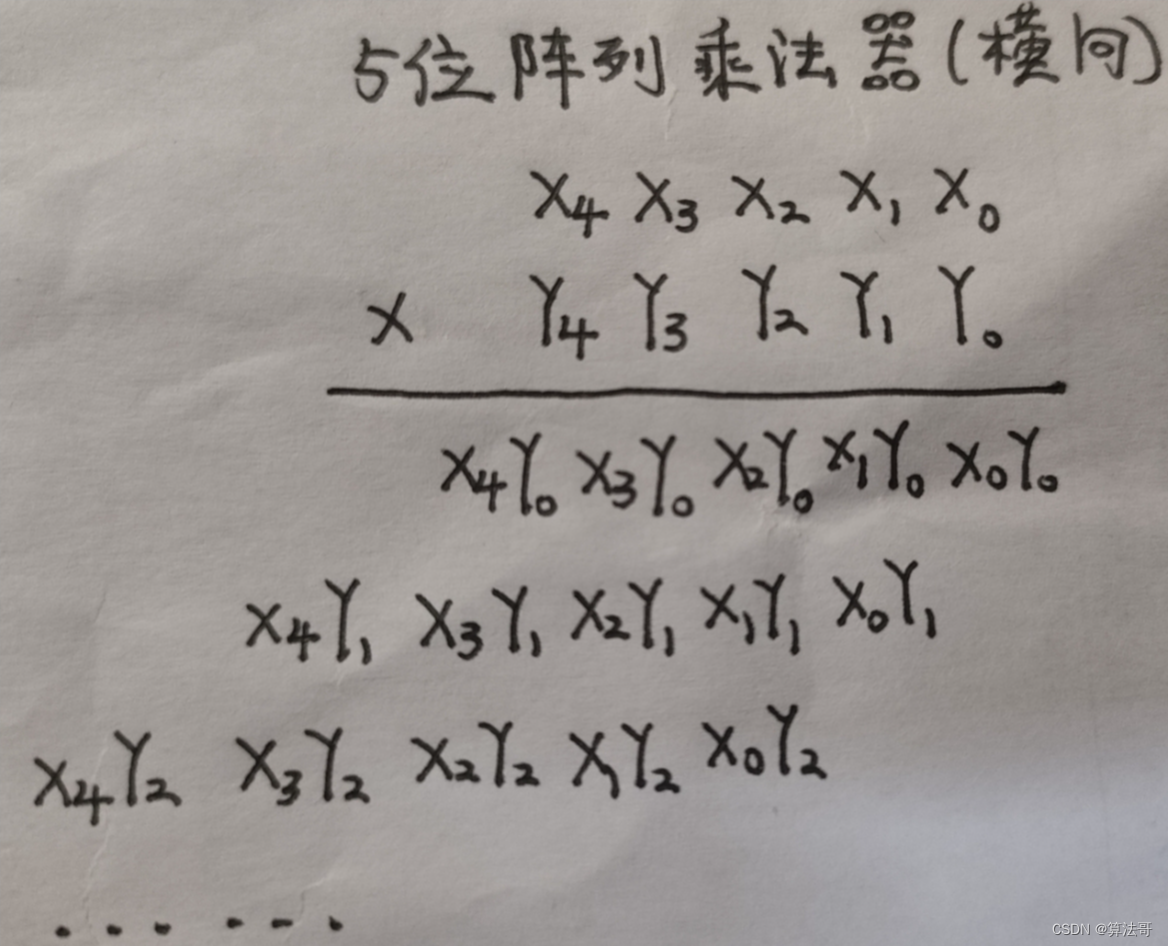

对于这个电路,我们只需要搞清楚其中的一个就行。上面图中的X1Y0和X0Y1是什么?看下面这张图就很容易理解了。

其实就是乘数的每一位与被乘数的每一位相乘。所以就只需要把竖着对应的乘积相加就完事了。

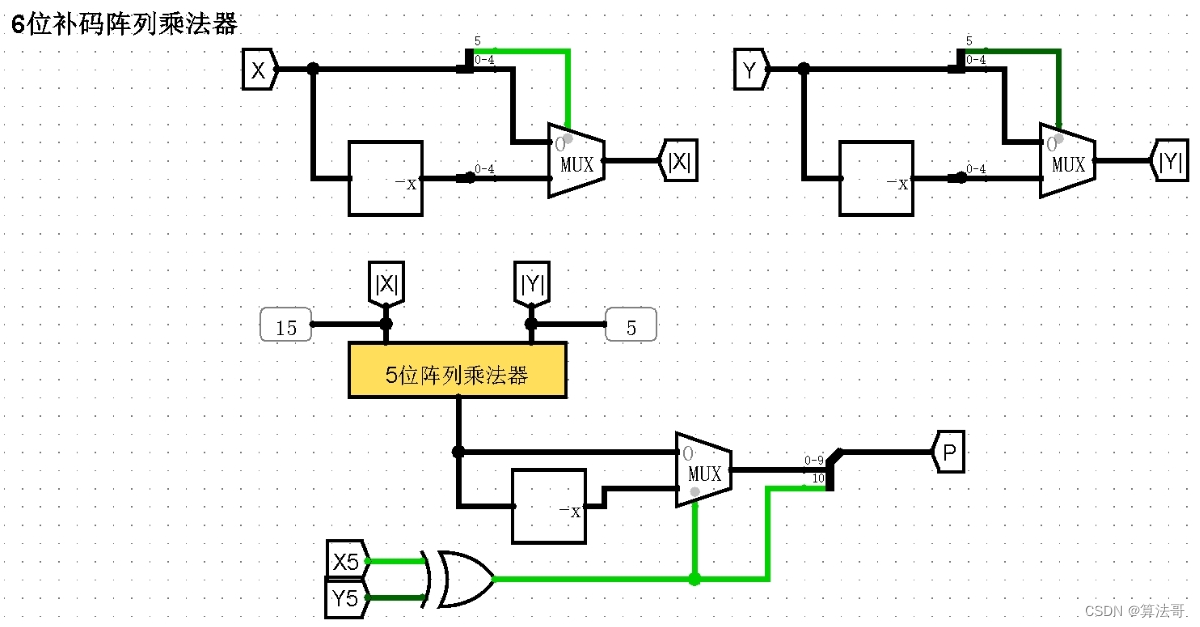

6位补码阵列乘法器

X5和Y5是两个数的最高位,也就是符号位,上面乘法的计算是将两个数的符号位与数值位分开来算的,数值位的绝对值输入5位阵列乘法器进行运算,而下面将X5和Y5进行异或操作,若X5与Y5同号,即最终结果为正,则MUX多路选择器的输入控制信号sel=0,则直接输出多路选择器的0路。若异或结果为1,则X5与Y5是异号的,即最终结果为负。此时MUX多路选择器的输入控制信号sel=1,将运算的结果求补(标有-x的是求补器)后从MUX的1路输出。

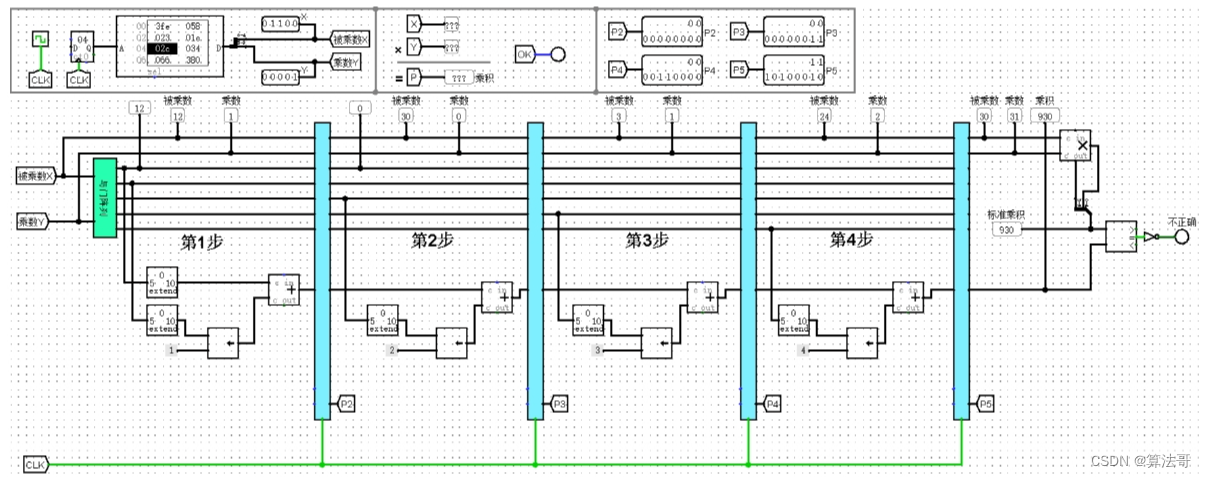

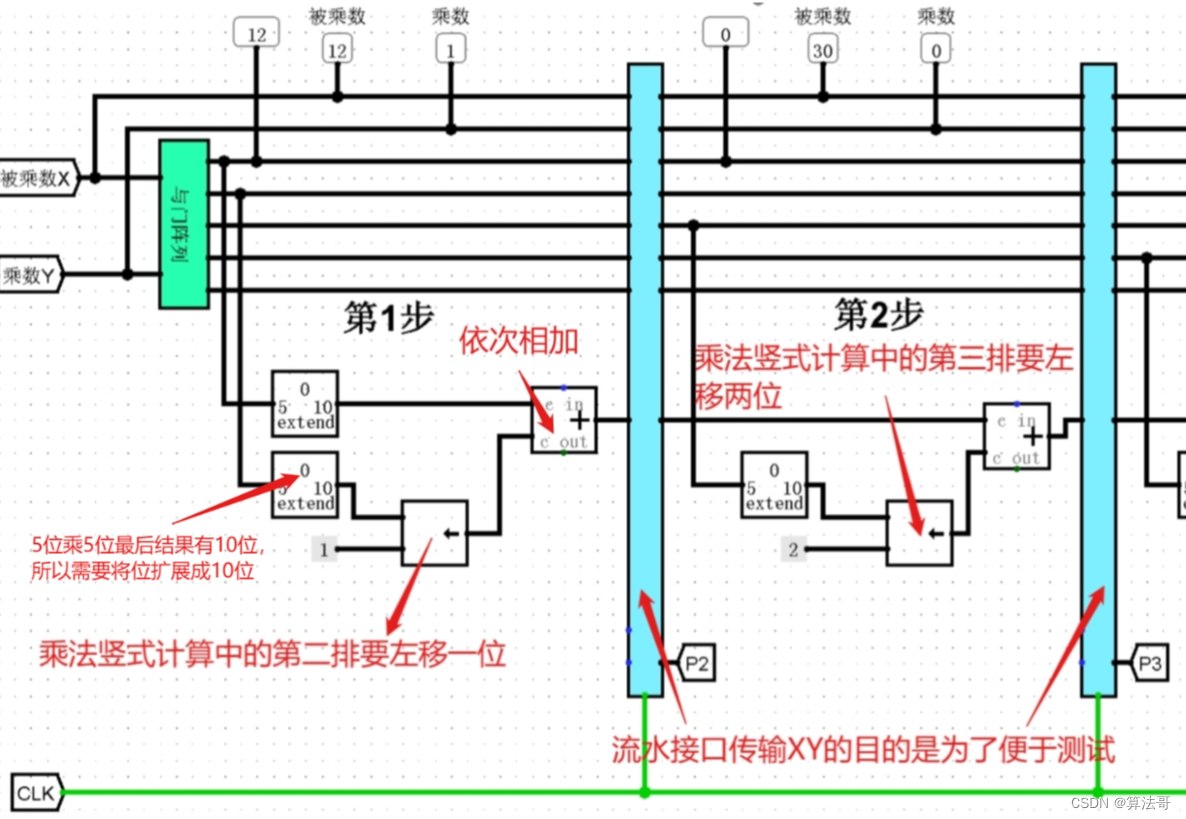

5位无符号乘法流水线

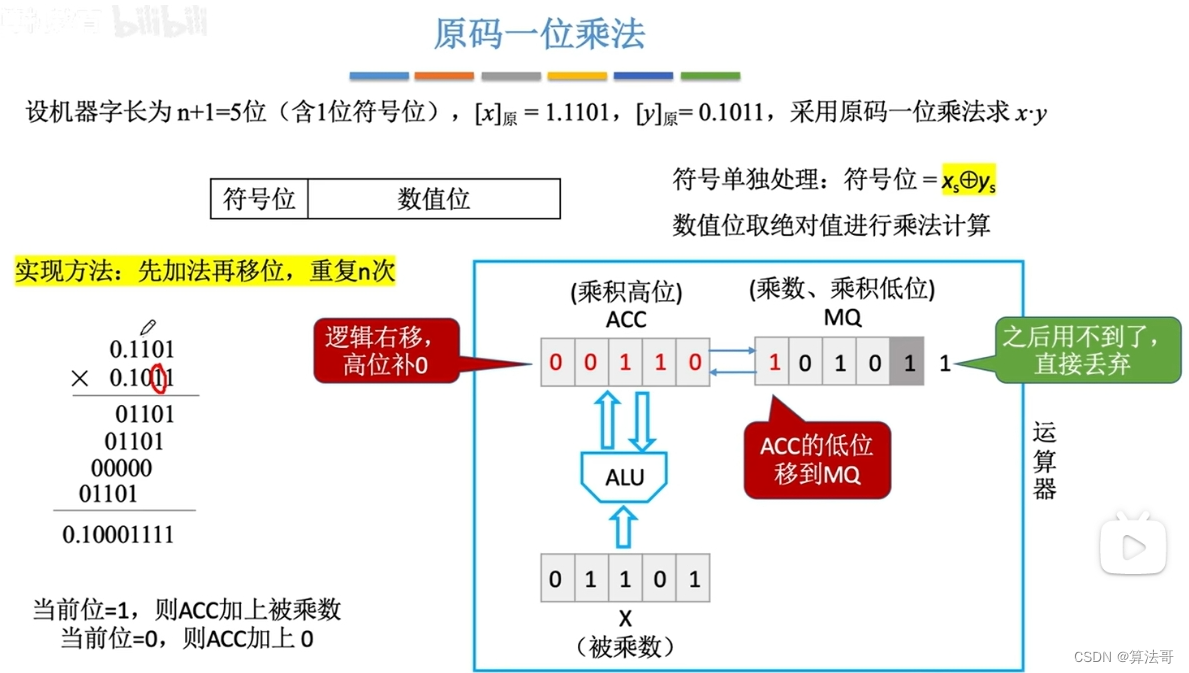

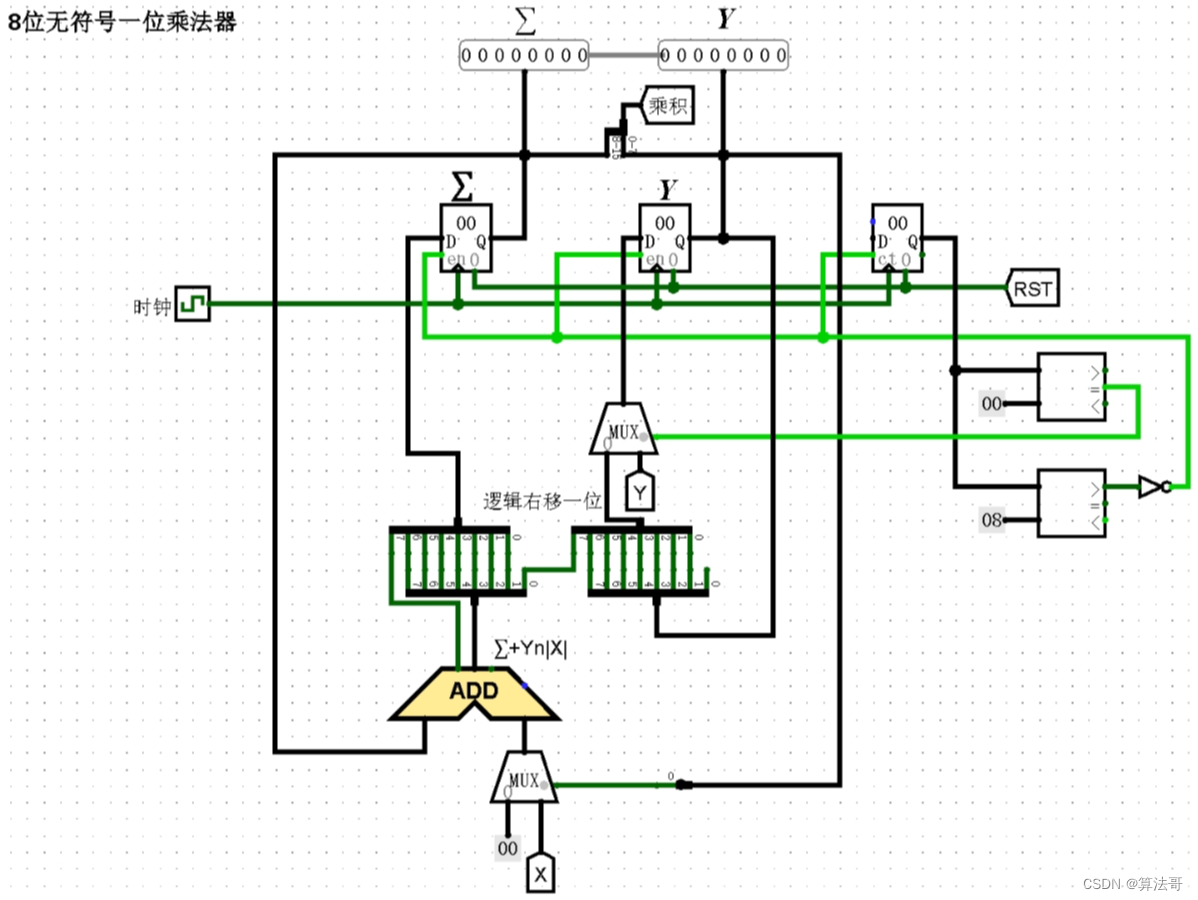

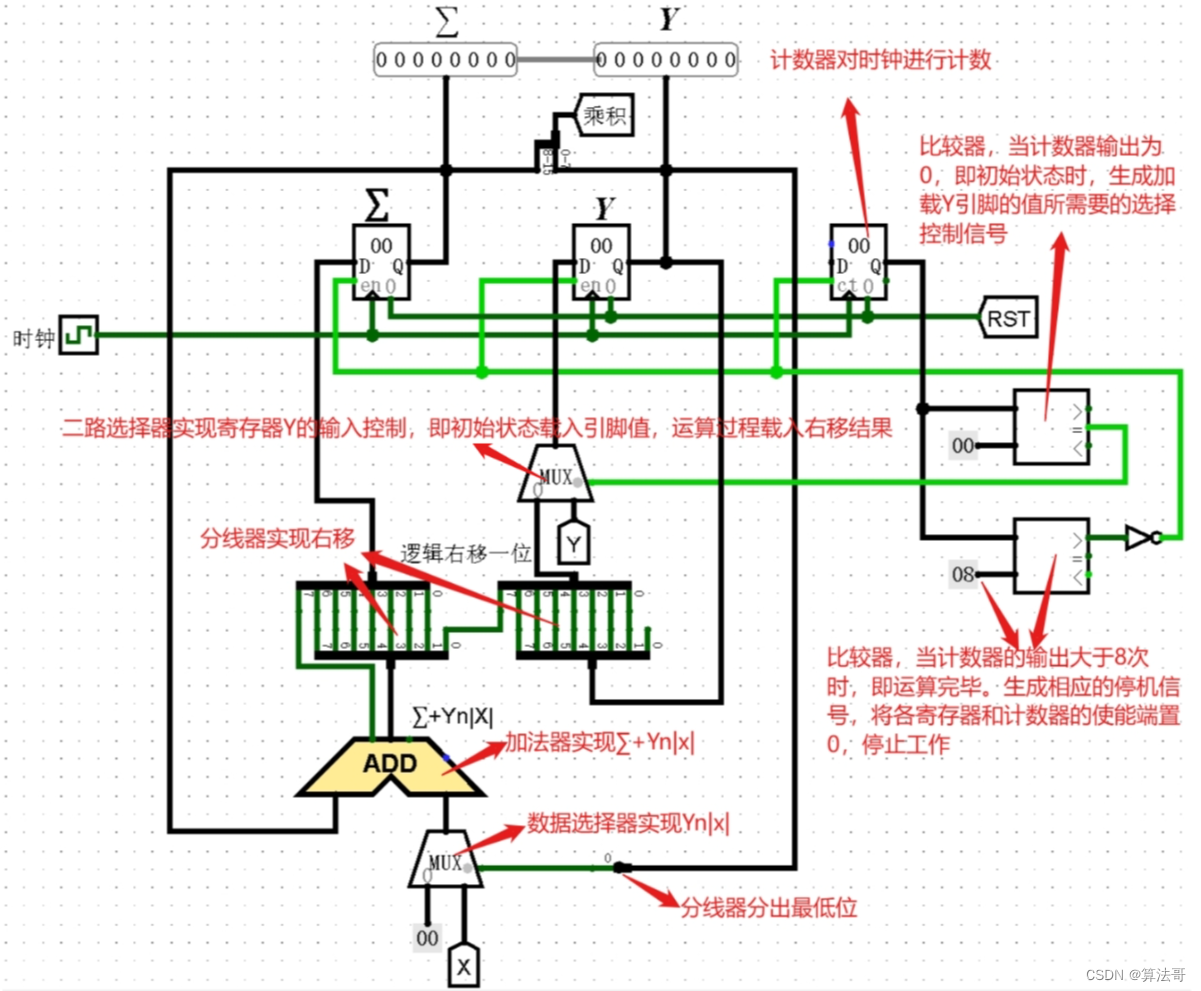

原码一位乘法器

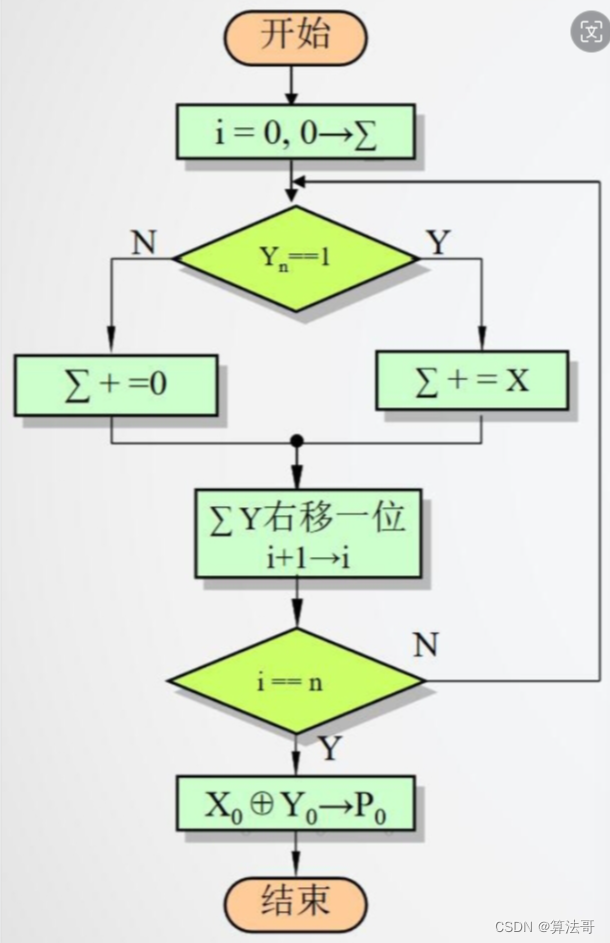

原码一位乘法流程:

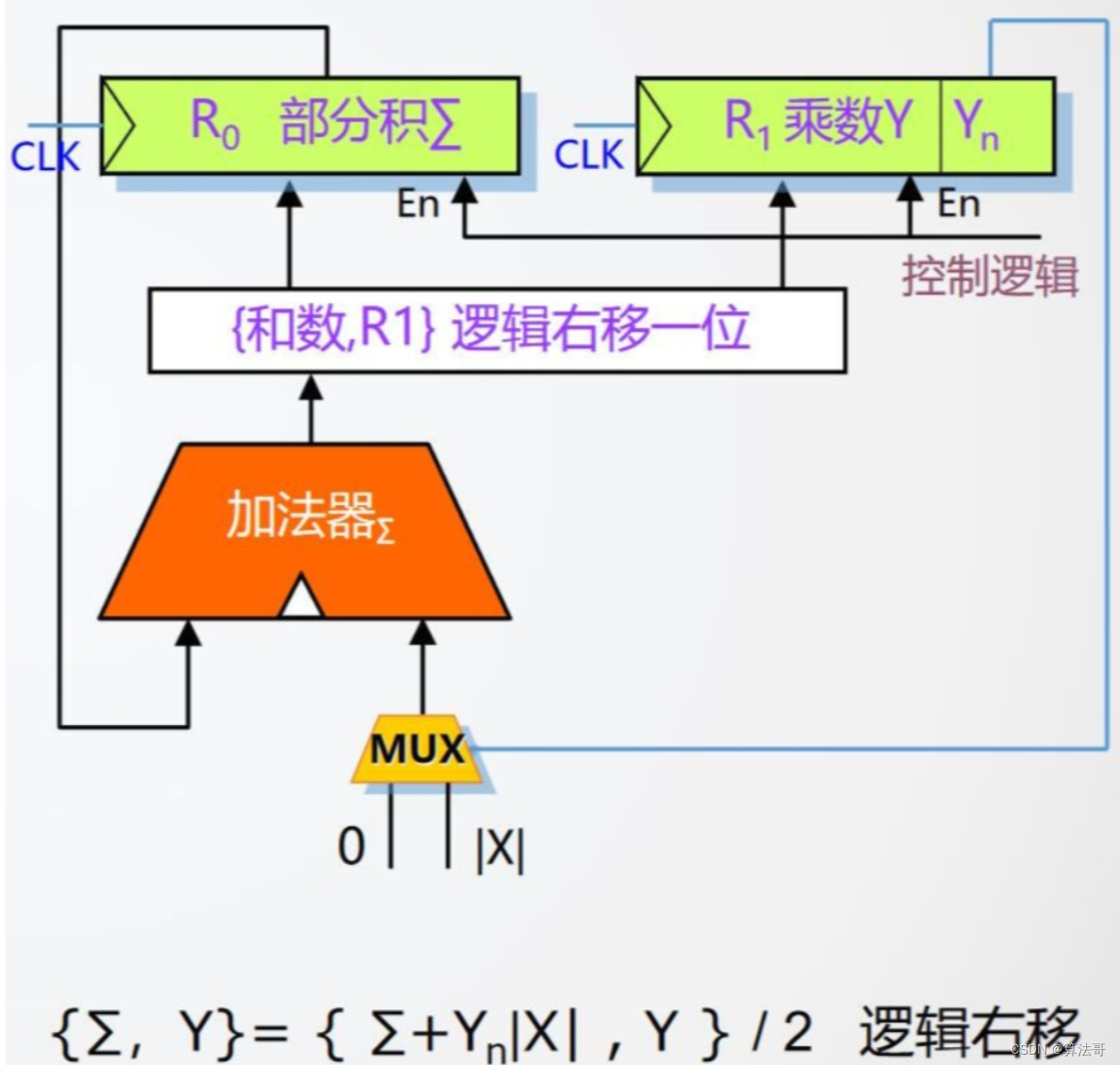

原码一位乘法的硬件逻辑:

具体课程可参考b站王道计算机组成原理P22

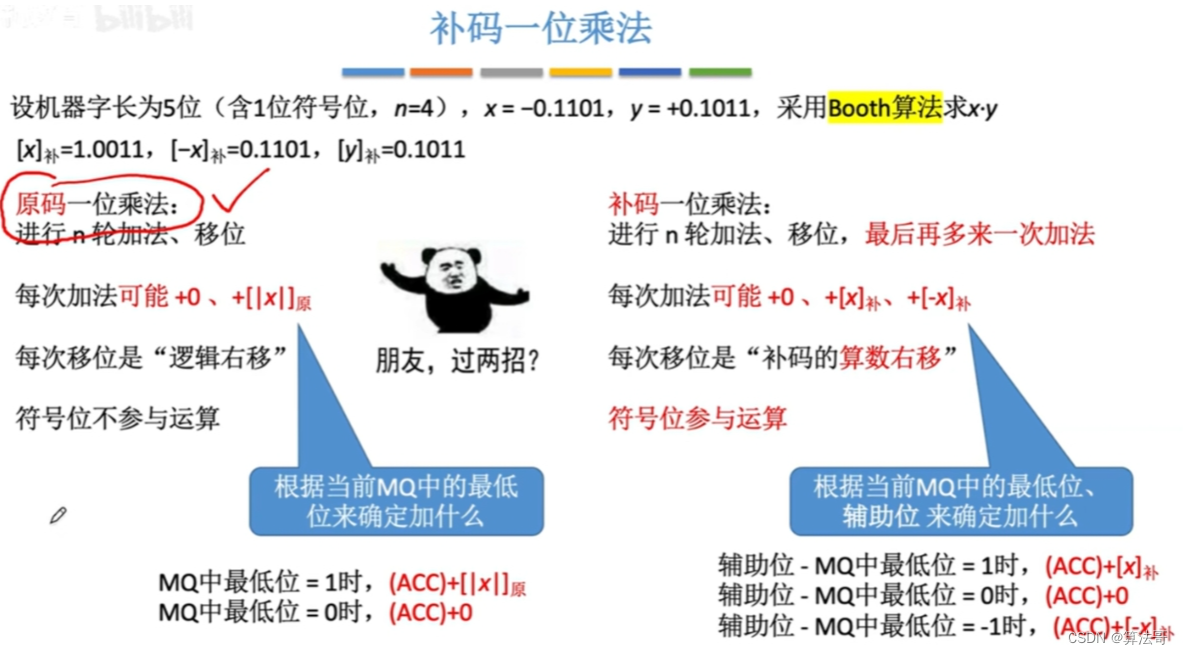

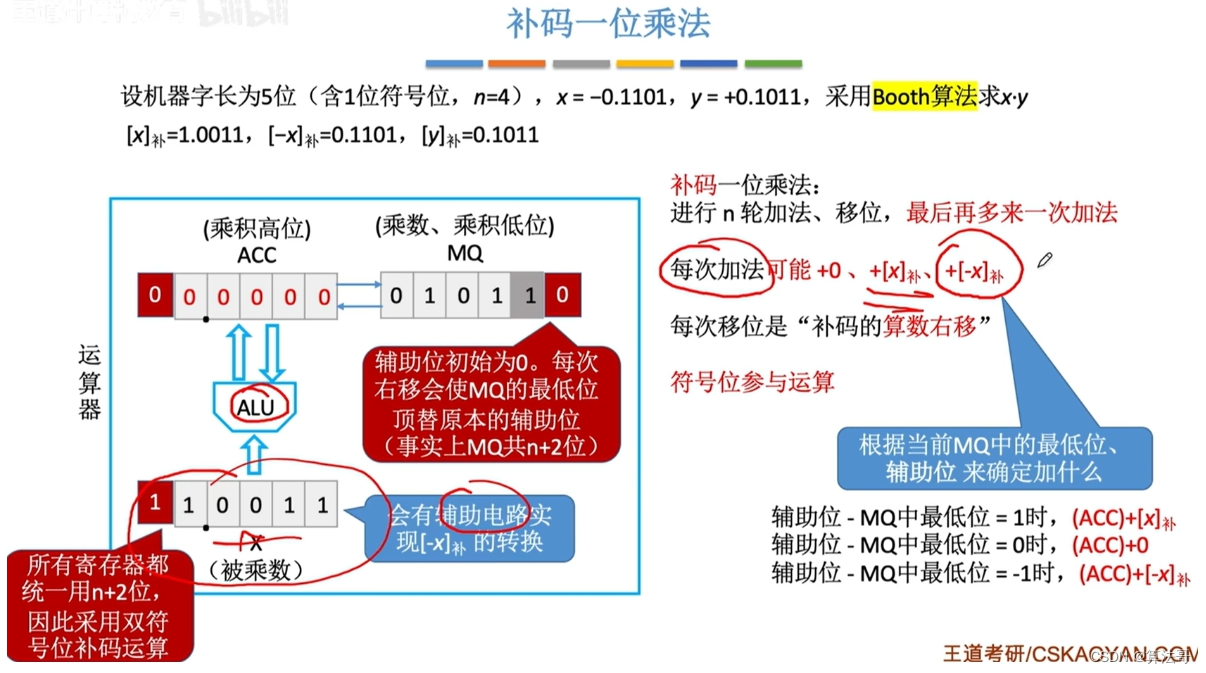

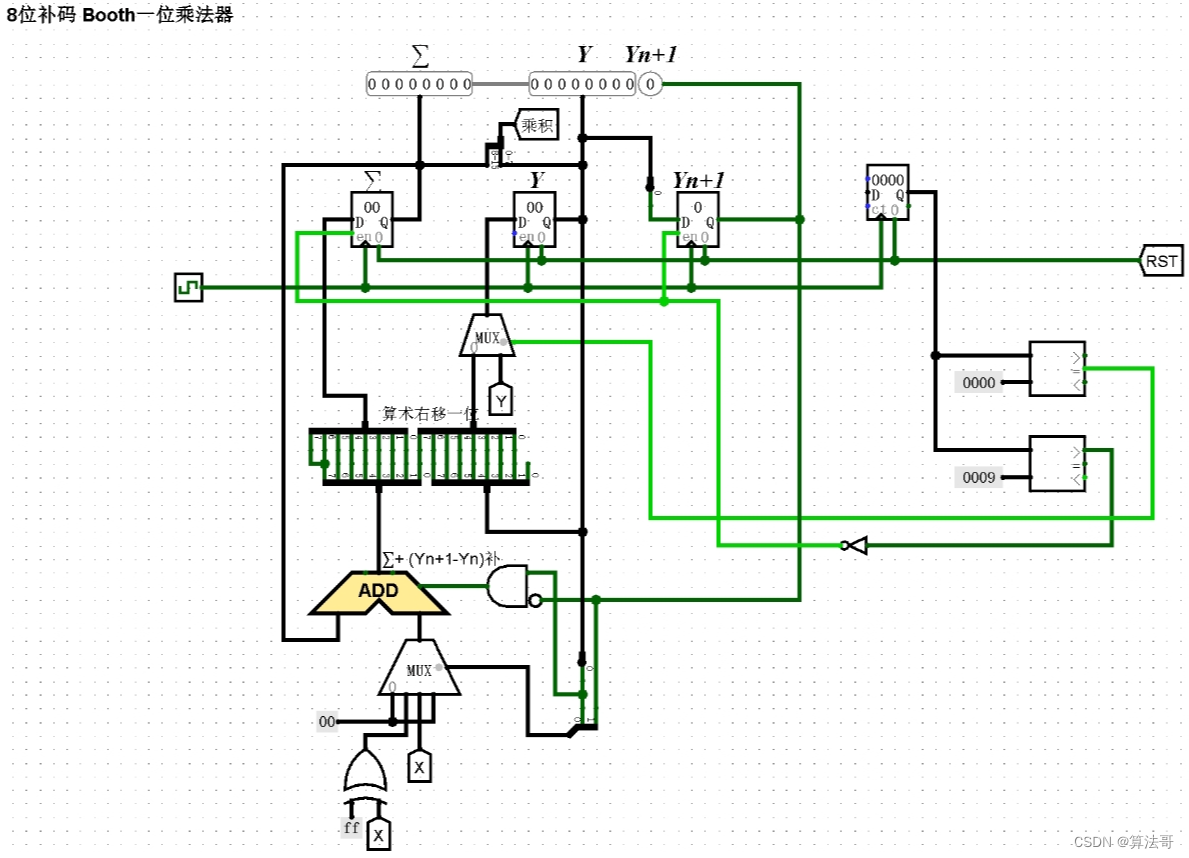

补码Booth一位乘法器

具体课程可参考b站王道计算机组成原理P23

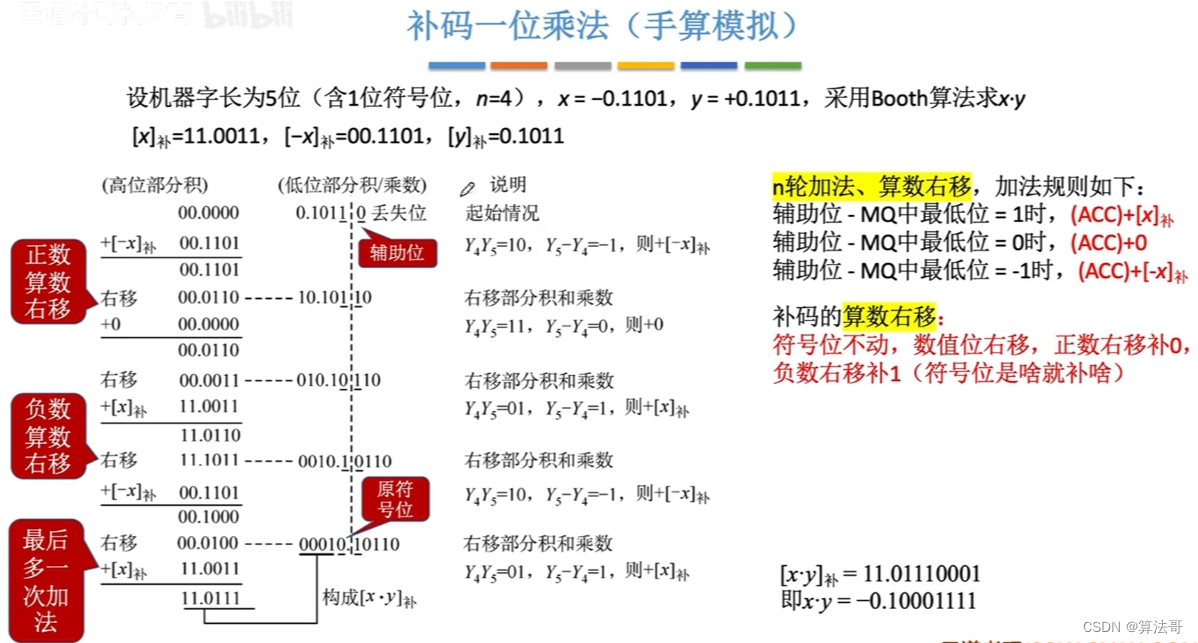

再结合手算过程来理解一下补码乘法的过程

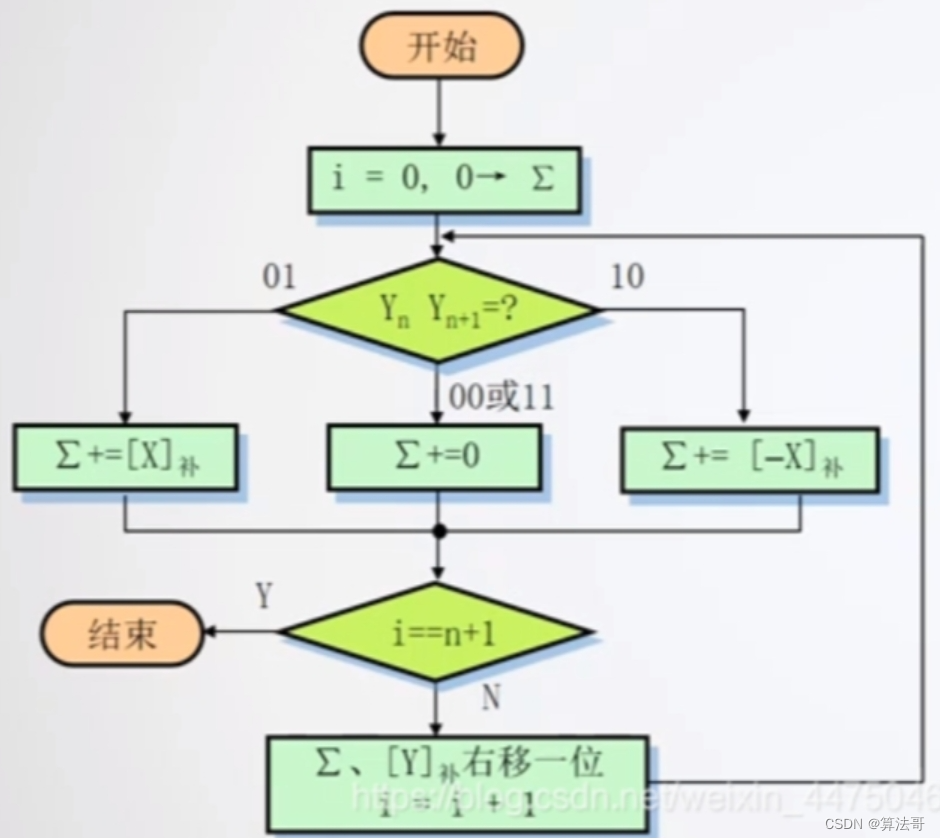

补码一位乘法流程:

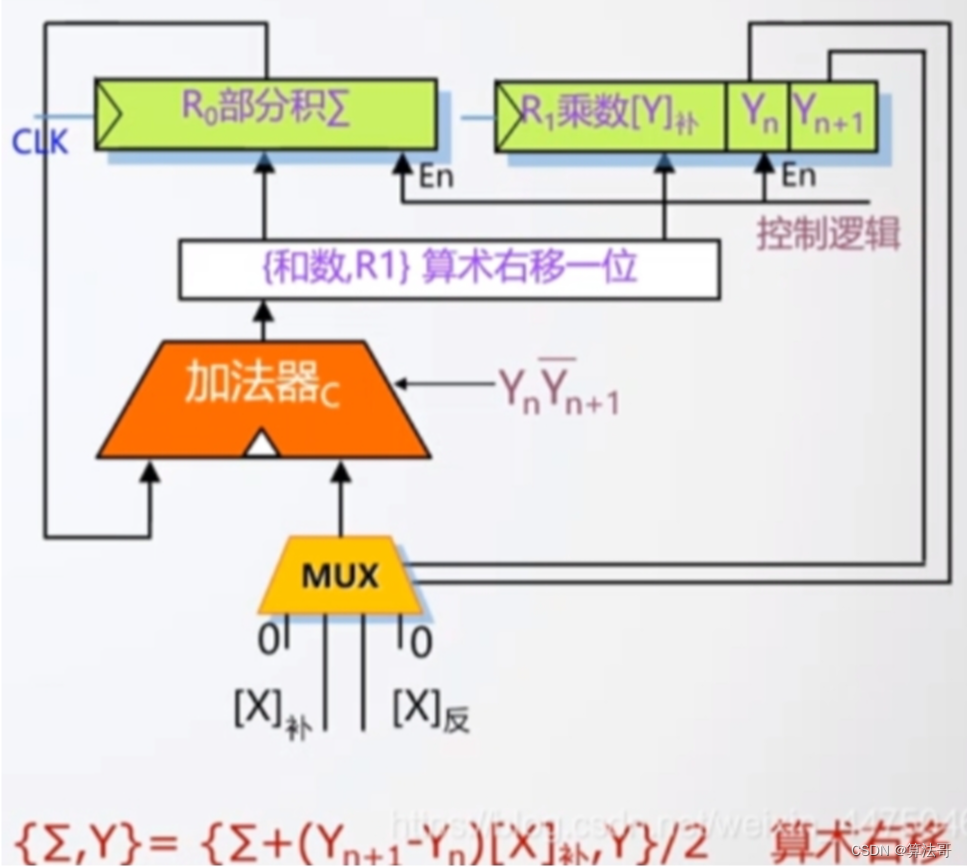

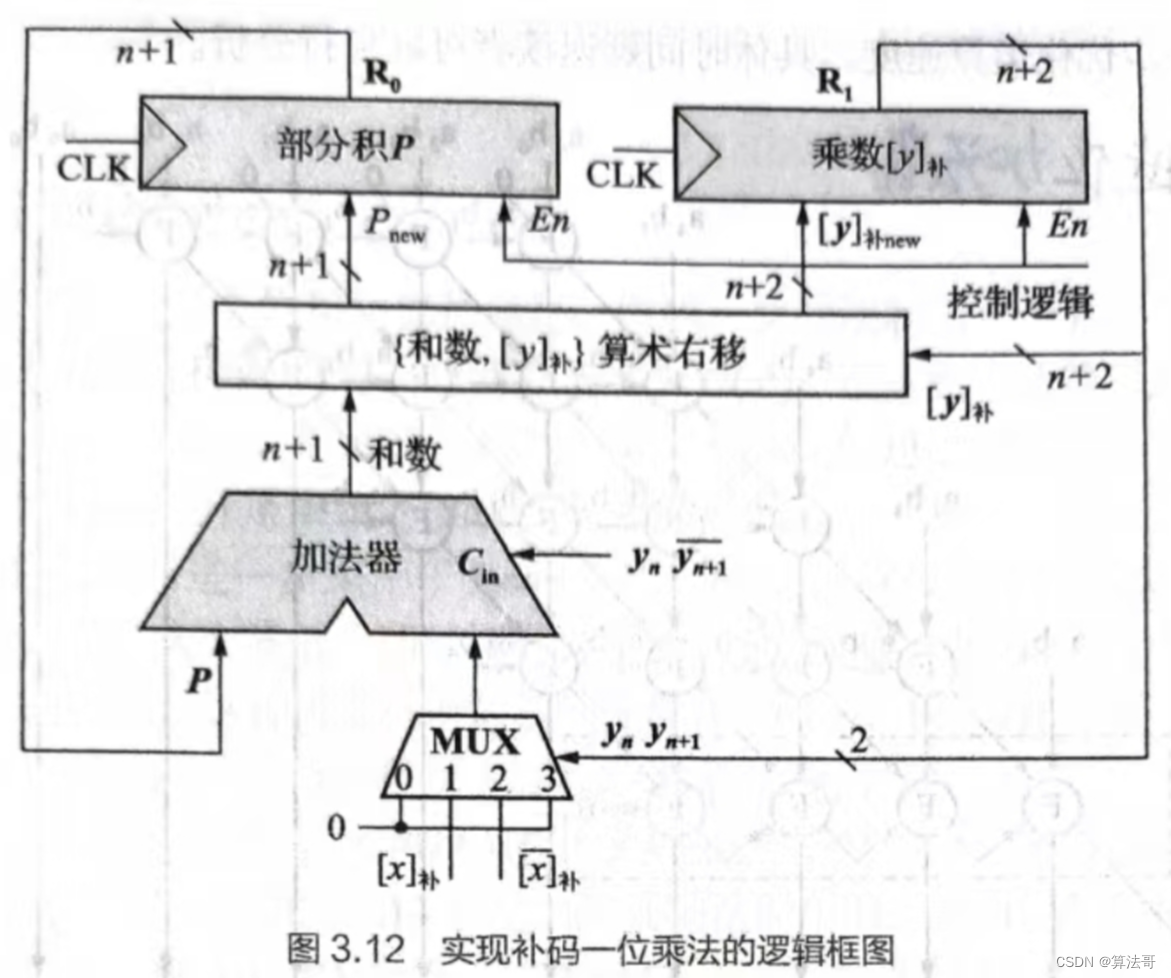

补码一位乘法的硬件逻辑:

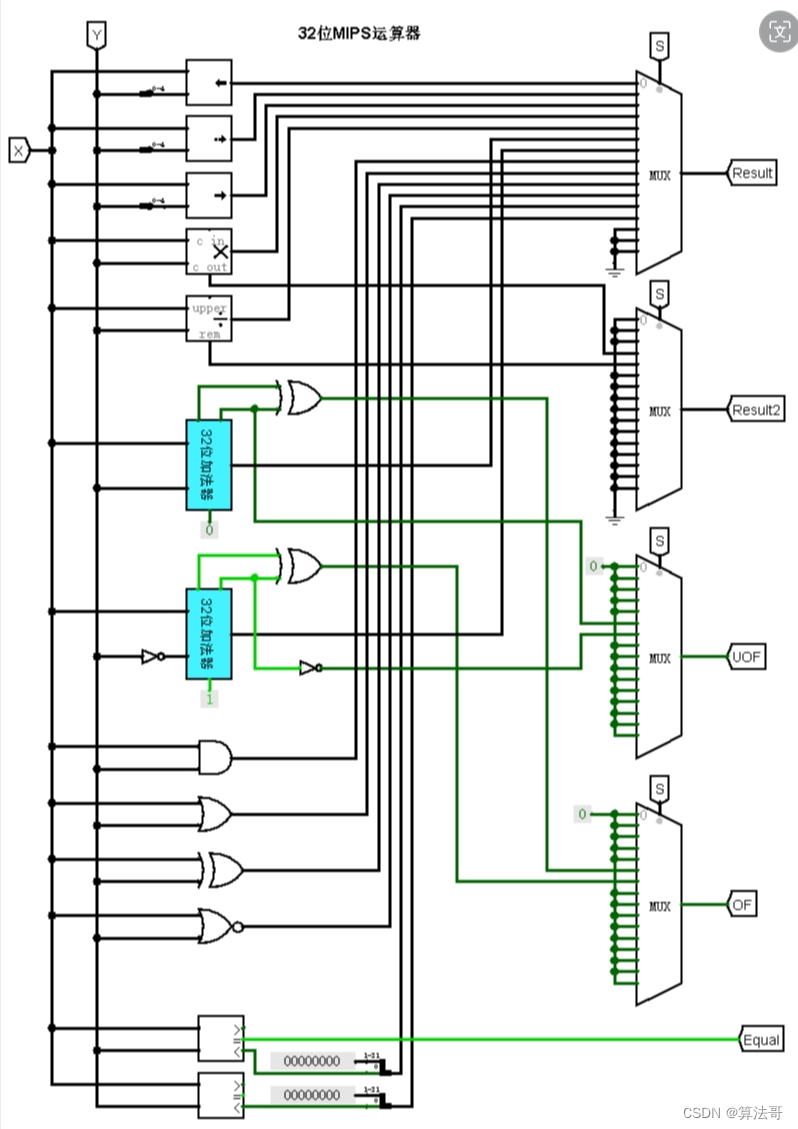

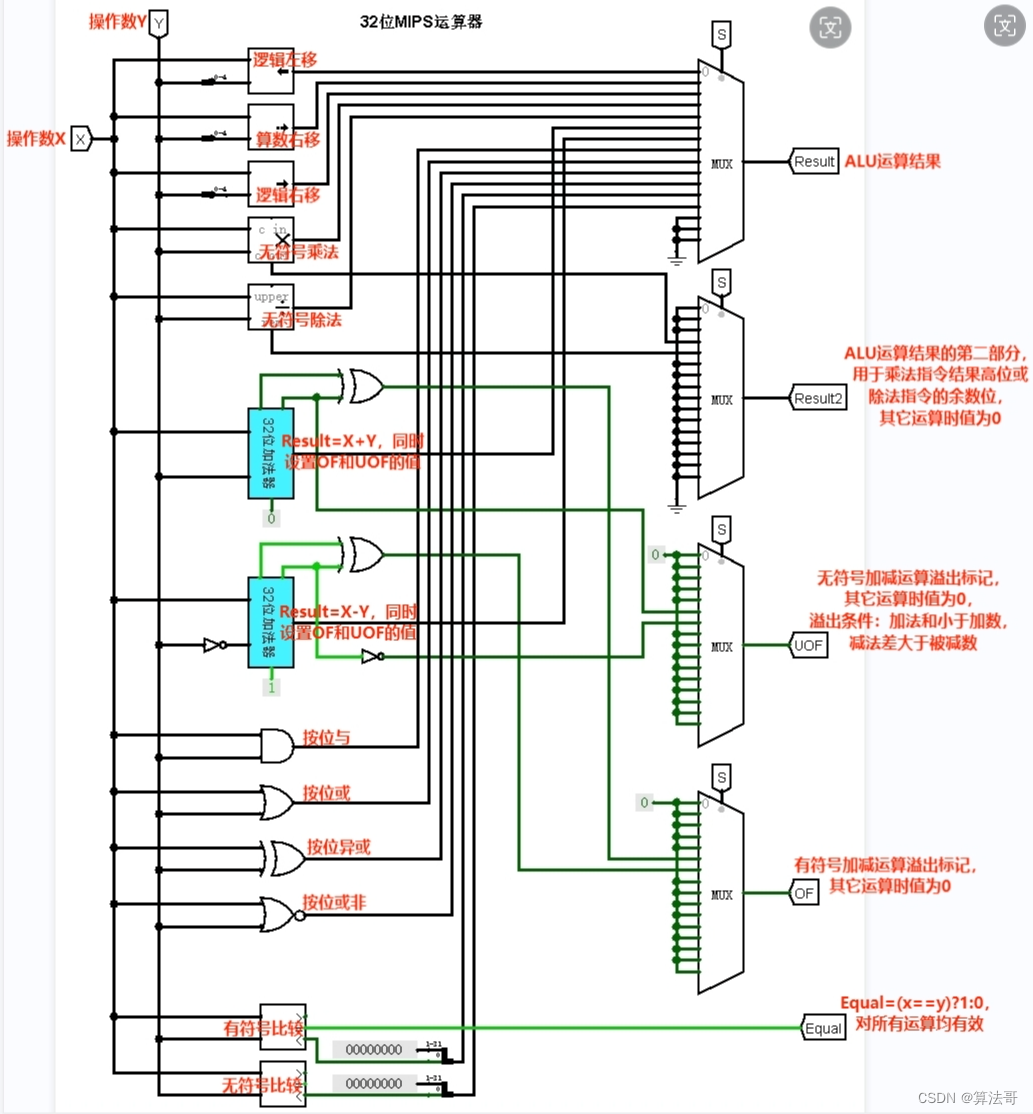

32位MIPS运算器

先上电路图,如下:

电路引脚及ALU的op功能表

| 信号 | 输入/输出 | 位宽 | 说明 |

|---|---|---|---|

| X | 输入 | 32位 | 操作数X |

| Y | 输入 | 32位 | 操作数Y |

| ALU_OP | 输入 | 4位 | 运算器功能码,具体功能见下表 |

| Result | 输出 | 32位 | ALU运算结果 |

| Result2 | 输出 | 32位 | ALU结果第二部分,用于乘法指令结果高位或除法指令的余数位,其它运算时值为零 |

| OF | 输出 | 1位 | 有符号加减运算溢出标记,其它运算时值为零 |

| UOF | 输出 | 1位 | 无符号加减运算溢出标记,其它运算时值为零,溢出条件(加法和小于加数,减法差大于被减数) |

| Equal | 输出 | 1位 | Equal=(x==y)?1:0,对所有运算均有效 |

| ALU_OP | 十进制 | 运算功能 |

|---|---|---|

| 0000 | 0 | Result = X << Y 逻辑左移(Y取最低五位)Result2=0 |

| ( Y0001 | 1 | Result = X >>> Y 算数右移(Y取最低五位)Result2=0 |

| 0010 | 2 | Result = X >> Y 逻辑右移(Y取最低五位)Result2=0 |

| 0011 | 3 | Result = (X * Y)[31:0];Resual2=(X * Y)[63:32] 无符号乘法 |

| 0100 | 4 | Result =X/Y;Resual2=X%Y 无符号除法 |

| 0101 | 5 | Result =X+Y(Set OF/UOF) |

| 0110 | 6 | Result =X-Y(Set OF/UOF) |

| 0111 | 7 | Result =X & Y 按位与 |

| 1000 | 8 | Result =X or Y 按位或 |

| 1001 | 9 | Result =X⊕Y 按位异或 |

| 1010 | 10 | Result =~(X or Y) 按位或非 |

| 1011 | 11 | Result =(X < Y) ? 1 : 0 符号比较 |

| 1100 | 12 | Result =(X < Y) ? 1 : 0 无符号比较 |

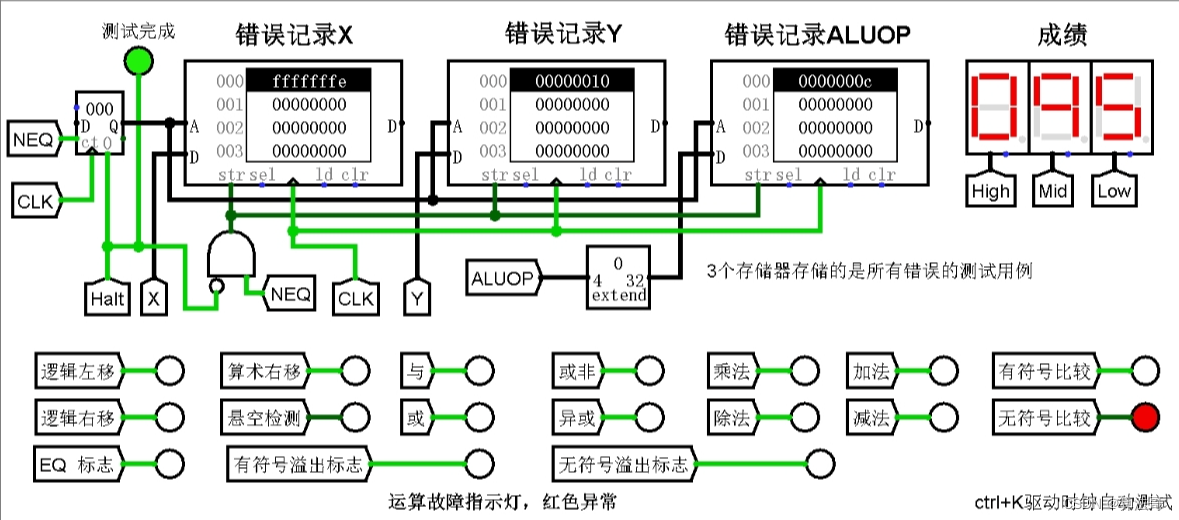

电路测试

设计思路

先构造出每一种功能的输出,再根据OP的值来选择输出:

0~2:分别用一个移位器实现,设置对应的属性;

3~4:分别用自带的乘法器、除法器实现;

5:加法,用封装好的32位加法器,OF判断最高位进位和符号位进位是否一致,UOF判断是否有进位(需一个异或门),C0取0;

6:减法,用封装好的32位加法器,Y取反用一个非门实现,无符号数的减法溢出,带加减功能的ALU的进位取反后表示,有符号数的减法溢出,仍然用最高位和符号位是否相等来判断,C0取1;

7~10:分别用与门、非门、异或门、或非门实现;

11:比较器用补码型,结果0拓展;

12:比较器用无符号型,结果0拓展,还需要一个equal信号;

都构造好之后,根据OP的值输出resualt。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- Amos各版本安装指南

- YOLOv8优化:独家创新(SC_C_Detect)检测头结构创新,实现涨点 | 检测头新颖创新系列

- 光伏方案设计有什么注意点?

- 3.Pandas高级函数应用

- [AI工具推荐]AiRestful智能API代码生成

- 分库分表之Mycat应用学习三

- [Angular] 笔记 24:ngContainer vs. ngTemplate vs. ngContent

- 合宋(颂)祝融峰和贺兰山的爱情故事

- 思迈特2023 年度回顾:这一年,在不确定的时代里做好正确的事

- 【卡梅德生物】制备兔单抗常见问题及解决方法