vivado I/O和时钟规划设计流程步骤

I/O和时钟规划设计流程步骤

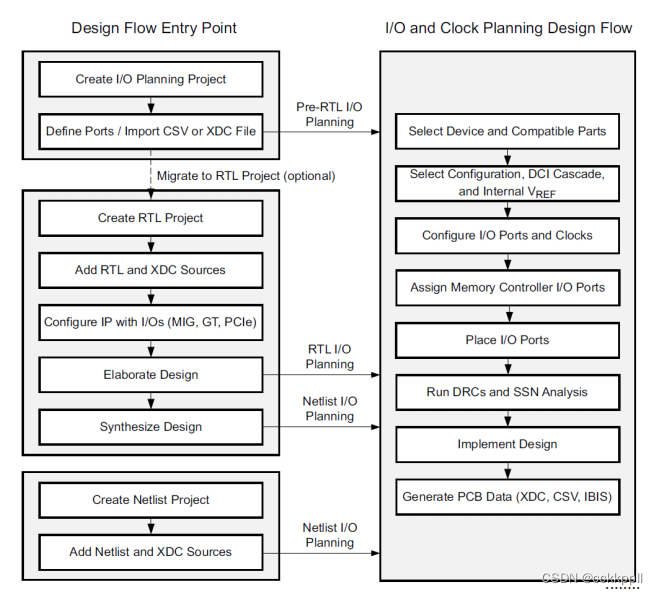

下图显示了左侧的项目设计流程步骤。水平箭头表示项目设计流程中可以执行I/O和时钟规划的点。中的步骤I/O和时钟规划设计流程如右图所示。

项目设计流程从一个空的I/O规划项目、RTL设计项目或合成后网表项目。使用这些项目类型中的任何一种,都可以执行以下操作I/O和时钟规划设计流程中的步骤:

1.选择设备和兼容部件

选择零件时,根据最终的资源估计确定设备大小设计根据PCB要求选择封装,例如到存储器的关键路径。Versal还有专用的硬盘控制器引脚,不能用于其他I/O操作。有关使用堆叠式硅互连(SSI)技术的设计,请参阅UltraFastFPGA和SoC的设计方法指南(UG949)。除了选定的零件还可以识别备用兼容部件,如定义备用兼容部件中所述部分或者,您可以选择一个受支持的目标设计平台板,其中包括AMD设备和其他组件提供强大的评估平台或快速产品开发平台。有关更多信息,请参阅使用平台进行I/O和时钟规划Board Flow。

2.选择配置、DCI级联和内部VREF

AMD设备每次通电时都必须进行配置。比特流加载到通过启用不同配置模式的特殊配置引脚连接设备。对于Versal自适应SoC,加载设备映像。中使用的配置模式应用程序可能会影响设计的I/O规划。确定和计划开始I/O分配之前的配置模式。配置模式不仅确定某些引脚的连接性,还确定所需的VCCO电压包括多功能引脚的I/O组。有关信息,请参阅设置设备配置模式。

根据I/O标准,数字控制阻抗(DCI)可以控制输出驱动器的阻抗或向驱动器、接收器或两者添加并联端接以匹配传输线的特性阻抗并提高信号完整性。DCI使用两个每个I/O组中的多用途参考引脚,用于控制驱动器或组中所有I/O的并行终止值。具有差分输入缓冲器的单端I/O标准需要参考电压(VREF)。您可以使用internal_VREF约束生成内部VREF,这将消除需要在PCB上提供特定的参考电压供应轨。在7个系列和AMD UltraScale? 架构,这可以释放给定I/O组中的多用途VREF引脚其他I/O端口分配。有关详细信息,请参见设置设备约束。

3.配置I/O端口和时钟

设备上的I/O端口支持多个与I/O相关的约束,睡眠和驾驶。配置这些端口以支持系统级设计所需的标准。I/O标准定义可能会影响引脚位置。例如,您可以将一些I/O标准组合在单个I/O组中,但不组合其他标准。欲了解更多信息,请参阅配置I/O端口。AMD器件被细分为时钟区域的列和行。时钟区域包含可配置逻辑块(CLB)、I/O组、数字信号处理(DSP)片、块随机存取存储器(RAM)、互连以及相关联的时钟资源。每个I/O存储体包含具有时钟功能的输入引脚,用于将系统或板上时钟带到设备上,以及转换为时钟路由资源。您必须计划使用这些时钟资源来分发在您的设备上为您的设计计时。Versal为高速I/O提供了特定的时钟不会错过全球计时。请注意确保正确地为这些I/O计时。有关详细信息,请参阅时钟规划。

注意:不能在I/O规划项目中执行时钟规划,因为时钟对象不是在这种类型的项目中定义。建议:AMD建议您使用Vivado IP目录中的时钟向导生成混合模式时钟管理器(MMCM)或锁相环(PLL)模块以定义时钟连接。有关信息,请参阅《时钟向导LogiCORE IP产品指南》(PG065)。你可以还通过高级I/O向导使用I/O接口设计生成时钟。

4.分配内存控制器I/O端口

内存IP使用预先设计的控制器和物理控制器定义内存控制器层(PHY),用于将FPGA设计与支持的外部存储器设备接口。高速内存控制器以及以太网IP和PCI Express?(PCIe)技术IP具有由时钟和偏斜需求驱动的特定引脚输出需求。您必须定义千兆收发器(GT)、PCIe的I/O物理引脚分配技术和内存IP作为IP定制的一部分。根据IP,要更改I/O分配,必须在中重新自定义IP设计有关使用和自定义IP的信息,请参阅Vivado Design Suite用户指南:使用IP(UG896)进行设计。对于UltraScale体系结构内存IP,I/O分配集成到标准I/O规划流中,不需要内存IP定制。有关更多信息,请参阅UltraScale体系结构内存的I/O规划IP。

注意:I/O规划项目不会从复杂IP的IP文件中读取物理引脚分配如内存控制器、PCIe或千兆收发器。请参阅带I/O的IP的I/O和时钟规划端口以获取更多信息。

5.放置I/O端口

您可以使用交互方式将设计中的I/O端口分配给设备上的封装引脚不同的方法。您可以选择单独的I/O端口或称为接口的I/O端口组在“I/O端口”窗口中,并将它们分配给“程序包”窗口中的程序包引脚或I/O设备窗口中的焊盘。高级I/O规划器也是半字节和存储体级别的工具引脚放置。此工具允许自动放置,可以理解所有I/O接口在XPIO库中,并一次有效地放置它们。有关信息,请参见放置I/O端口。您还可以让Vivado Design Suite使用信息自动放置I/O端口源自综合设计。有关信息,请参见自动放置I/O端口。

6.运行DRC和SSN分析

在完成I/O和时钟分配后,通过运行DRCs和同时开关噪声(SSN)分析。DRC验证当前设计并报告任何违反规定的情况。有关信息,请参阅跑步DRCs。SSN分析估计了同时切换输出可能导致的中断I/O组中的其他输出端口。计算和估计将I/O组特定的电气特性纳入预测,以识别潜在的噪声相关问题在您的设计中。有关信息,请参阅使用SSN分析。注:SSN分析估计旨在确定设计中潜在的噪声相关问题不作为最终设计签字标准。

建议:AMD建议您在合成后,在实施以及实施后。这使您能够在设计的早期发现问题

7.实施设计

您必须在生成比特流以配置AMD设备之前实现该设计。在实施过程中,Vivado工具将设计元素放置在设备资源上设计网络,并进行优化以减少功率和闭合时序。欲了解更多信息,请参阅Vivado Design Suite用户指南:合成(UG901)和Vivado设计套件用户指南:实施(UG904)。

8.生成PCB数据(XDC、CSV、IBIS)

I/O和时钟规划是一个迭代过程,包括信息交换在PCB或系统设计者与FPGA设计者之间。它可以从的输入开始使用从CSV文件导入的目标设备引出线的PCB。当您完成中的步骤时I/O和时钟规划流程,您可以返回引脚输出以及的设备型号信号完整性分析,使用逗号分隔值(CSV)文件和I/O缓冲区信息规范(IBIS)模型。有关详细信息,请参见与接口系统设计器。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 深度解析Python关键字:掌握核心语法的基石(新版本35+4)

- 【Spark精讲】Spark on Hive性能优化

- HarmonyOS-AppStorage:应用全局的UI状态存储

- Mybatis——实现增删改查(详细操作)

- 图像分割实战-系列教程13:deeplabV3+ VOC分割实战

- c语言:成本100元,40%的利润怎么计算|练习题

- 用redis广播消息更新集群环境下本地缓存

- 深入解析JavaScript中的装饰器模式、call/apply和转发

- HTML5+CSS3小实例:不一样的超链接下划线

- 第三章 课后习题(完整版)