【Xilinx Vivado 2019.2 BD 编译出错(地址位宽不对):[IP_Flow 19-3478] Validation failed...】

发布时间:2024年01月10日

编译BD出错描述

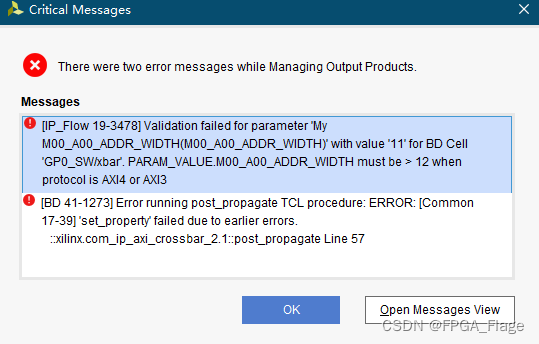

在开发ZYNQ的PL部分时,编译所设计的Block Design时出现[IP_Flow 19-3478]错误,详细错误为:

- [IP_Flow 19-3478] Validation failed for parameter ‘My M00_A00_ADDR_WIDTH(M00_A00_ADDR_WIDTH)’ with value ‘11’ for BD Cell ‘GP0_SW/xbar’. PARAM_VALUE.M00_A00_ADDR_WIDTH must be > 12 when protocol is AXI4 or AXI3;

- [BD 41-1273] Error running post_propagate TCL procedure: ERROR: [Common 17-39] ‘set_property’ failed due to earlier errors.::xilinx.com_ip_axi_crossbar_2.1::post_propagate Line 57。

具体报错如图所示:

编译环境

- 软件:Vivado 2019.2

- 运行环境:Windows10

- 工程芯片:xc7z035ffg900-2

原因分析

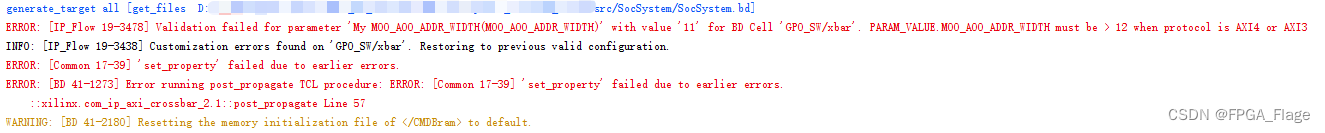

在报错图片中有说到参数无效, [IP_Flow 19-3478] Validation failed for parameter ‘My M00_A00_ADDR_WIDTH(M00_A00_ADDR_WIDTH)’ with value ‘11’ for BD Cell ‘GP0_SW/xbar’. PARAM_VALUE.M00_A00_ADDR_WIDTH must be > 12 when protocol is AXI4 or AXI3。

而参数无效的原因是:M00_A00_ADDR_WIDTH 必须为12,但是设计中的位宽为11,因此找到错误的AXI总线,将其地址深度改到不低于12位位宽的深度。

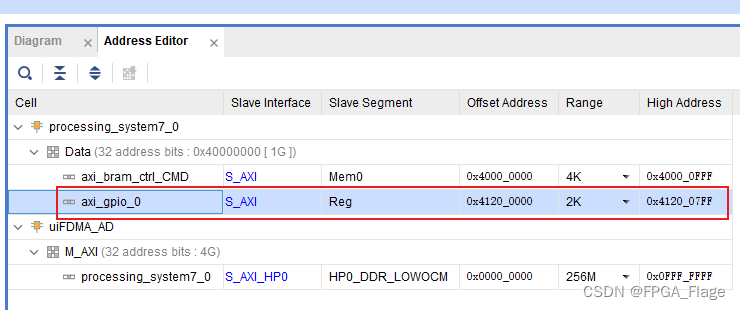

打开BD设计界面中的Address Editor选项卡,如图所示

从上图表红色框所知,axi_gpio_0 的深度为 2K(注意:这里的单位为Byte);因此axi_gpio_0总线位宽为11位就能表示该范围(2K = 211 = 2048);由此可以得出只要将范围设置为4K即可消除该错误。

解决方法

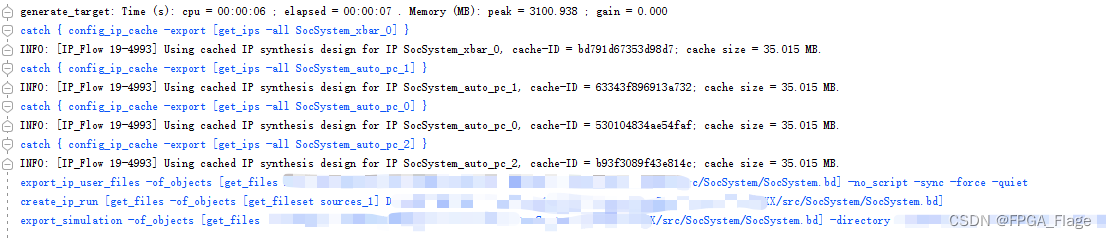

由上面原因分析可知:只要将上面的AXI 总线范围修改为4K即可消除此错误,如图所示:

保存

→

\rightarrow

→ 编译BD设计文件;编译结果

总结

由此可以总结:AXI总线地址是以4K对齐。

文章来源:https://blog.csdn.net/qq_35370933/article/details/135484648

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- LeetCode-搜索插入位置(35)

- 深入浅出 Zookeeper 中的 ZAB 协议

- 通过注解将接口代理到具体实现类调用

- 不玩游戏毫无经验,steam搬砖项目到底能不能做?

- C++ Qt开发:QItemDelegate自定义代理组件

- Vault实战(三)-Vault命令详解

- ATF(TF-A)安全通告TF-V11——恶意的SDEI SMC可能导致越界内存读取(CVE-2023-49100)

- 详解—C++[智能指针]

- Flow Launcher——让工作生活变得更简单

- ESU毅速丨复杂结构模具可尝试3D打印随形水路