裕泰微YT8521SH PHY芯片在uboot下的代码适配(一)

文章目录

YT8521SC/SH 是一款单口千兆以太网 PHY。

支持的工作模式

YT8521S 的 RGMII, SGMII/Fiber, RGMII 可以组合为多种模式:

UTP-RGMII

FIBER-RGMII

UTP/FIBER-RGMII

UTP-SGMII

UTP-FIBER_AUTO

UTP-FIBER_FORCE

SGMII_MAC-RGMII_PHY

SGMII_PHY-RGMII_MAC

上述各模式的选择是通过 power-on-strapping 实现的,具体详见 datasheet 或参考电路。

我们使用的是UTP_TO_RGMII模式

自协商模式下改变 PHY 支持的速度和双工能力

write_utp_mii_reg0x0[12]: 1’b1 #自协商打开,此为默认打开状态

write_utp_mii_reg0x4[8:5] #相应 bit 置 1 来打开对应的本地自协商时的 100/10BT 的速度双工能力

write_utp_mii_reg0x9[9] #相应 bit 置 1 来打开对应的本地自协商时的 1000BT 的速度双工能力

write_utp_mii_reg0x0[15]: 1’b1 #软复位 ,使上述配置生效

RGMII 配置

通过 POS 设置 RX_delay

根据 RGMII 标准,时钟的上升和下降沿采样,且时钟信号需要比数据信号 delay 1~2ns 来保证 setup/hold

时间,这个 delay 可以发送端加,也可以接收端加,甚至在早期的 RGMII 标准中通过时钟信号的板上走线延迟

来达到此目的。目前的应用中一般都是发送端加,对 UTP 来说就是 RX_CLK 的延迟,称为 rx_delay。YT8521 是通过芯片的 power-on-strapping 管脚来实现的开/关 rx_delay(具体见参考电路或 datasheet)。开启后,RGMII在 125MHz(1000BT/1000BX)下的 rx_delay 约为 1.x 纳秒,25MHz/2.5MHz(100BT/10BT)下的 rx_delay 约为7.x 纳秒。

通过寄存器加长 RX_delay

实际使用中若需要加长 rx_delay,以改善 setup 时间,也可以通过配置 common 扩展寄存器来配置:

Write_ext_reg0xa003[13:10]: 默认为 4’b0,每加 1,则 rx_delay 延长约 150ps。(无论 RGMII 工作在

125MHz/25MHz/2.5MHz)

TX_delay 的设置

UTP 的 RGMII tx_delay 默认很少,也就是 MAC 发给 UTP 的时钟和数据信号要保证足够的 setup/hold 时

间。假如 MAC 发送给 UTP 的 RGMII 的时钟和数据信号不满足要求,通常为 setup 时间不够,UTP 也可以通过

配置 common 扩展寄存器来配置:

Write_ext_reg0xa003[3:0]: RGMII 125MHz 时的 tx_delay,默认为 4’b1(150ps),每加 1,则 tx_delay 延长约

150ps。

Write_ext_reg0xa003[7:4]: RGMII 25/2.5MHz 时的 tx_delay,默认为 4’b1111(2.25ns),已经是最大延迟。

驱动能力的设置

UTP 的 RGMII 驱动能力,反映在上升/下降时间。驱动能力大,意味着能带更大的负载,但也可能引入

EMI 的问题。UTP 默认的驱动能力是权衡两者之后的设置,并非最强档位。若需要加强或减弱驱动能力,可以

通过配置 common 扩展寄存器来配置:

Write_ext_reg0xa010[5:4]: 默认为 2’b01。2’b11 为最强档,2’b00 为最弱档。

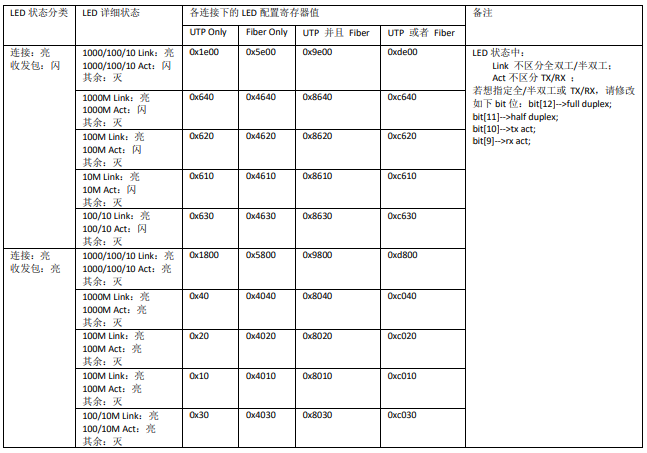

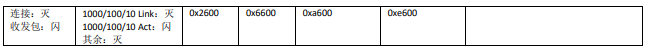

LED 灯配置

YT8521SH 支持三个 LED 灯:LED0,LED1,LED2。它们对应的配置寄存器为 utp_ext_reg0xa00c,

utp_ext_reg0xa00d, utp_ext_reg0xa00e。用来配置 LED 在不同状态下是闪、灭、亮。其中闪的频率由

utp_ext_reg0xa00f 定义闪的频率分为 Blink mode2 和 Blink mode1 两种。

注意:除了 collision 状态和 force LED 状态可选 Blink mode2 或 Blink mode1(见 utp_ext_reg0xa00b)外,

其它的状态若要闪只能是 Blink mode2。

为方便使用,下表列出了一些常用 LED 行为对应的寄存器配置:

另外,闪烁的占空比和频率配置分别放在 utp_ext_reg0xa00f 中。除了连接和收发包外的一些 LED 行为配置放

在 utp_ext_reg0xa00b 中。具体请参考 datasheet。

硬件电路设计相关问题

快速上下电的要求

YT8521SH 快速上下电的要求和条件,根据实验和仿真,结论如下:

- 当 3.3V 电压掉到 3.3~2.5V 或 0~1.4V,再上升回 3.3V,芯片会正常工作;

- 当 3.3V 电压掉到 1.4~2.5V 的范围,再上升回 3.3V,则分为两种情况:

如果期间芯片的复位管脚为低(一般小于 1V),再升回 3.3V 后,此信号拉到高,则芯片经过复位,会正

常工作。

如果期间芯片的复位管脚为高(一般高于 1.5V),再升回 3.3V 后,则芯片未经过复位,可能工作不正常,

但在下一次硬复位后即可正常工作

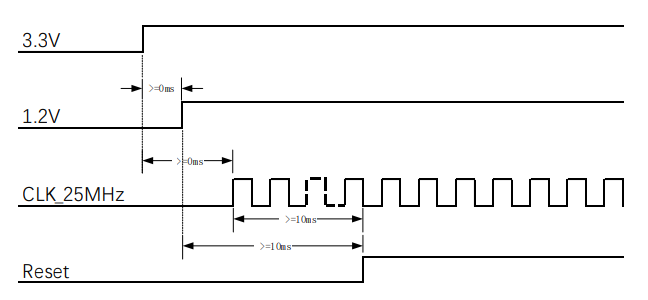

上电复位时序要求

YT8521SH 芯片支持多种模式。

一、对于不包含 RGMII 相关的模式,它的上电时序要求如下:

说明:

- 若 1.2V 或 CLK_25MHz 由芯片内部电源/晶体振荡电路产生,则它们与 3.3V 的时序由芯片内部控制,满

足芯片内部时序要求。其中可能由于 3.3V 上升慢,而 1.2V 上升快,导致 1.2V 比 3.3V 先稳定,这是正常现

象,无问题。或者 CLK_25MHz 在 3.3 上电未稳定时即有输出也是正常现象。 - 若 1.2V 或 CLK_25MHz 由外灌,则需遵守上述时序。其中 1.2V 和 CLK_25MHz 并不要求先后,但要求

1.2V 和 CLK_25MHz 都稳定并保持至少 10ms 后再释放 Reset 信号。

上述说明详细可见YT8521SH应用说明。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 互联网加竞赛 Yolov安全帽佩戴检测 危险区域进入检测 - 深度学习 opencv

- 如何在 Linux 操作系统中管理计划任务?

- 【实战教程】从零开始学防火墙服务部署,让你的网络安全防护无懈可击!

- AI写作哪个好用?这5个赶紧收藏吧

- 内网渗透测试基础——权限提升分析及防御

- 社区公益培训系统功能说明

- VBA技术资料MF107:表对象中数据的删除查找及排序

- 【LeetCode】20. 有效的括号(简单)——代码随想录算法训练营Day11

- C++ //练习 2.5 指出下述字面值的数据类型并说明每一组内几种字面值的区别:

- Redis学习指南(26)-Redis的RDB备份查看工具Rdbtools