【计算机组成-算术逻辑单元】

发布时间:2024年01月15日

课程链接:北京大学陆俊林老师的计算机组成原理课

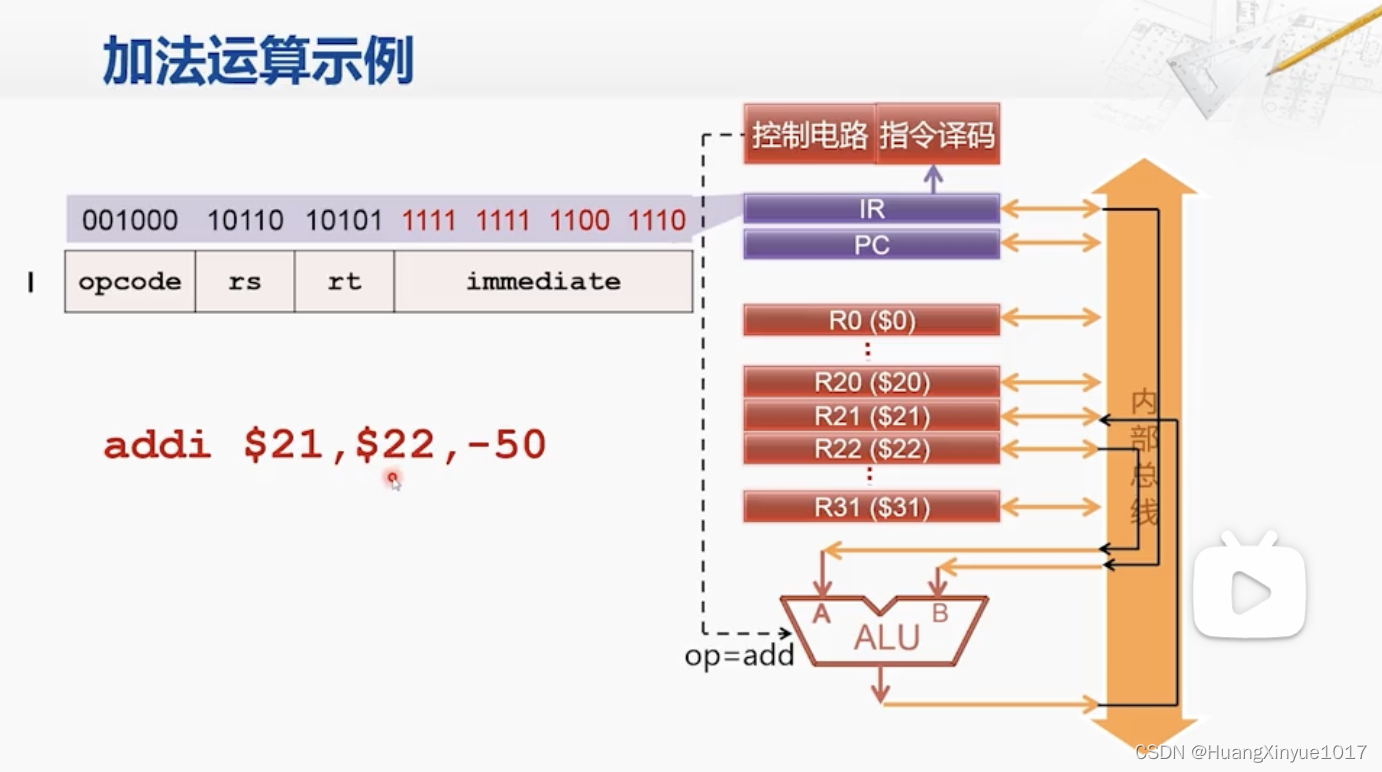

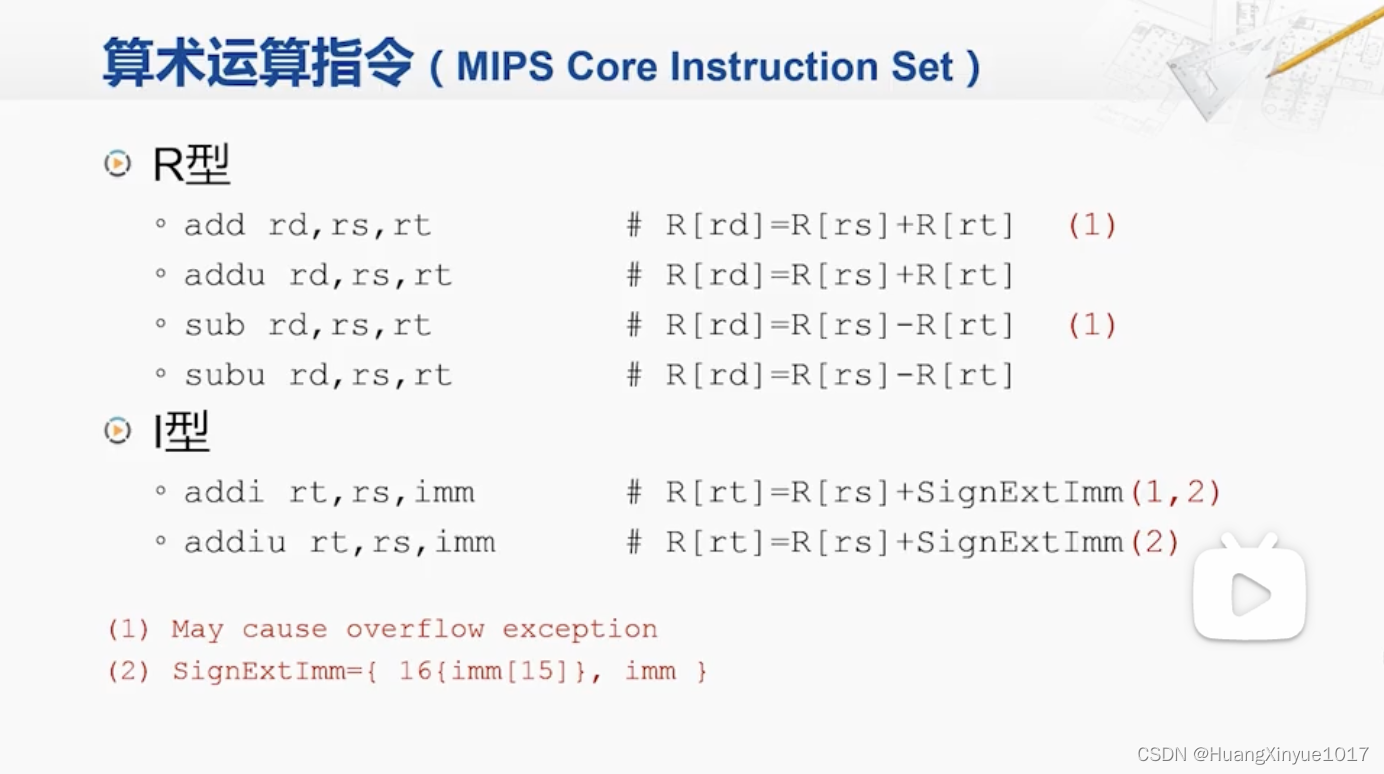

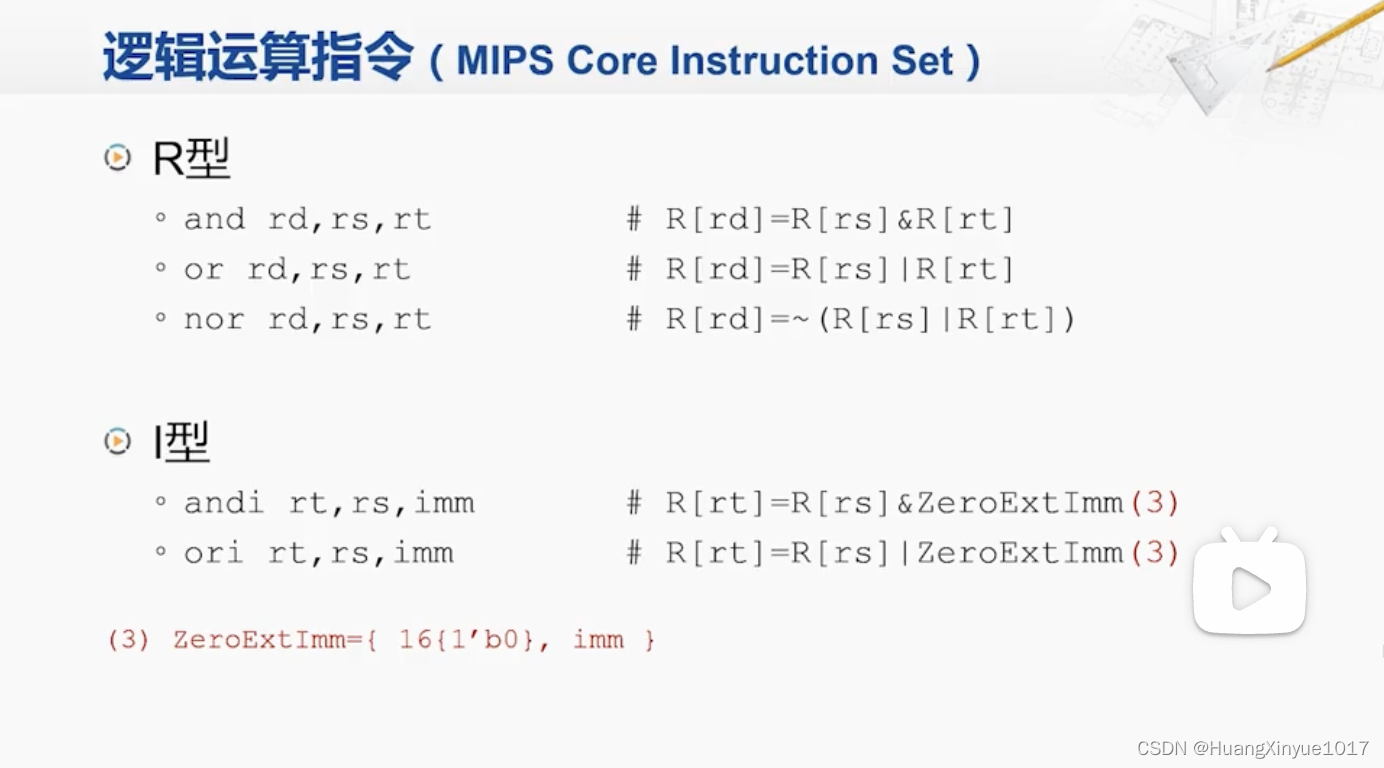

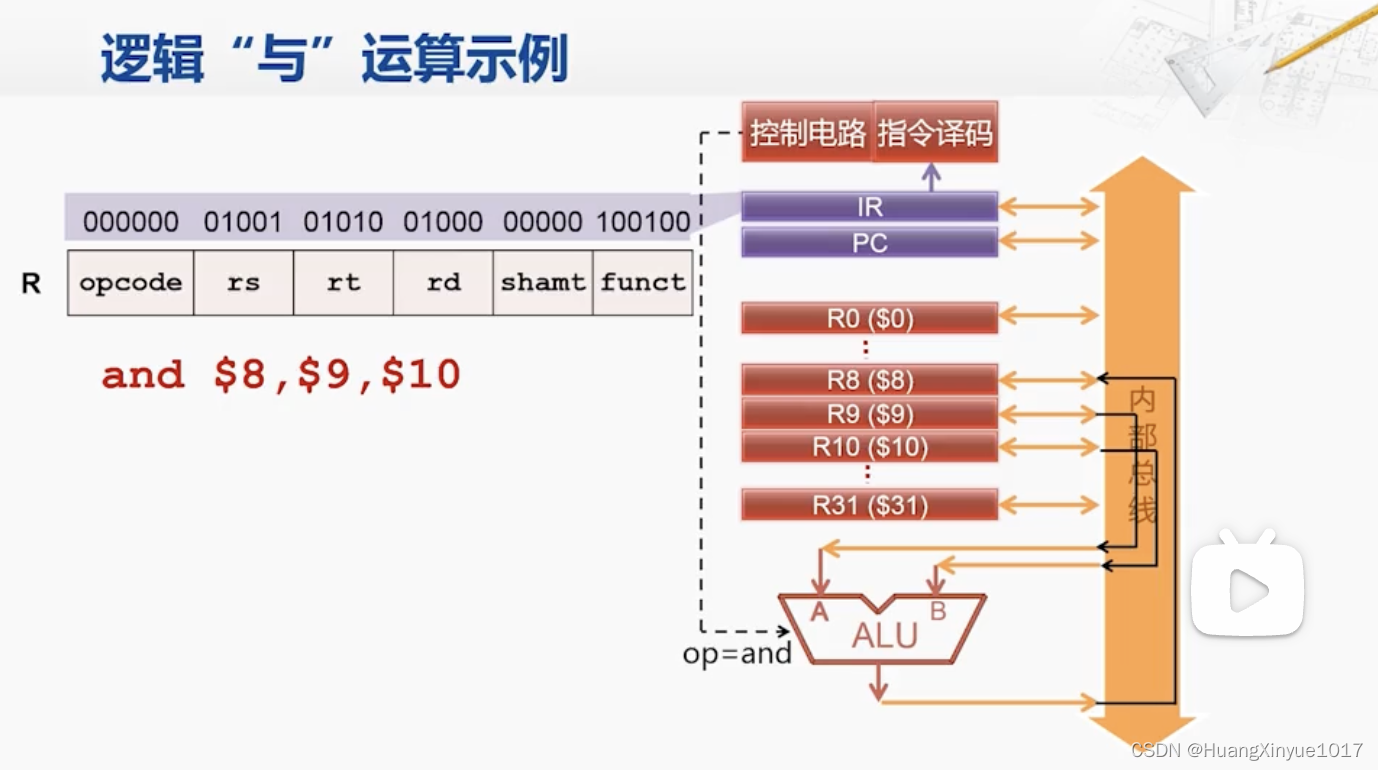

1. 算术运算和逻辑运算

算数运算

逻辑运算

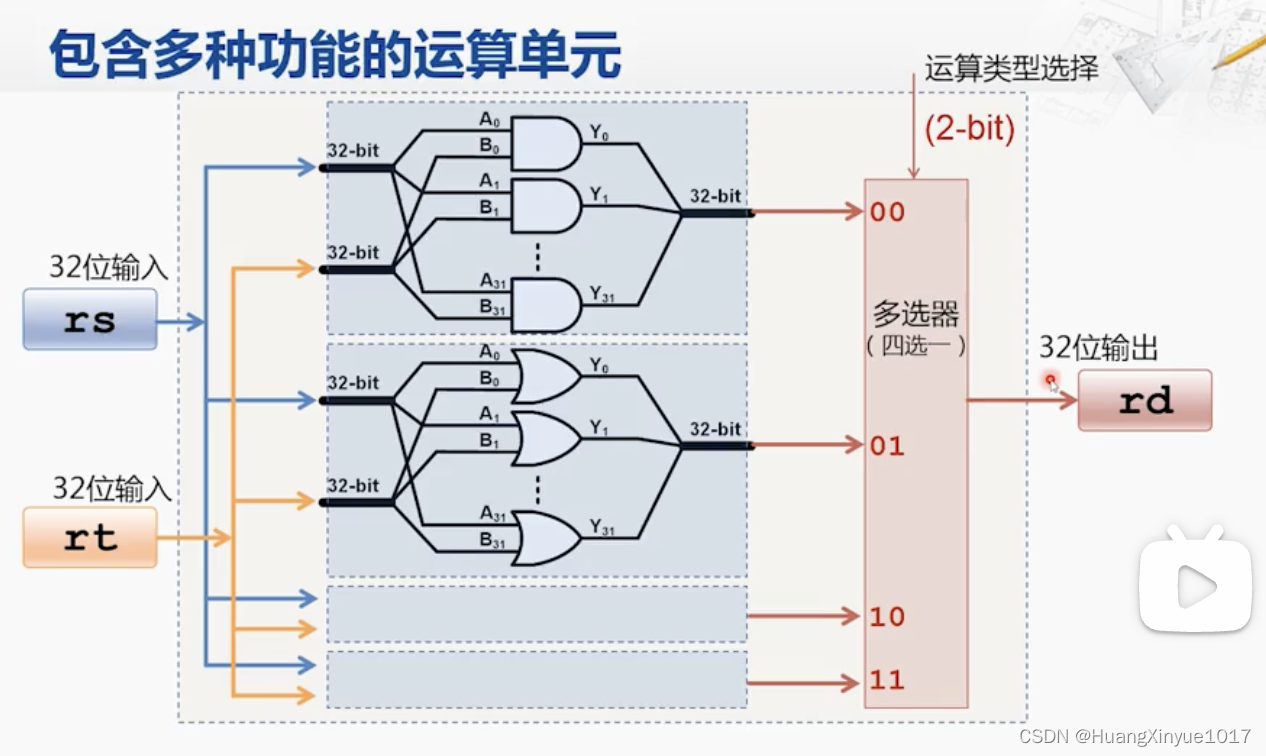

算数逻辑运算的需求

- 算数运算:两个32-bit数的加减法,结果为一个32-bit数;检查加减法的结果是否溢出

- 逻辑运算:两个32-bit数的与或非,结果为一个32-bit数

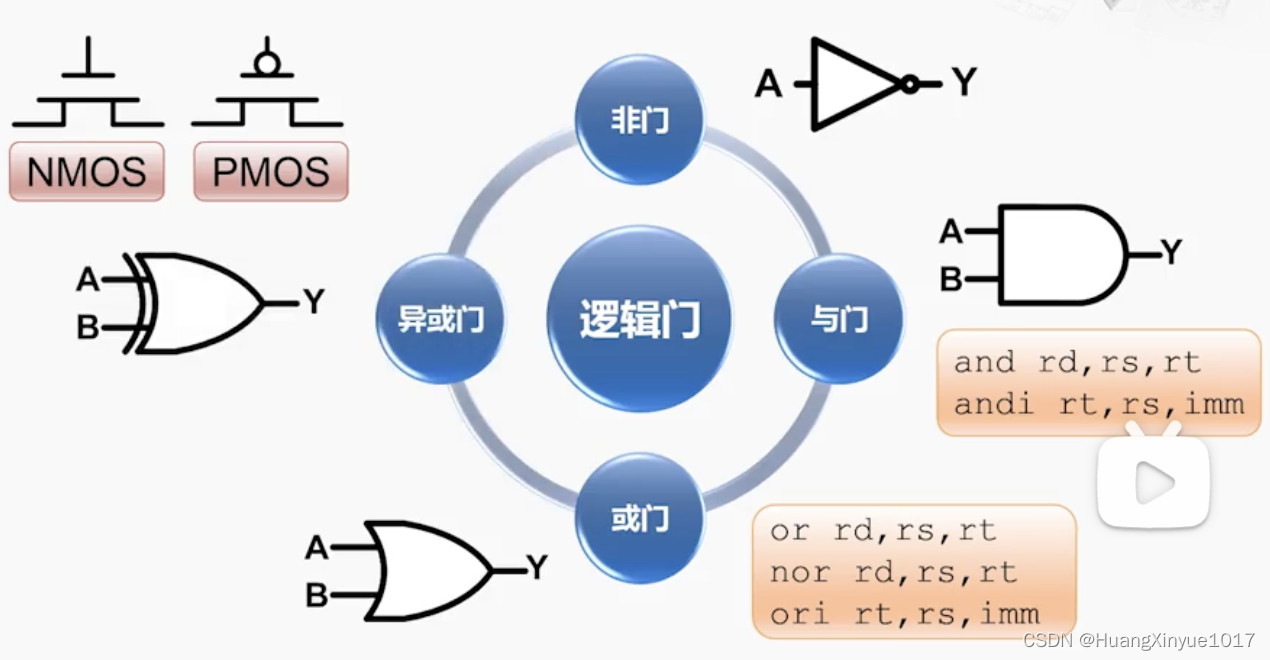

2. 门电路的基本原理

晶体管

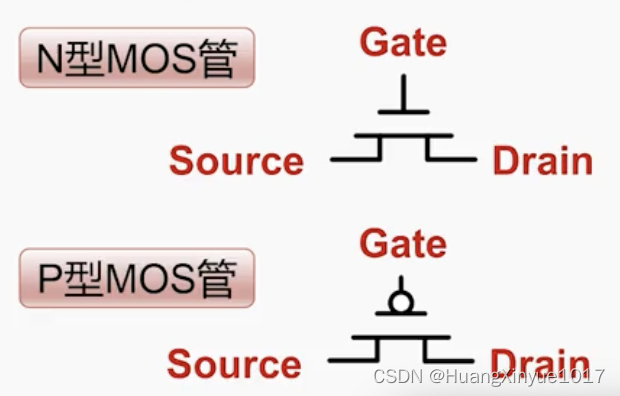

- 现代集成电路中通常使用MOS(Metal-Oxide-Semiconductor,金属-氧化物-半导体)晶体管:分为N型MOS管(高电频为通路)和P型MOS管(低电频为通路)

- CMOS(Complementary MOS)集成电路:由PMOS和NMOS共同构成的互补型MOS集成电路

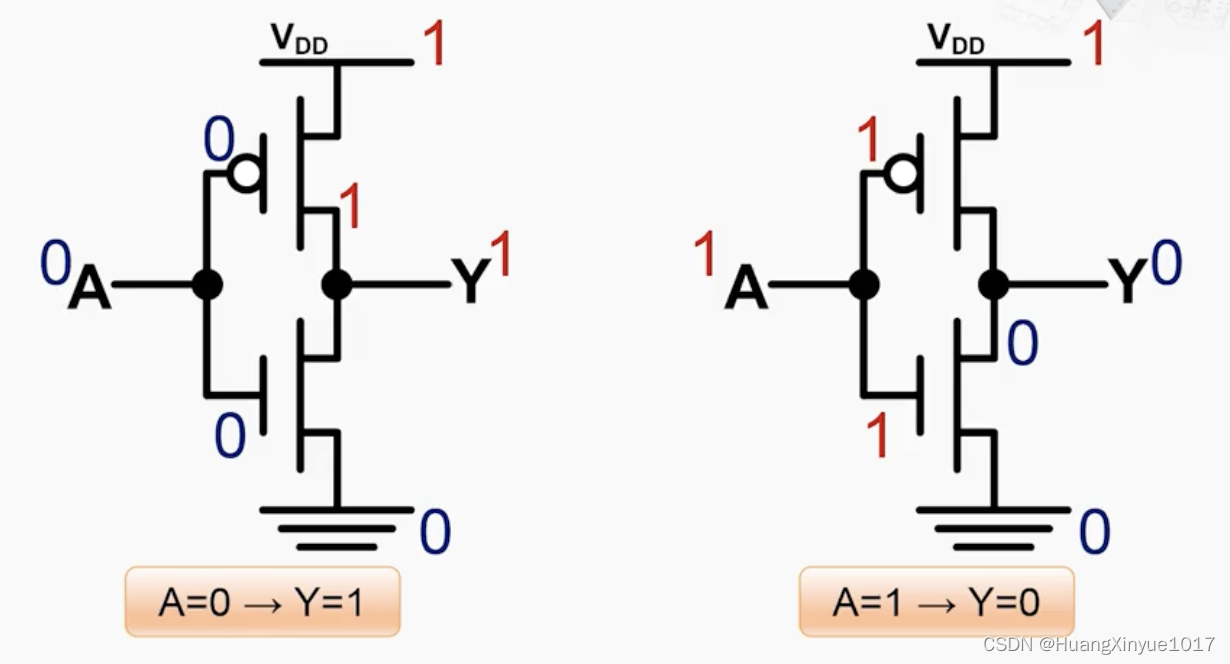

非门(NOT Gate)

非门的工作过程

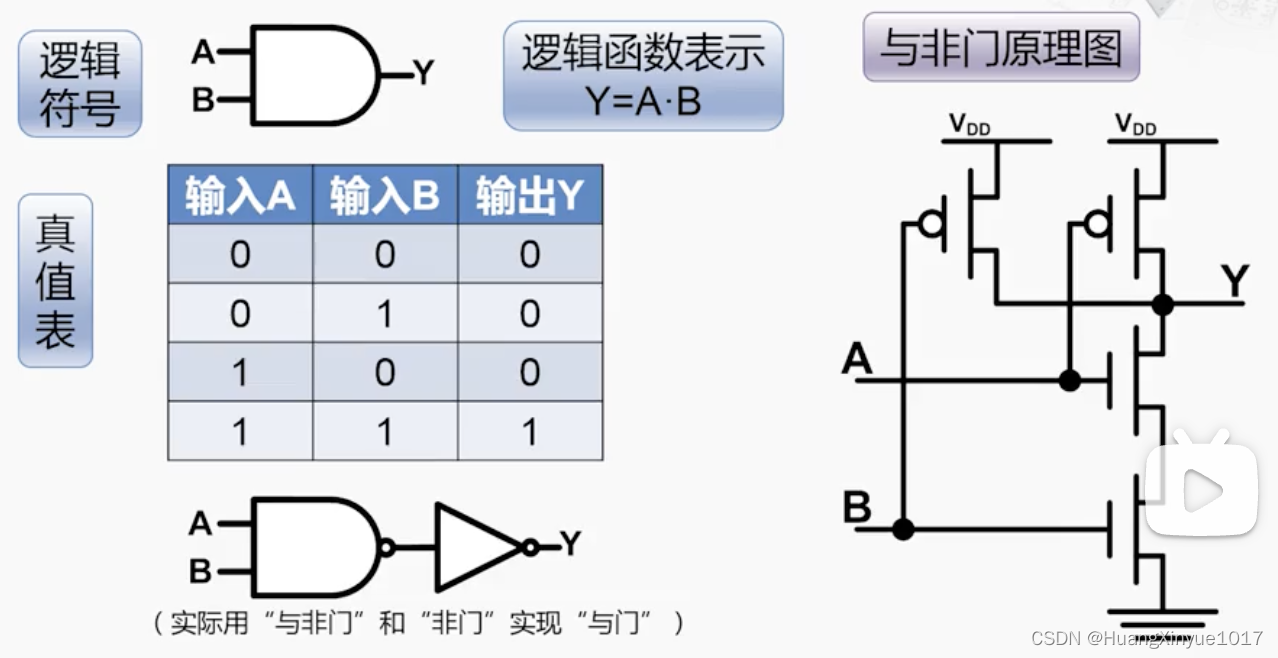

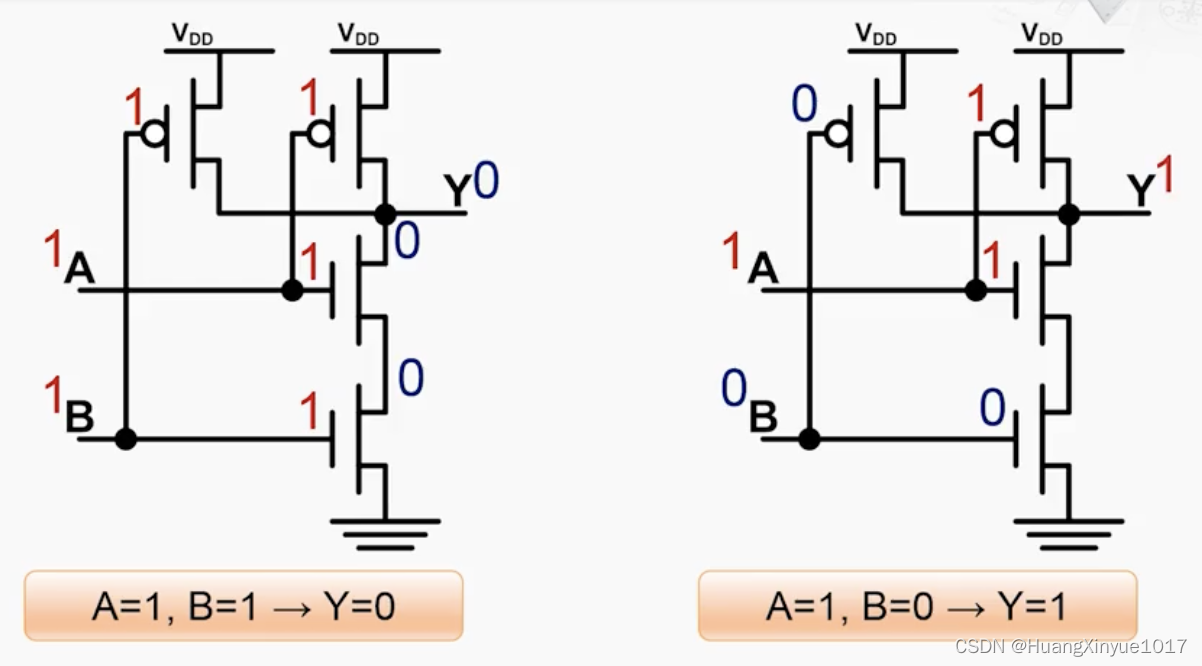

与门(AND Gate)

与非门的工作过程

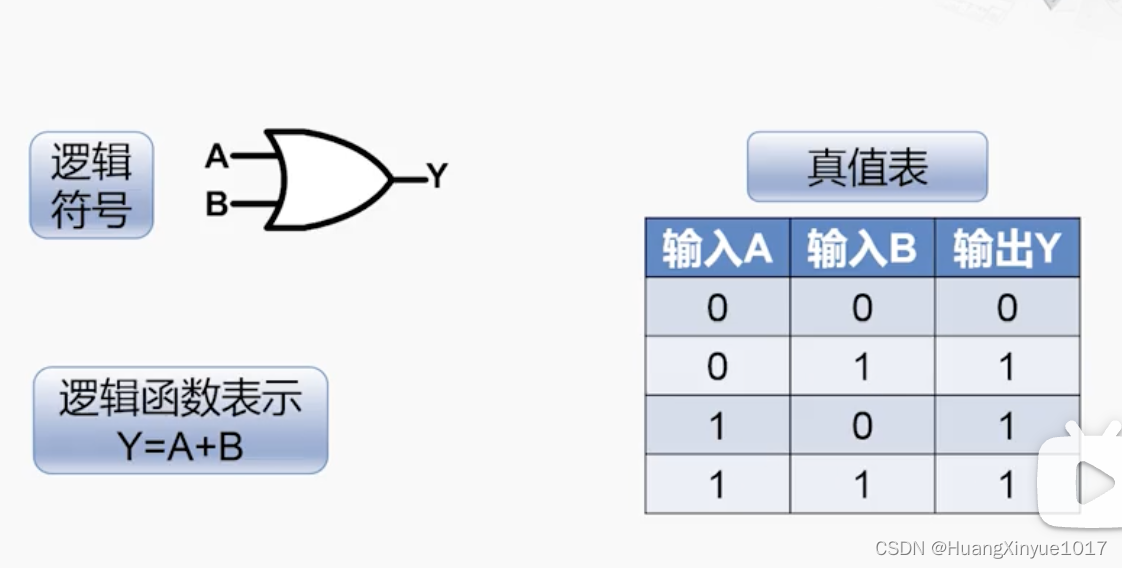

或门(OR Gate)

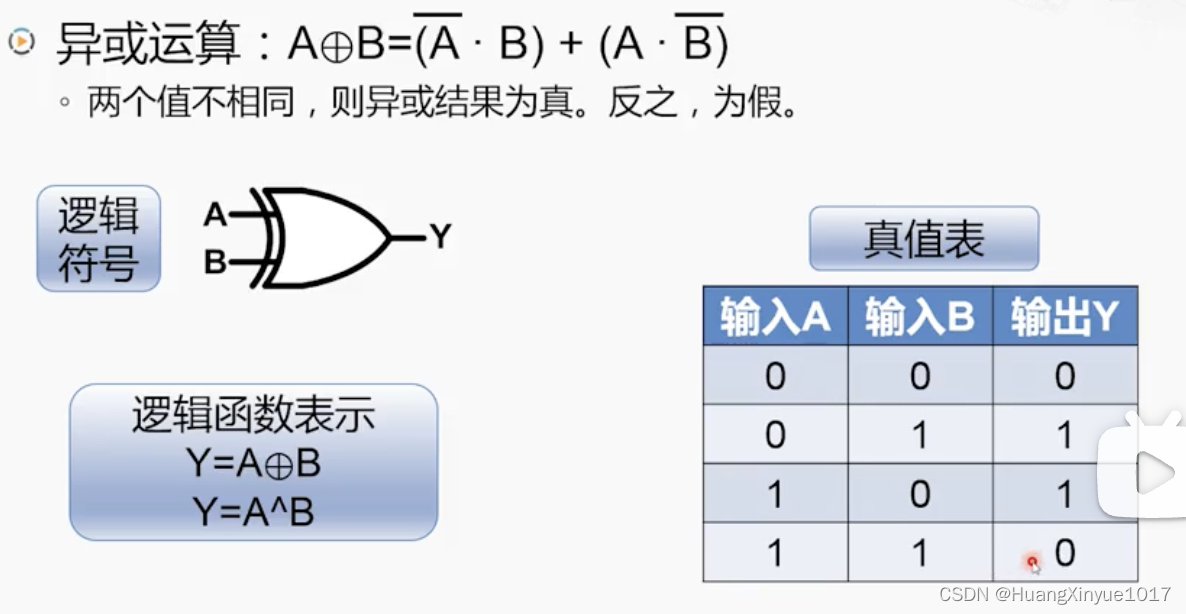

异或门(XOR Gate)

晶体管、逻辑门

3. 寄存器的基本原理

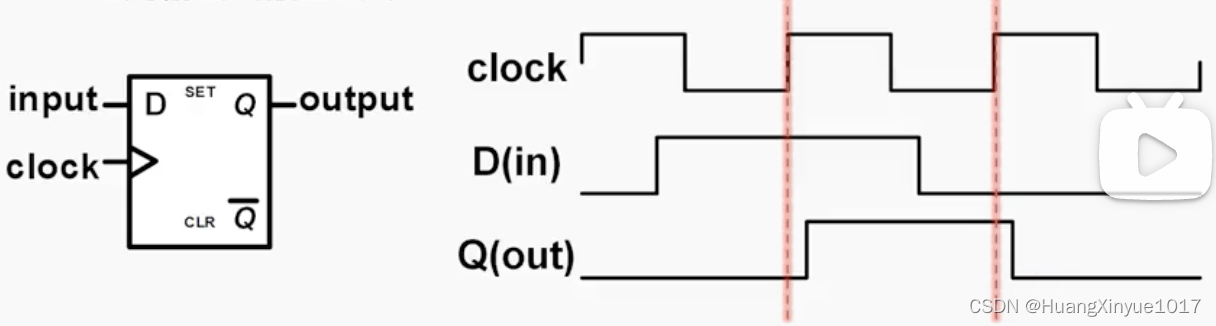

D触发器(D Flip-Flop,DFF)

- 具有存储信息能力的基本单元

- 由若干个逻辑门构成,有多种实现方式

- 主要有一个数据输入、一个数据输出、一个时钟输入

- 在时钟clock的上升沿(0->1),采样输入D的值,传送到输出Q,其余时间输出Q的值不变

D触发器的工作原理

- 照相机 + 显示器 -> D触发器

- 每10秒钟按一次快门 -> 时钟的频率为0.1Hz(f = 1 / T)

- 按快门后1秒钟,显示器上显示照片 -> CLK-to-Q时间为1秒

- 按快门前后,待拍摄的画面不能有变化 -> Setup/Hold时间

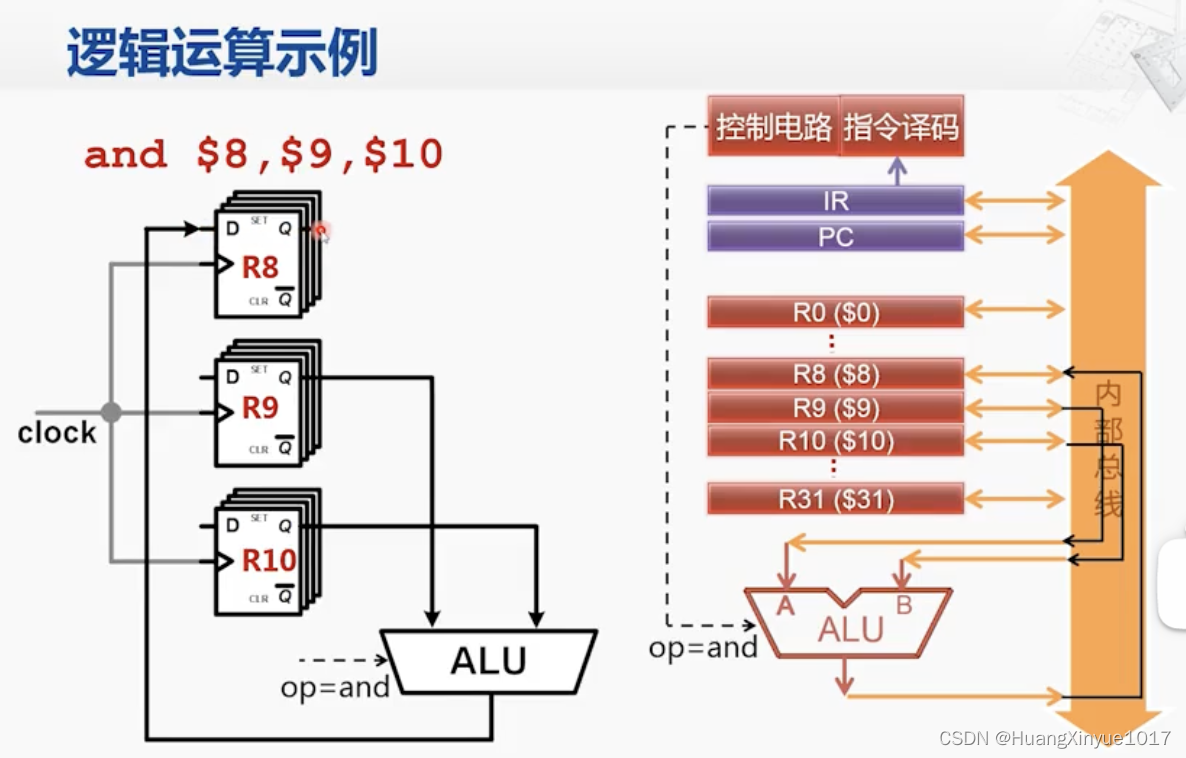

4. 逻辑运算的实现

5. 加法和减法的实现

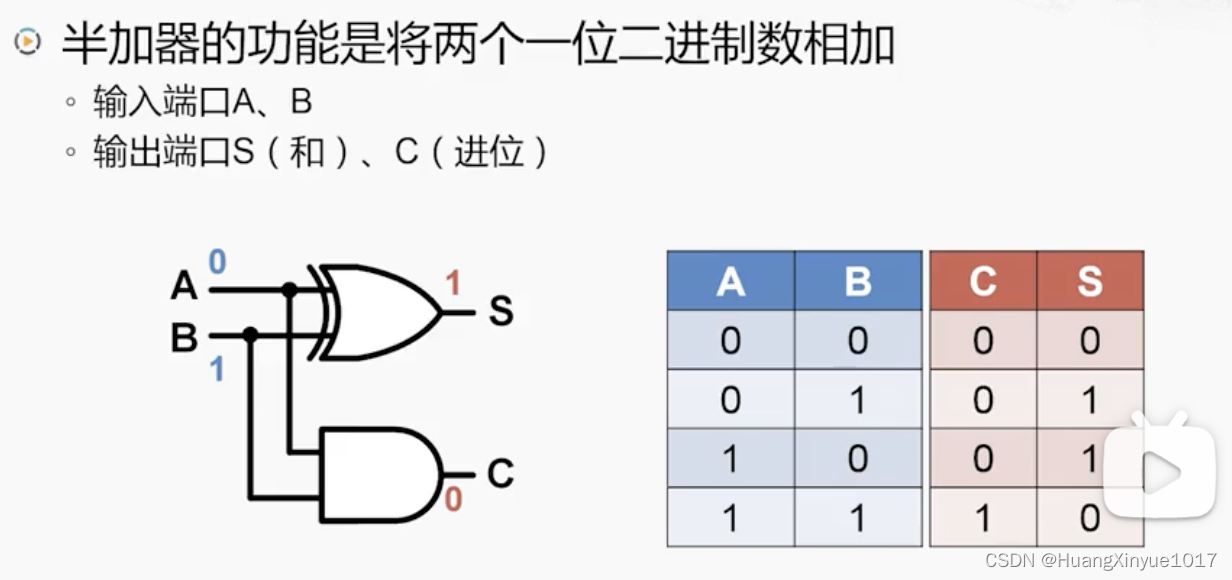

半加器(Half Adder)

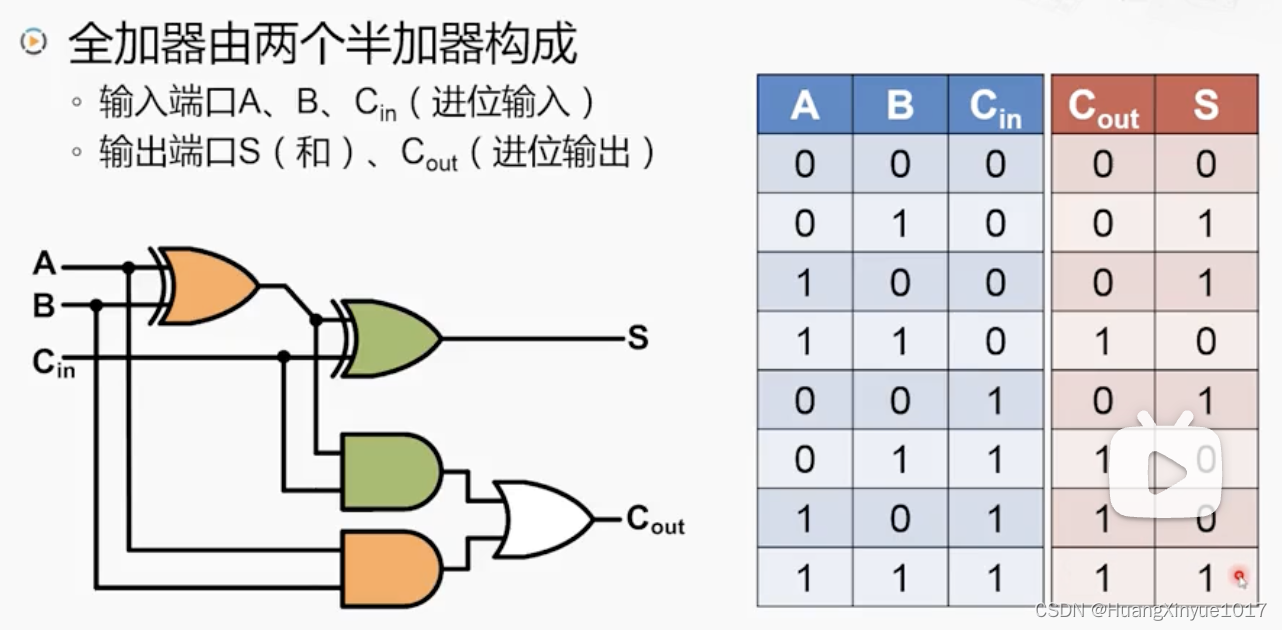

全加器(Full Adder)

4-bit加法器

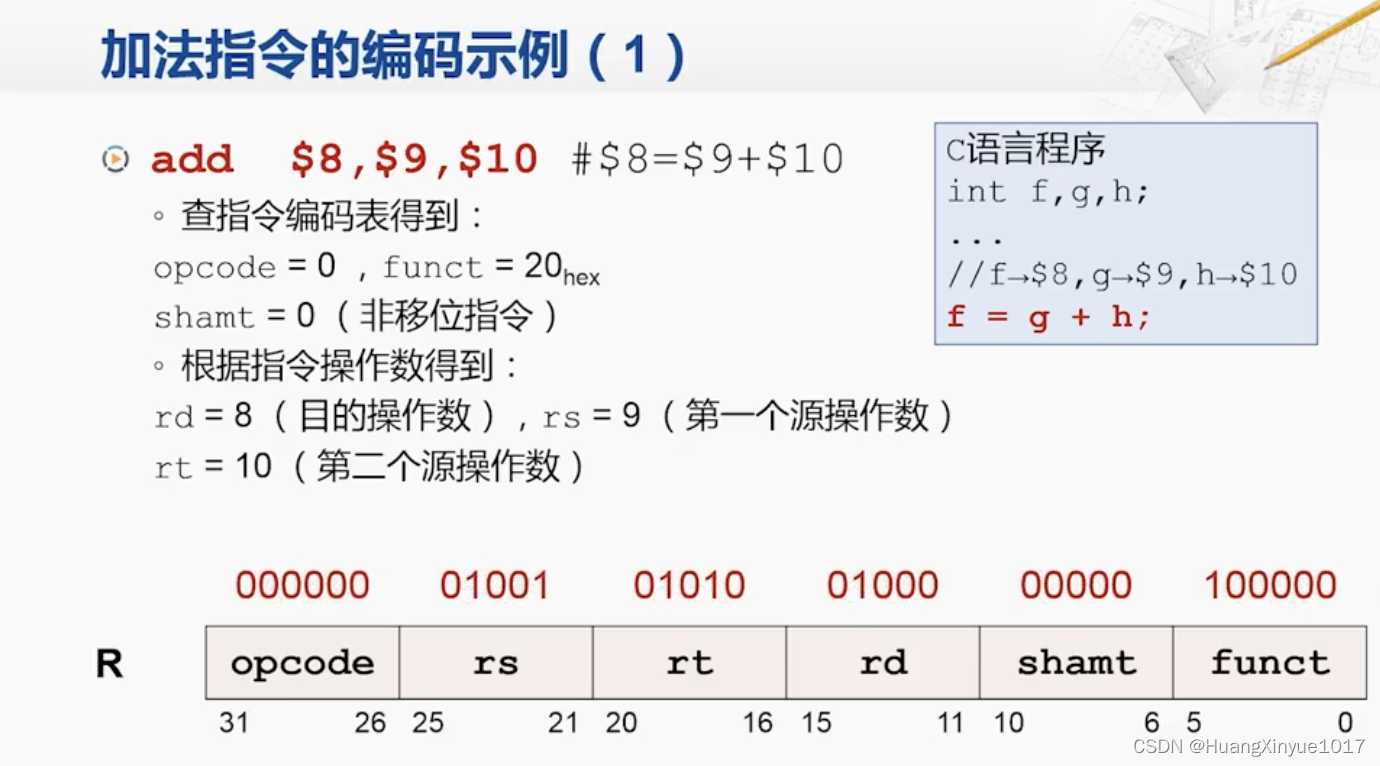

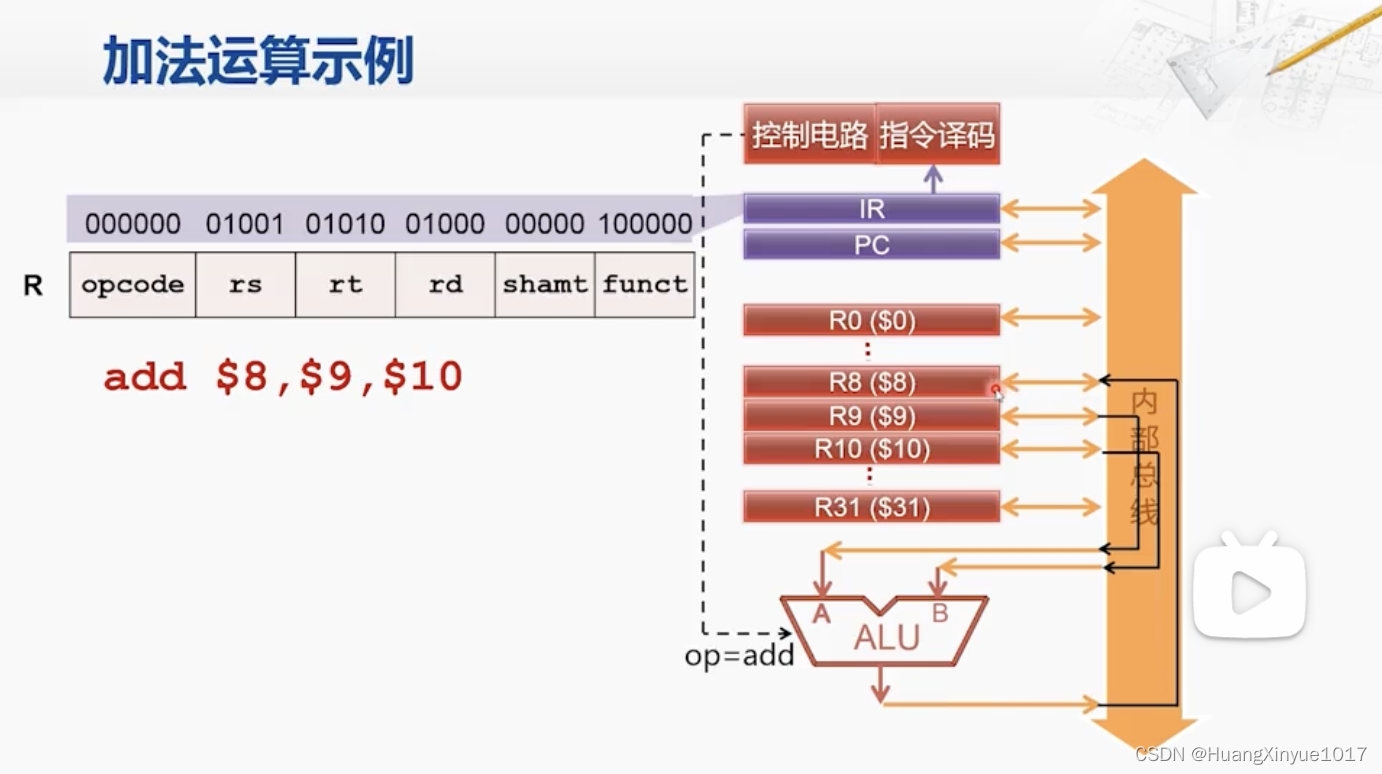

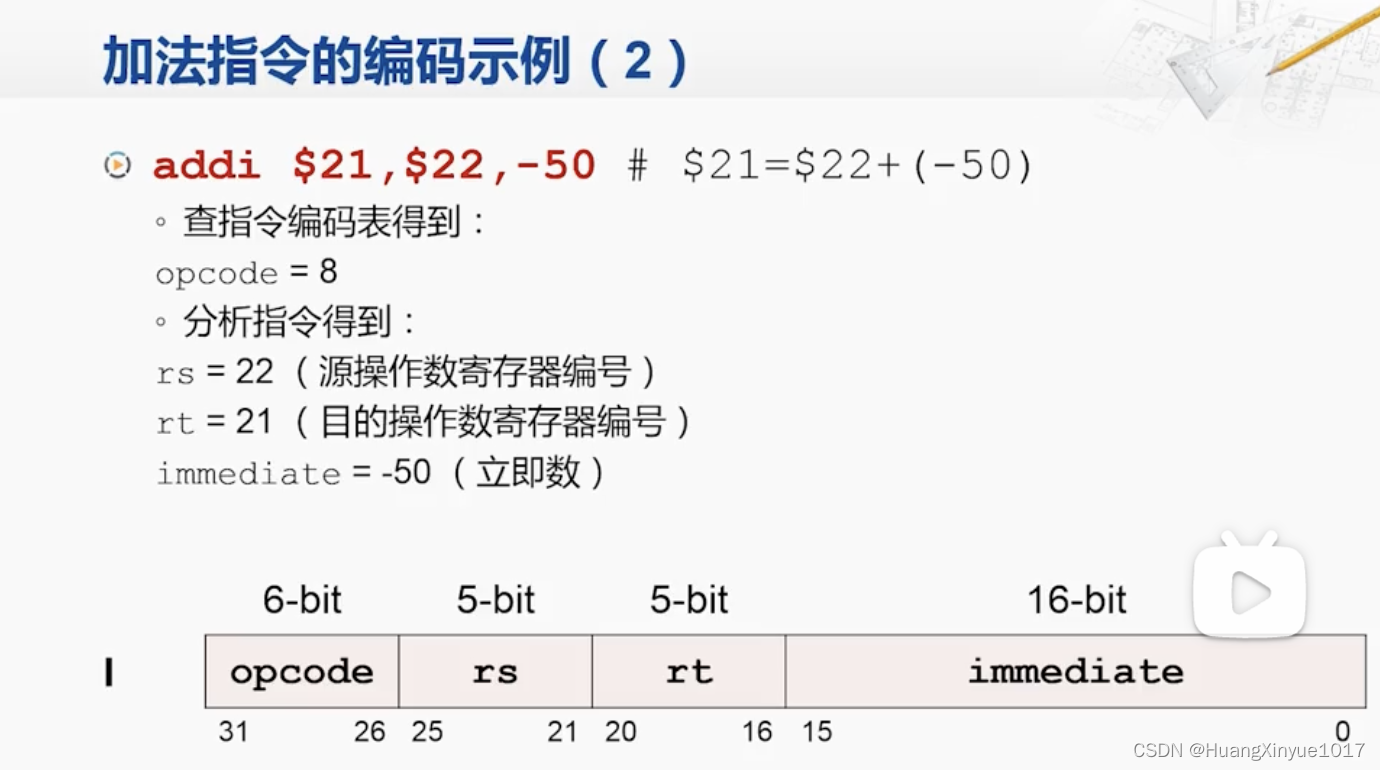

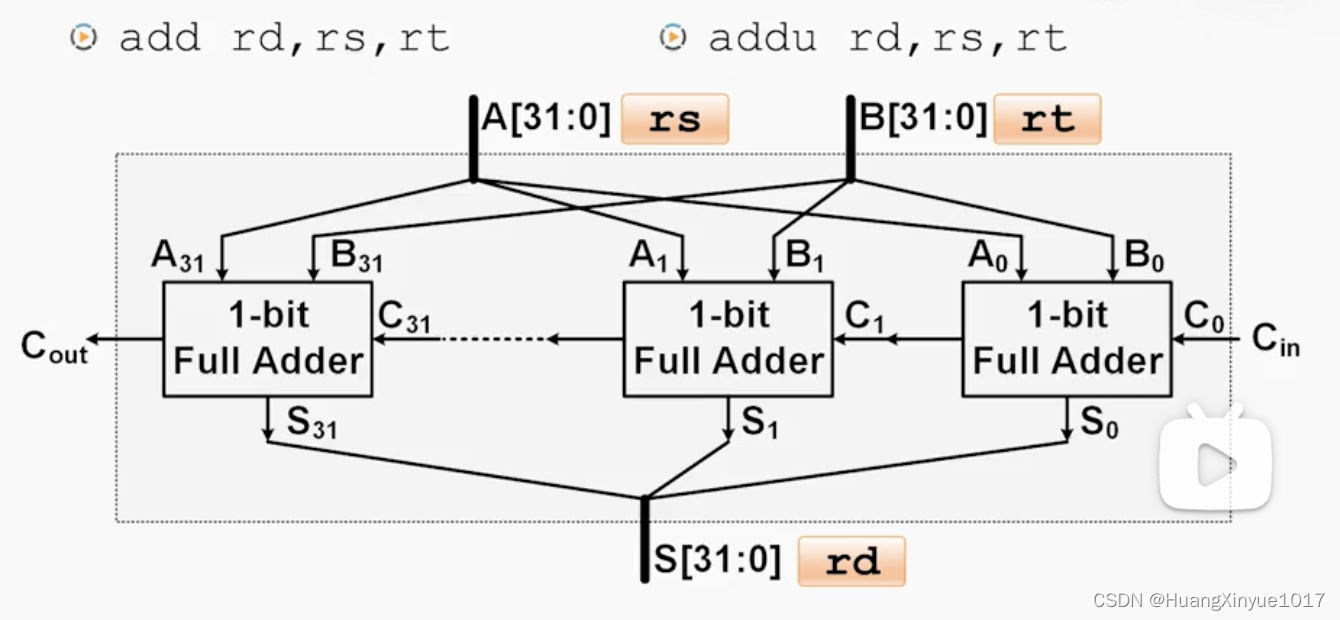

加法运算的实现示例

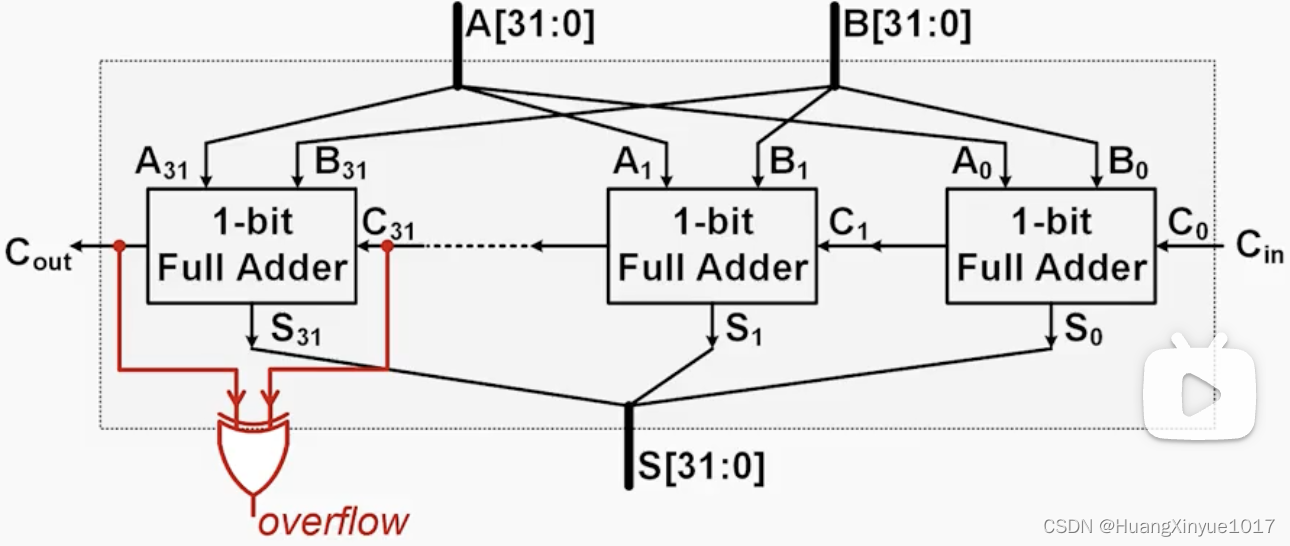

检查加法运算结果是否溢出

- 溢出(overflow):运算结果超出了正常的表示范围

- 溢出仅针对有符号数运算:溢出的表现:两个正数相加,结果为负数;两个负数相加,结果为正数

- 溢出的检查方法:最高位的进位输入不等于最高位的进位输出

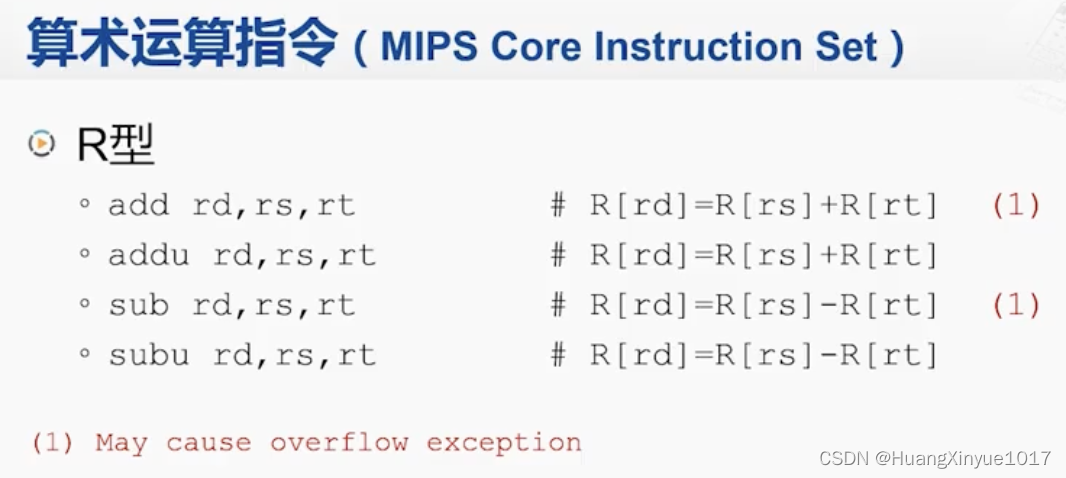

MIPS对溢出的处理方式

- 提供两类不同的指令分别处理

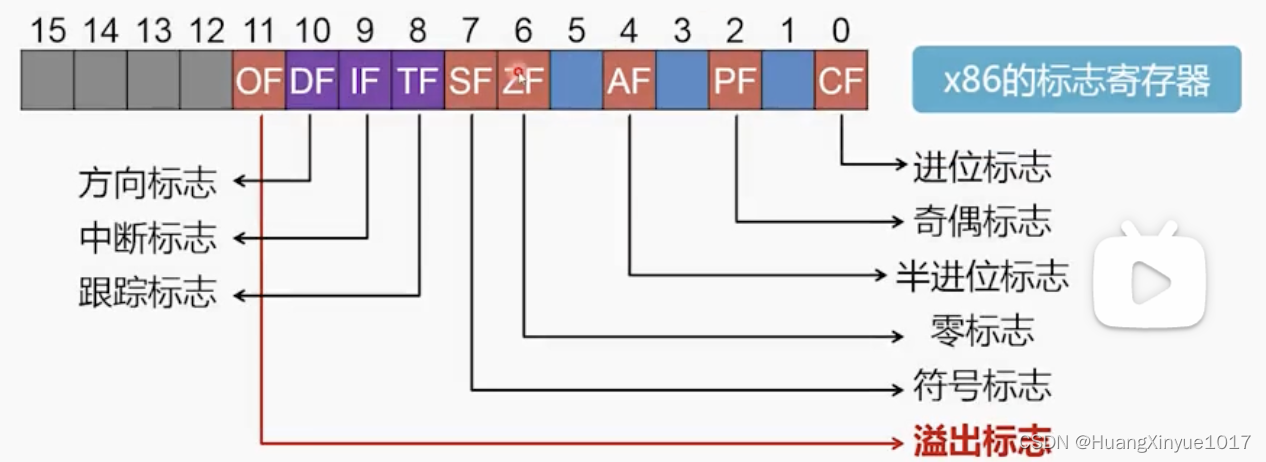

x86对溢出的处理方式

- 溢出标志OF(Overflow Flag):如果把操作数看作有符号数,运算结果是否发生溢出;若发生溢出,则自动设置OF=1,否则OF=0

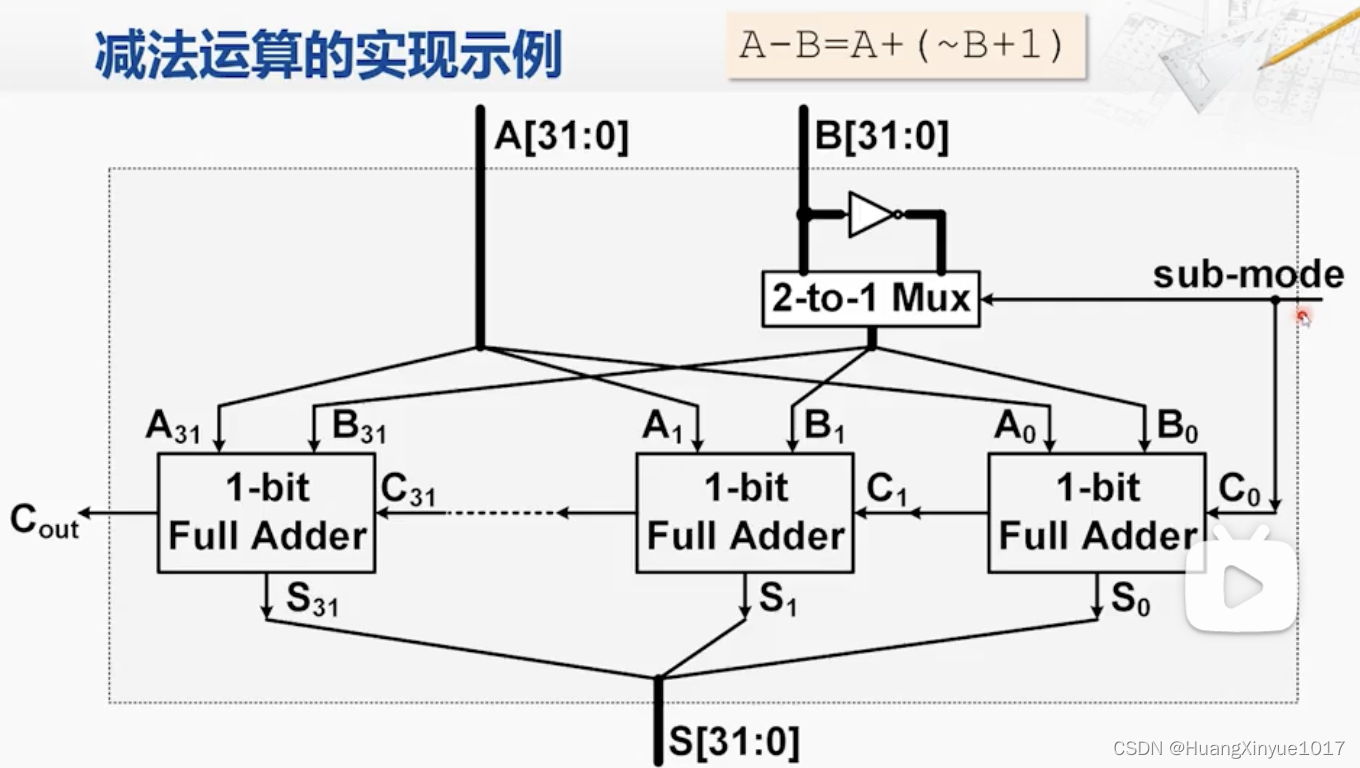

减法运算

- 减法运算均可转换为加法运算:A - B = A + (-B)

- 补码表示的二进制数的相反数:转换规则:按位取反,末位加一

- 在加法器的基础上实现减法器:A + (-B) = A + (~B+1)

6. 加法器的优化

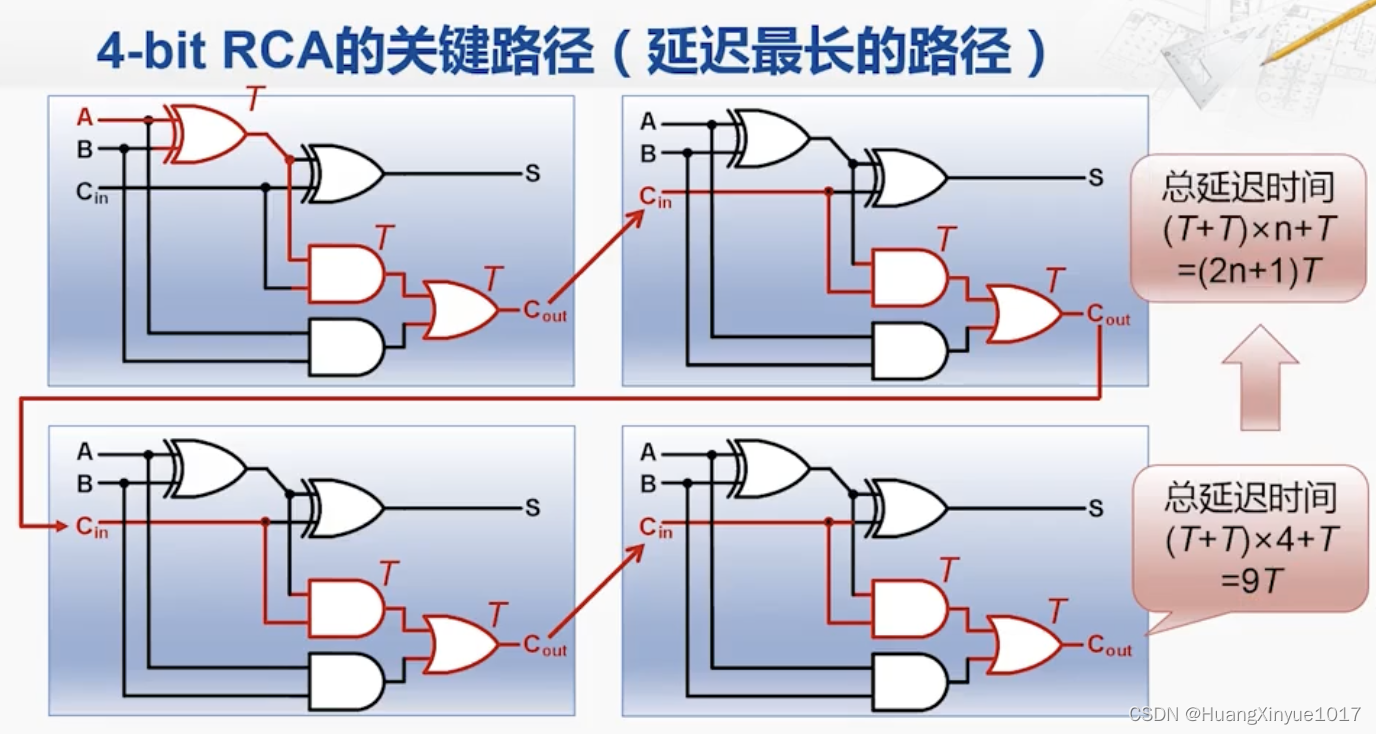

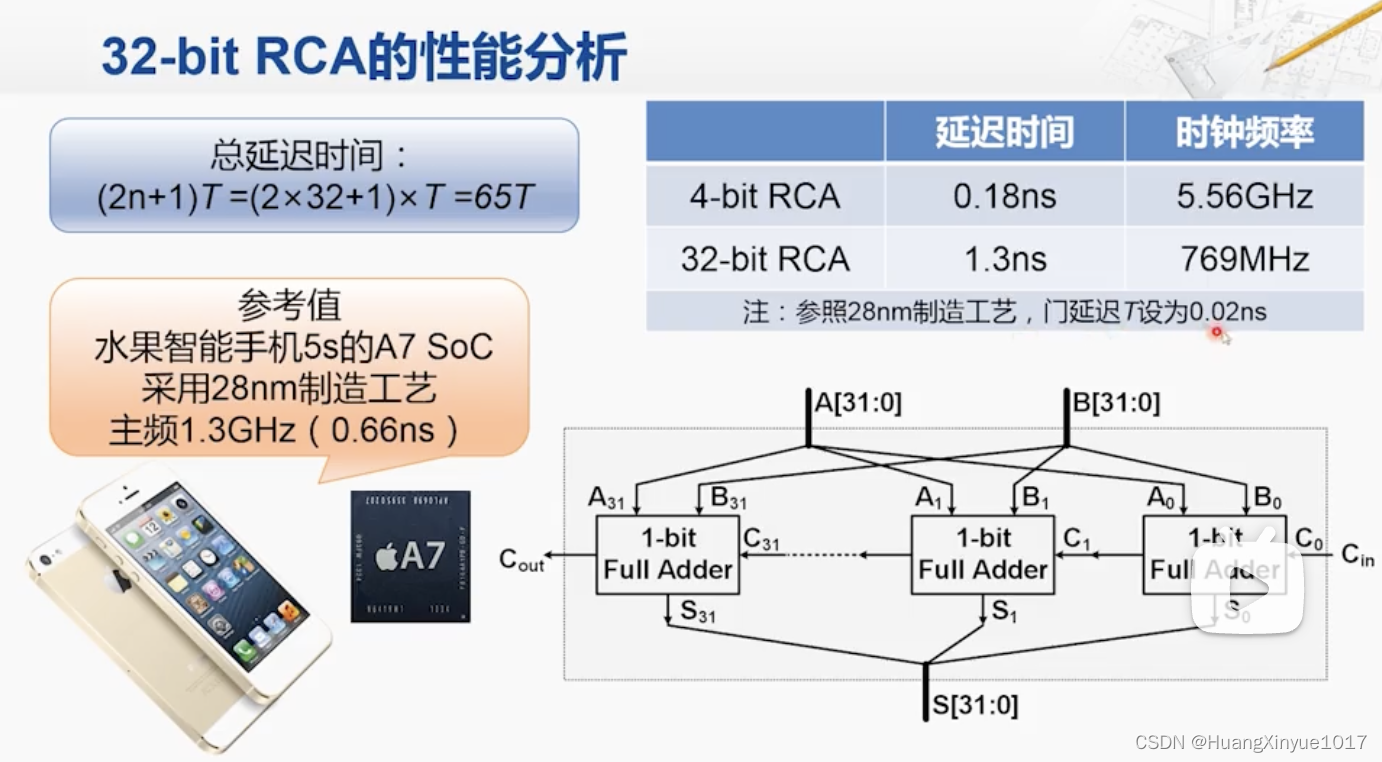

行波进位加法器(Ripple-Carry Adder,RCA)

- 上述加法器被称为RCA

- 结构特点:低位全加器的 C o u t Cout Cout 连接到高一位全加器 C i n Cin Cin

- 优点:电路布局简单,设计方便

- 缺点:高位的运算必须等待低位的运算完成,延迟时间长

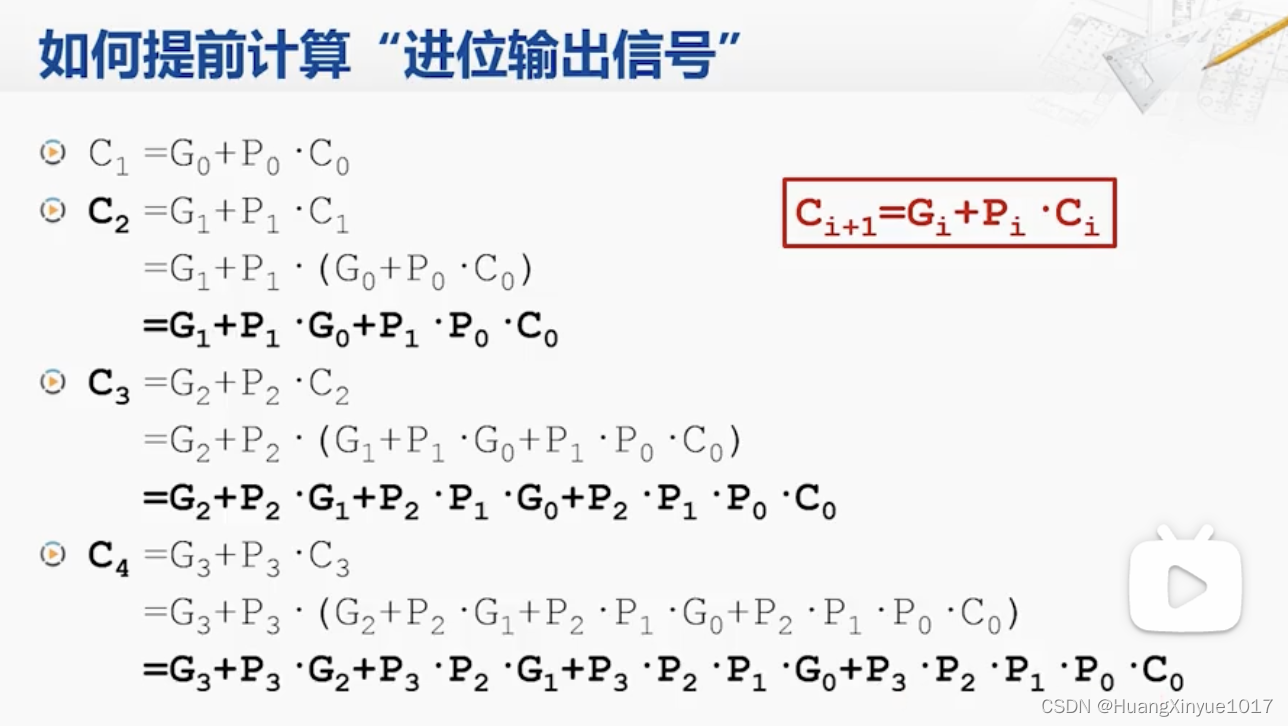

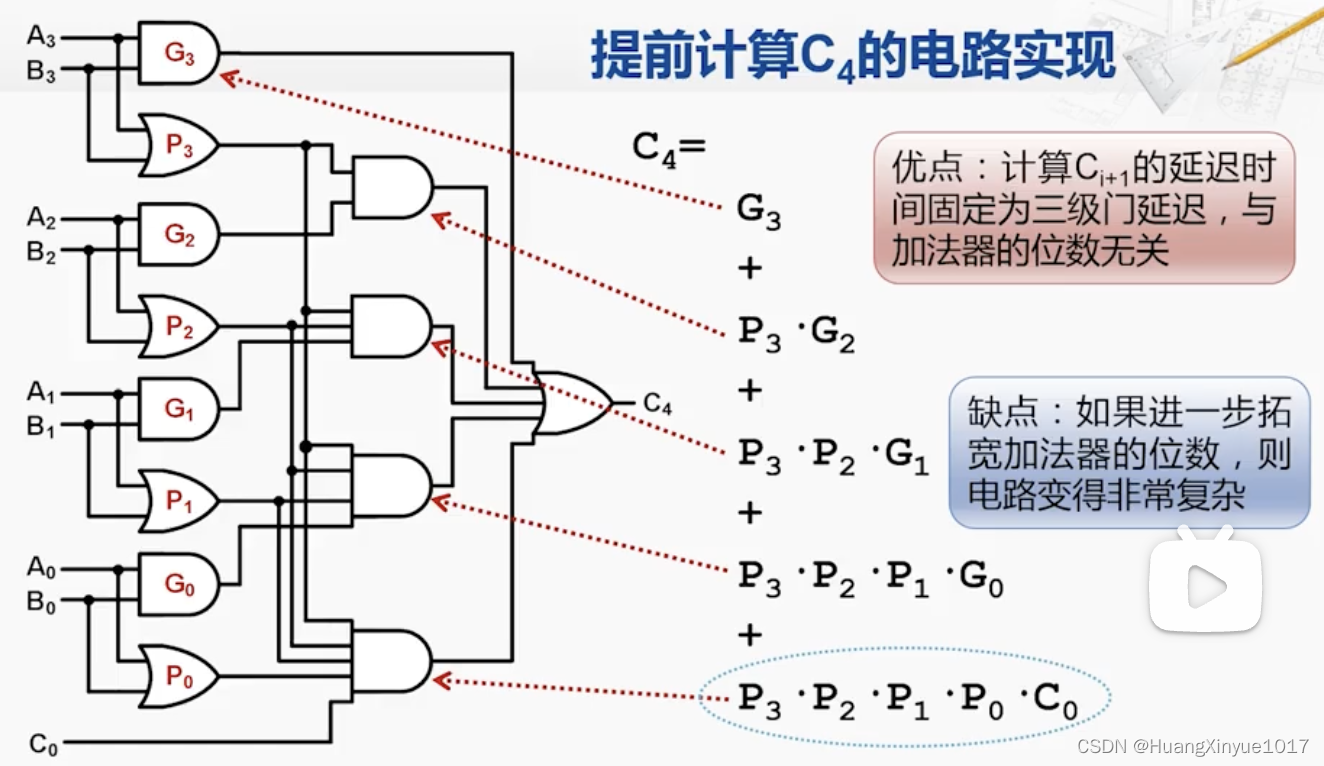

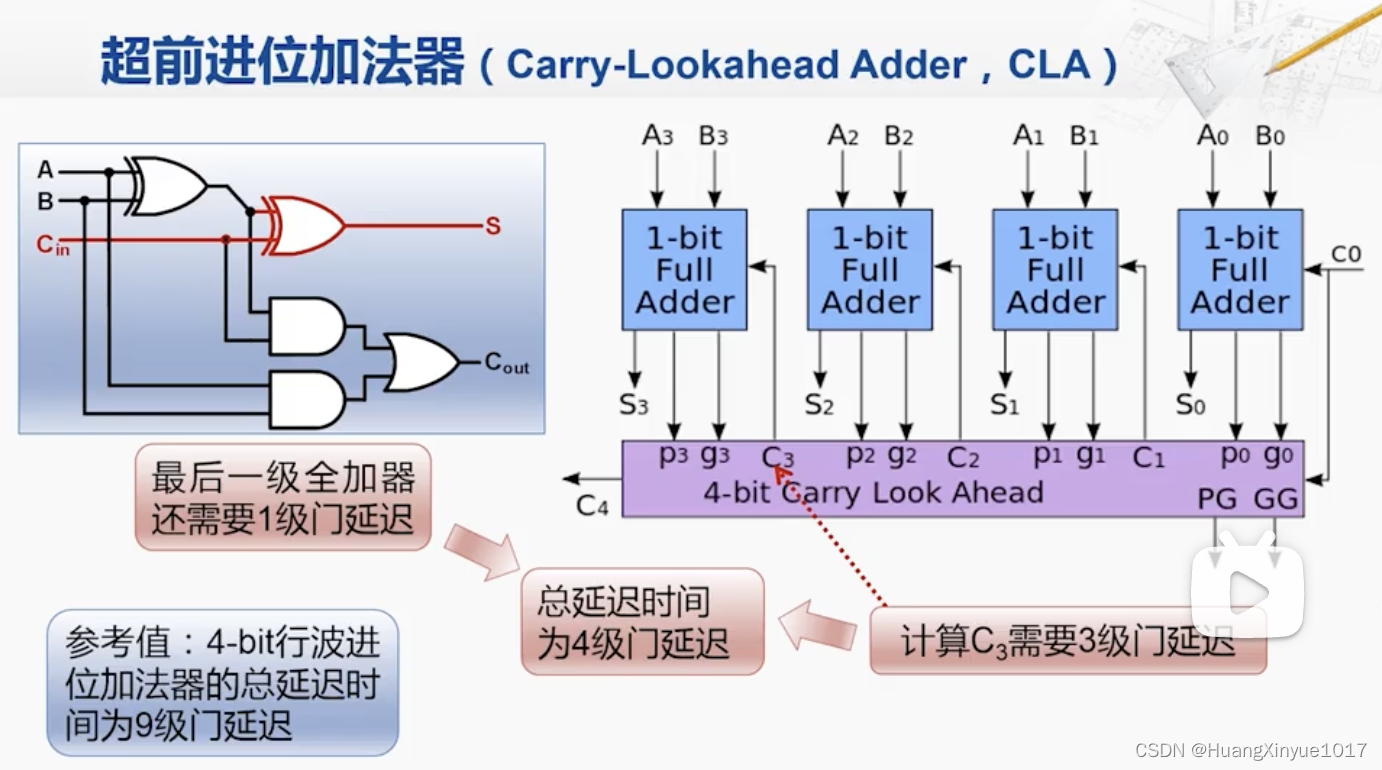

超前进位加法器(Carry-Lookahead Adder,CLA)

32-bit加法器的实现

- 如果采用行波进位,总延迟时间为65级门延迟

- 如果采用完全的超前进位,理想的总延迟时间为4级门延迟

- 通常的实现方法:采用多个小规模的超前进位加法器拼接而成;例如:采用4个8-bit的超前进位加法器连接成32-bit加法器

文章来源:https://blog.csdn.net/HuangXinyue1017/article/details/135527772

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- Python 集合(Sets)2

- 【科技素养题】少儿编程 蓝桥杯青少组科技素养题真题及解析第21套

- 在 TensorFlow 中启用 Eager Execution

- 【Amazon 预算设置】设置AWS服务用量预警并发送邮件提醒

- stable diffusion 基础教程-文生图

- SecureCRT连接vmware虚拟机的centos系统配置

- 【深入浅出RocketMQ原理及实战】「消息队列架构分析」帮你梳理RocketMQ或Kafka的选择理由以及二者PK

- springboot学生成绩管理系统源码和论文

- 接口测试之dubbo篇

- gRPC-Gateway:高效转换 RESTful 接口 | 开源日报 No.105