【【ZYNQ基础模块串口的意义】】

发布时间:2024年01月11日

ZYNQ基础模块串口的意义

ZYNQ的配置介绍

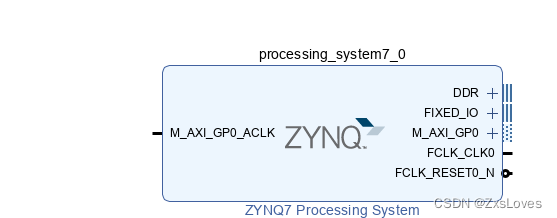

如此纯粹的引脚显示

DDR 用来接DDR FIXED_IO 主要用来调试

现在一步一步配置出PS与PL端想沟通的zynq核

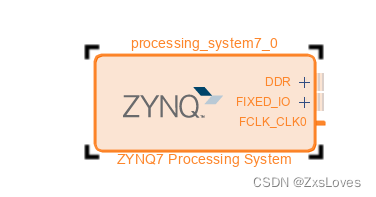

第一步给PL端添加一个时钟

因为 PS 与 PL端的时钟晶振不一样 我们可以通过一个PLL 来帮助我们生成想要实现的PL端时钟

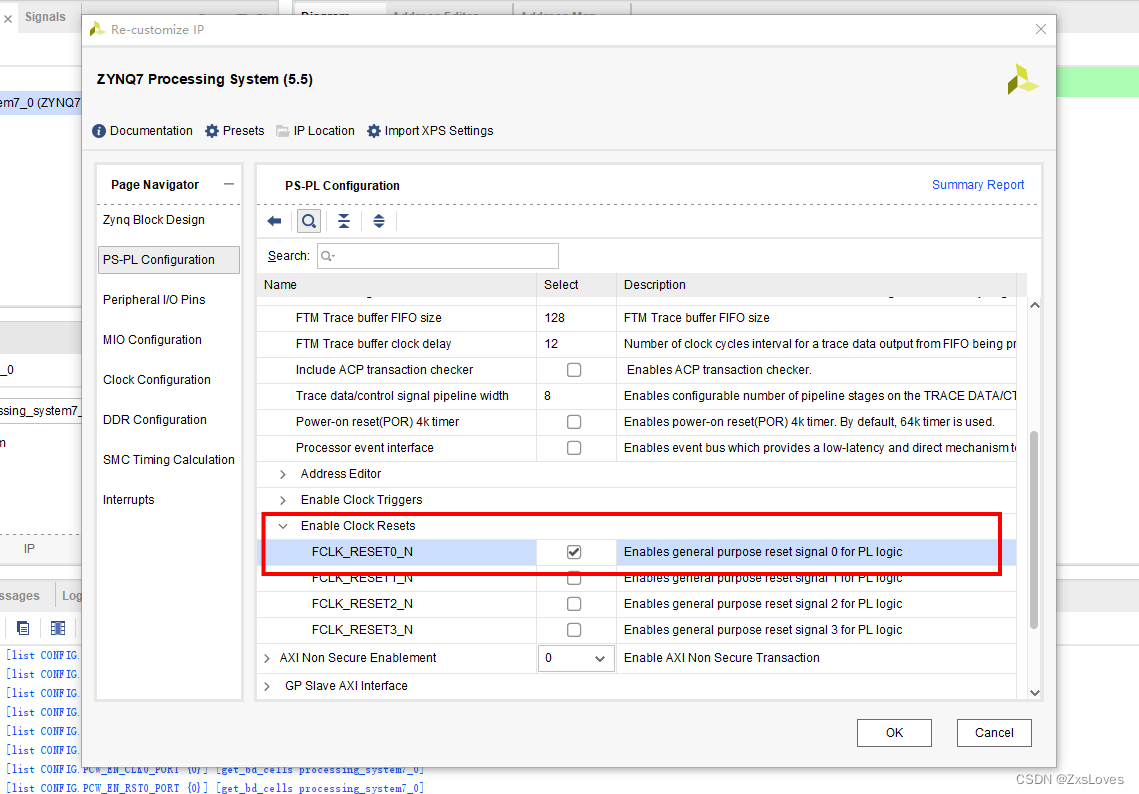

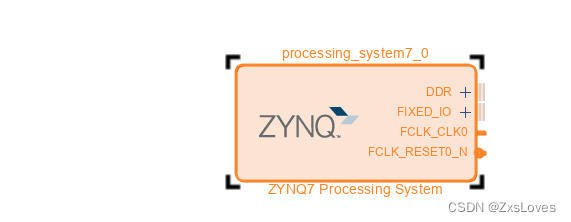

第二步 给PL端添加一个复位引脚

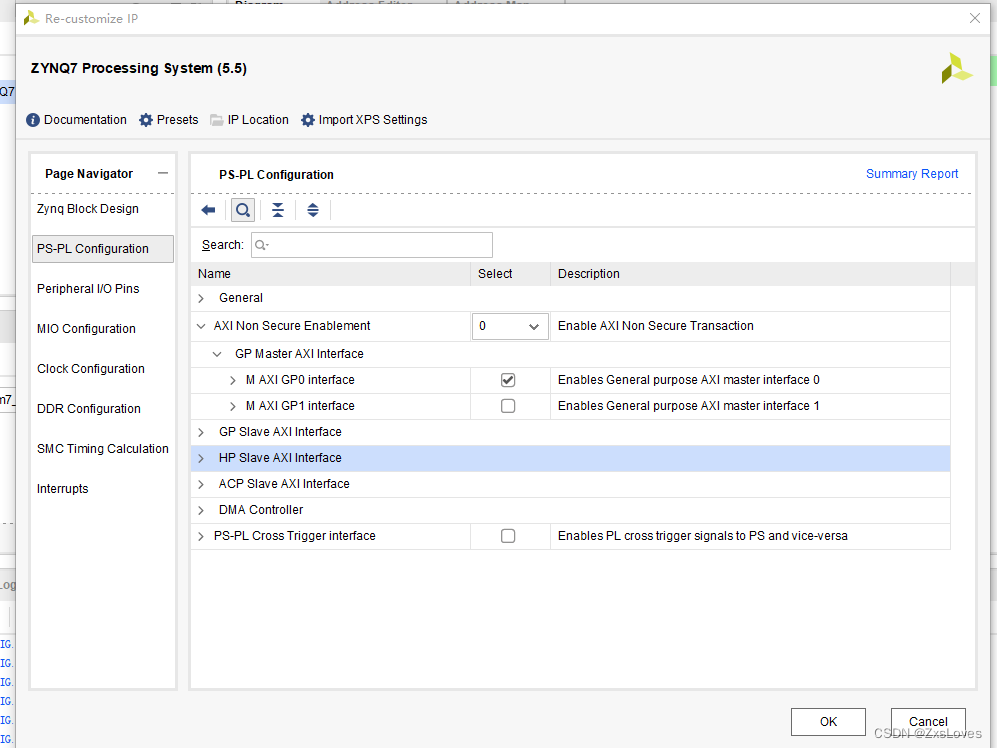

接下来添加 GP接口 用来传输控制信息

GP用来 PS作主机

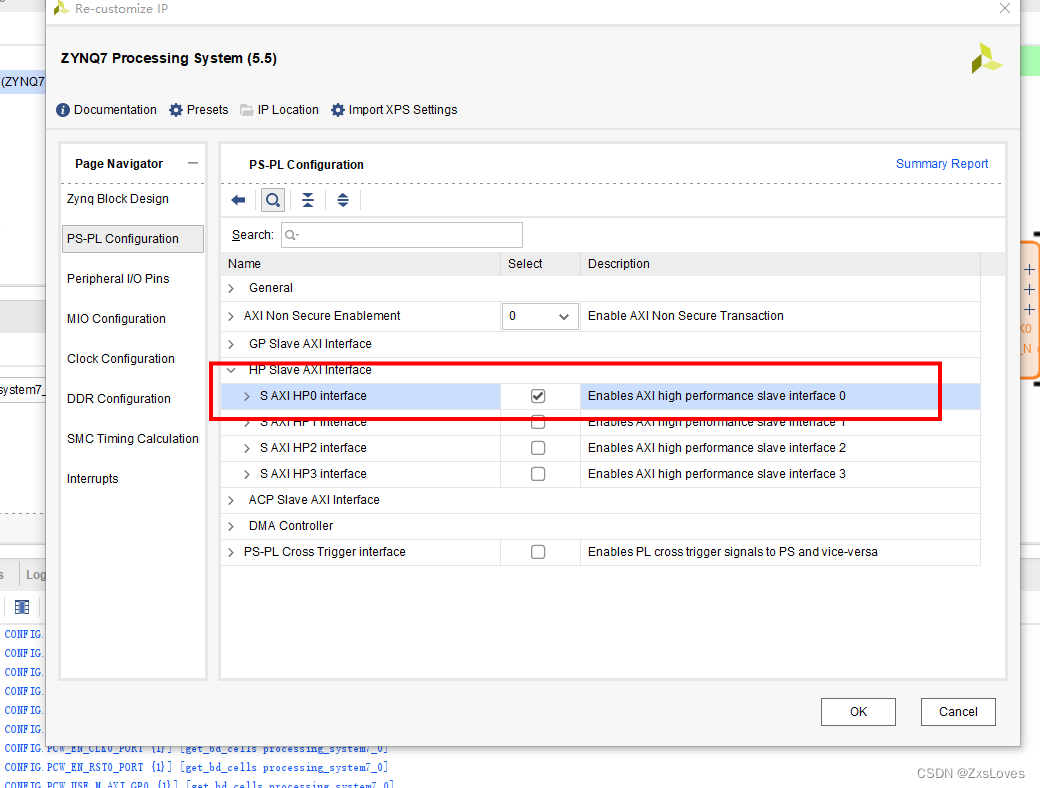

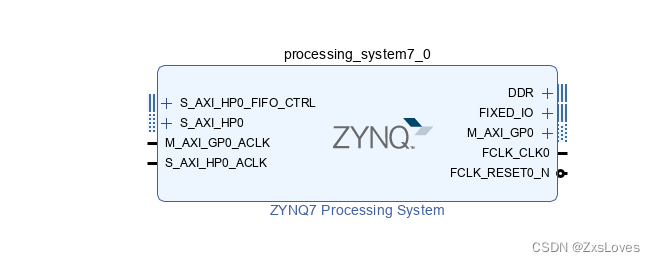

接下来 添加 PS 与PL互动的数据接口

S_AXI_HP0_FIFO_CTRL 是 Zynq UltraScale+ MPSoC 的 AXI High Performance (HP) Slave Interface 的 FIFO 控制寄存器接口。在这个接口中,S_AXI_HP0 表示第一个高性能 AXI 接口。

以下是该接口的一般含义:

- S_AXI_HP0:

AXI High Performance 接口的第一个实例。这是一个高性能的 AXI 总线接口,通常用于连接处理系统 (PS) 和可编程逻辑 (PL) 中的高性能外设或内存控制器。 - FIFO_CTRL:

FIFO 控制寄存器接口,用于控制和配置与该 AXI 接口相关的 FIFO。

这个接口允许对 FIFO 进行一些配置,如深度、中断使能等。通过配置这些参数,可以优化 AXI 总线与 FIFO 之间的数据传输。详细的配置和功能取决于具体的硬件设计和应用需求。

在使用这个接口时,设计者通常需要参考相关的技术文档和数据手册,以了解具体的寄存器配置和接口使用方法。

完成这是基础zynq串口的含义与配置

文章来源:https://blog.csdn.net/weixin_50965981/article/details/135539645

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 你是无醇葡萄酒的爱好者吗?

- 生活服务网站搭建的作用是什么

- AJAX入门到实战,学习前端框架前必会的(ajax+node.js+webpack+git)(九)

- 3分钟搞懂北交所交易规则和手续费

- 什么是 Web3.0

- libevent服务GET/POST的简单使用

- 关于Python里xlwings库对Excel表格的操作(二十八)

- 62.JavaWeb

- 货物数据处理,pandas和openpyxl联合处理

- C#用double.TryParse(String, Double)方法将字符串类型数字转换为数值类型