vivado RTL运行方法检查、分析方法报告、报告DRC

运行方法检查

Vivado Design Suite提供基于超快设计的自动化方法检查使用“报告方法论”命令的FPGA和SoC(UG949)方法论指南。您可以生成关于打开、详细阐述、综合或实现的方法论报告设计对于详细设计,方法报告会检查XDC和RTL文件。对于有关使用Tcl命令运行方法论报告的信息,请参阅Vivado Design SuiteTcl命令参考指南(UG835)。

建议:运行方法报告可以让您在在合成之前的精细化阶段,这节省了设计过程中的时间。强烈建议您对您的设计进行这些检查,并解决发现的任何问题。

运行报告方法

1.从“RTL分析”下的“流导航器”中,选择“打开详细设计”。

2.详细说明设计后,从Flow Navigator中选择Report Methodology在RTL分析下。或者,选择“报告”?→?报告方法。

注意:或者,您可以在Tcl控制台中输入以下命令:report_methodology-name<results_name>。

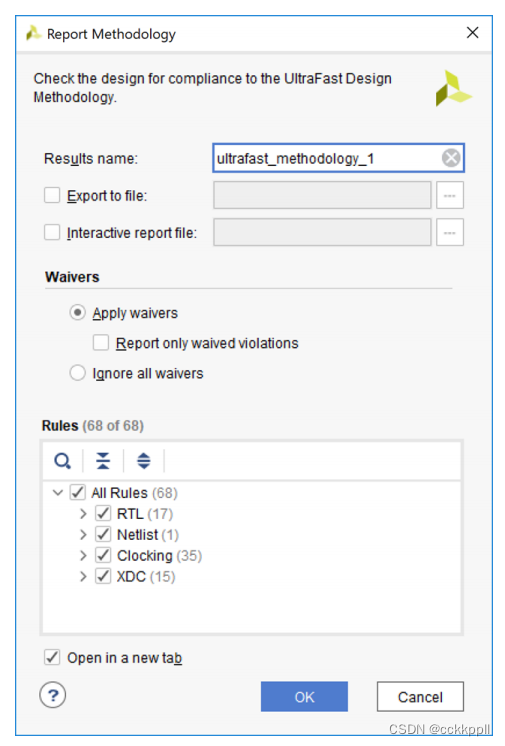

3.在“报告方法论”对话框中,设置这些选项,然后单击“确定”:

?结果名称:指定结果的名称,该名称显示在方法的选项卡中窗输入唯一的名称可以更容易地识别特定运行的结果在调试期间。

?导出到文件:如果要导出到文件,请指定用于编写报告的文件名到。要选择默认路径以外的路径,请使用浏览按钮。

?交互式报告文件:将报告保存到文件中。

?规则:允许您探索和指定要运行的规则。

?新选项卡:默认情况下,会为报告创建一个新选项卡。要禁用此选项,请取消选中在新选项卡中打开。

分析方法报告

如果发现违规,将打开“方法”窗口。该窗口显示违规行为,分组在各种规则类别下。

报告DRCs

以下部分介绍了在Vivado中选择DRC规则和分析DRC违规行为石斑鱼类。有关使用Tcl命令运行DRCs的信息,请参阅Vivado Design Suite Tcl《指令参考指南》(UG835)。有关创建自定义DRC的信息,请参阅VivadoDesign Suite用户指南:使用Tcl脚本(UG894)。

建议:运行RTL DRCs使您能够在详细说明过程中尽早发现设计问题在合成之前的阶段,这在设计过程中节省了时间。

选择DRC规则

1.从“RTL分析”下的“流导航器”中,选择“打开详细设计”。

2.设计完成后,从RTL下的Flow Navigator中选择Report DRC分析或者,选择“报告”?→?报告DRC。

注意:或者,您可以在Tcl控制台中输入以下命令:report_drc-name<results_name>。

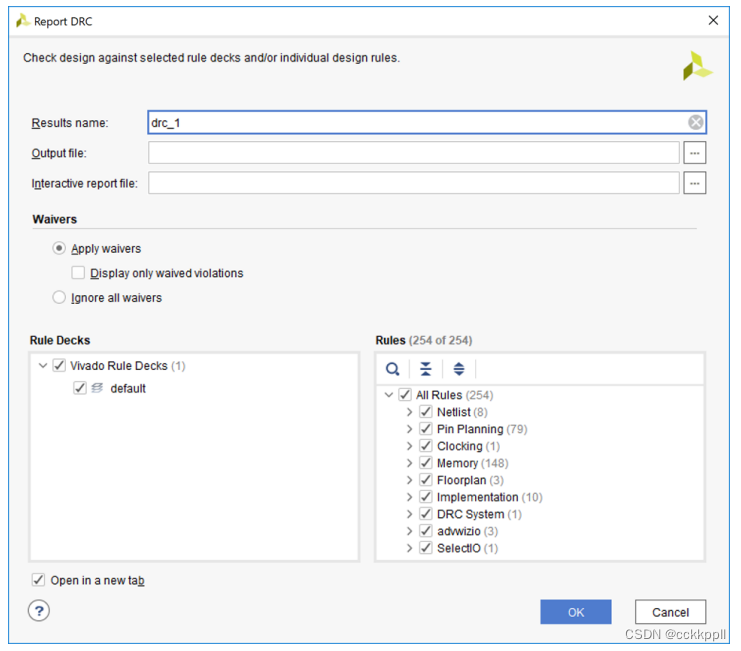

3.在“报告DRC”对话框中,设置以下选项,然后单击“确定”:

?结果名称:指定DRC结果的名称,显示在DRC的选项卡中窗输入唯一的名称可以更容易地识别特定运行的结果在DRC窗口中调试期间。

?输出文件:可以选择为DRC结果指定文件名。选择其他路径的步骤默认情况下,使用浏览按钮。

?交互式报告文件:将结果以AMD RPX格式写入指定的文件名。RPX文件是一个交互式报告,包含所有报告信息,可以使用open_report命令重新加载到Vivado Design Suite中的内存中。

?弃权:

?应用豁免:使用您创建的豁免来抑制您不再需要的DRC查看。有关更多信息,请参阅《Vivado Design Suite用户指南:设计》中的此链接分析与闭合技术(UG906)。

注意:使用“仅显示已放弃的违规行为”在“结果”中仅显示已取消的违规行为窗

?忽略所有豁免:忽略您创建的豁免。

?规则牌组:指定要在设计中运行的规则牌组。规则牌是设计的集合

为方便起见,将规则检查分组。在细化过程中,只有默认的规则组是可获得的其他规则组在FPGA设计流程的不同阶段可用,例如如在合成或实现之后。

?默认:运行AMD推荐的一组默认检查。

?opt_checks:运行与逻辑优化相关的检查。

?placer_checks:运行与放置相关的检查。?router_checks:运行与路由相关联的检查。

?bitstream_checks:运行与位流生成相关的检查。

?timing_checks:运行与时间约束相关联的检查。

注:详细设计不支持timing_checks规则组。

?incr_eco-checks:检查增量eco设计修改的有效性。

?eco_checks:检查工程变更单(eco)设计修改的有效性。

注意:对于详细设计,只有默认的规则组可用

?规则:指定规则组后,根据需要修改规则以运行

分析DRC违规

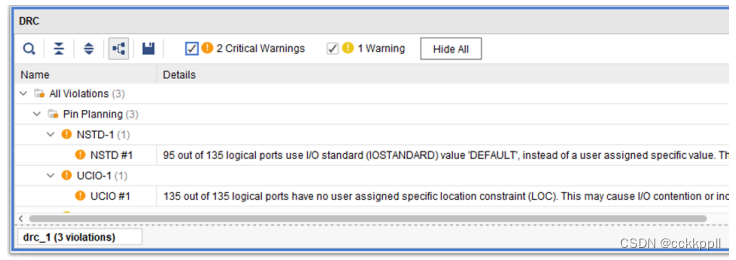

如果发现违规行为,将打开DRC窗口。DRC窗口显示违反规则的情况找到,分组在“运行DRC”对话框中定义的各种规则类别下。

违反规则的行为按严重程度进行分类,颜色编码如下:

?咨询:提供设计处理的一般状态和反馈。

?警告:表示由于约束或规范可能无法按预期应用。

?严重警告:表示将不应用或不应用某些用户输入或约束坚持最佳实践。强烈建议您检查这些问题并变化。

注意:在生成比特流期间,严重警告会升级为错误。

?错误:表示导致设计结果不可用的问题,如果没有该问题,则无法解决你的干预。设计流程停止。

提示:要只查看一种消息类型,请双击消息标题中的消息类型窗例如,双击“错误”仅显示错误消息。

您可以单独列出DRC违规行为,也可以按规则分组列出违规行为。要更改显示,请单击

“按规则分组”工具栏按钮。当违规行为单独列出时,可以单击Severity列的标头,用于按严重性对违规进行排序。要对列进行排序,请执行以下操作:

?单击列标题,以递增顺序对表中的数据进行排序。

?再次单击列标题,按降序对表中的数据进行排序。

注:有关更多信息,请参阅Vivado Design Suite用户指南:使用Vivado IDE(UG893)。当您在DRC窗口中选择违规消息时,与在其他打开的窗口(如“网表”或“原理图”窗口)中交叉选择冲突。这样可以快速定位和检查与具体违规行为。

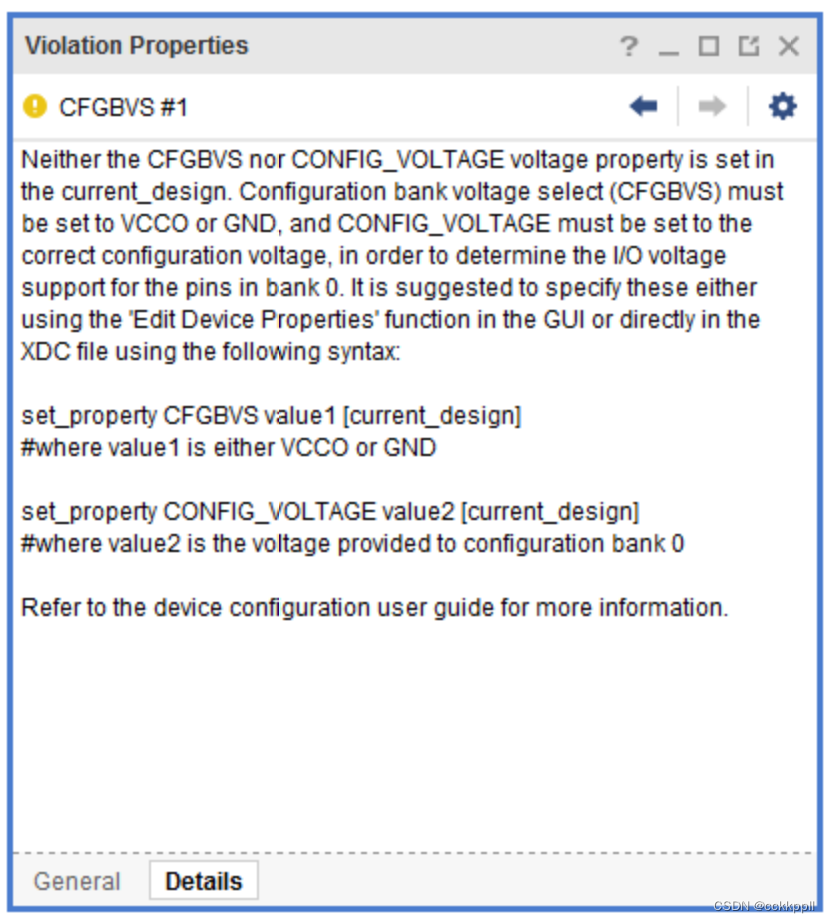

此外,默认情况下,冲突属性显示在“冲突属性”窗口中。在里面在DRC窗口中,也可以从右键单击菜单中选择“违规属性”以打开违规属性窗口。“违规属性”窗口同时显示违反DRC规则以及违反规则的设计元素的具体详细信息。详细信息视图包括指向违反DRC的特定设计对象的链接。单击链接以查看Netlist窗口、Device窗口、Schematic窗口或源中的设计对象RTL文件。

运行RTL DRCs的Tcl命令以下是相关的Tcl命令:

?Tcl命令:report_drc

?Tcl命令示例:report_drc-name drc_1

注意:默认情况下,会生成基于文本的报告。您可以使用-name选项创建报表的交互式选项卡。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- SpringBoot ElasticSearch 聚合统计

- HTML--CSS--超链接样式以及鼠标样式自定义

- 用队列实现栈,力扣

- 文心一言 VS 讯飞星火 VS chatgpt (163)-- 算法导论13.1 3题

- 人工智能计算机视觉:解析现状与未来趋势

- echarts实现控制图(设置阈值上下限超出变色)

- srand函数与rand函数的简介

- SpringBoot+Mybatis+MySQL+Vue实现CRUD+分页

- 浮动静态路由及负载均衡-新版( 10)

- 干货|Google ads谷歌广告投放详细步骤与技巧