ARM GIC(三) gicv2架构

ARM的cpu,特别是cortex-A系列的CPU,目前都是多core的cpu,因此对于多core的cpu的中断管理,就不能像单core那样简单去管理,由此arm定义了GICv2架构,来支持多核cpu的中断管理

一、gicv2架构

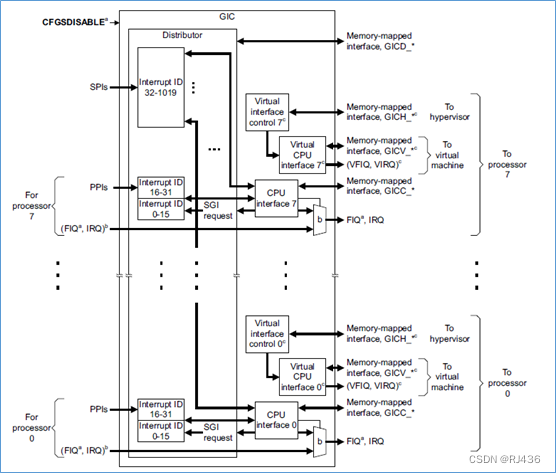

GICv2,支持最大8个core。其框图如下图所示:

在gicv2中,gic由两个大模块组成:

distributor:实现中断分发,对于PPI,SGI是各个core独有的中断,不参与目的core的仲裁,SPI,是所有core共享的,根据配置决定中断发往的core。最后选择最高优先级中断发送给cpu interface。寄存器使用 GICD_ 作为前缀。一个gic中,只有一个GICD。

cpu interface:将GICD发送的中断信息,通过IRQ,FIQ管脚,传输给core。寄存器使用 GICC_ 作为前缀。每一个core,有一个cpu interface。

virtual cpu interface:将GICD发送的虚拟中断信息,通过VIRQ,VFIQ管脚,传输给core。每一个core,有一个virtual cpu interface。而在这virtual cpu interface中,又包含以下两个组件:

virtual interface control:寄存器使用 GICH_ 作为前缀

virtual cpu interface:寄存器使用 GICV_ 作为前缀

图中的virtual interface,是用于支持虚拟中断,本系列不讨论虚拟中断。

GICv2支持中断旁路模式,也就是gic外部的FIQ,IRQ直接接到core的FIQ,IRQ上,相当于gic是不使能的。也就是CFGSDISABLE是有效的,将GIC给无效掉。

gicv2,定义了自己的一些寄存器,这些寄存器,都是使用memory-mapped的方式去访问的,也就是在soc中,会留有一片空间,给gic。cpu通过访问这部分空间,来对gic进行操作。

寄存器,分为以下:

GICD_*: distributor的寄存器

GIC

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- ffmpeg中AVFrame解码linesize确定

- JS常用插件 Swiper插件 实现轮播图

- DWM1000 MAC层

- Vue中除了使用v-model指令外,实现双向数据绑定的方法有哪些?

- mysql变量-show_compatibility_56

- 练习题 删除链表的倒数第N个结点

- 精通UI弹窗设计的5个规范和技巧!

- 分享一些网站关键词优化的技巧和工具

- JOSEF约瑟 零序过流继电器LGL-110/AC AC220V 0.01~9.99A 柜内安装

- LeetCode 2171. 拿出最少数目的魔法豆