Marin说PCB之电源完整性之直流压降仿真CST--01

电源完整性能是一个老生常谈的话题, 电源直流压降(DC IR Drop)是指在电路中由于电源电压的不稳定或电源电阻的存在而导致的电压降低现象。在电路中,电源的直流电压会在电路中的导线、电阻、电容等元件上产生一定的电压降,从而影响电路的正常工作。

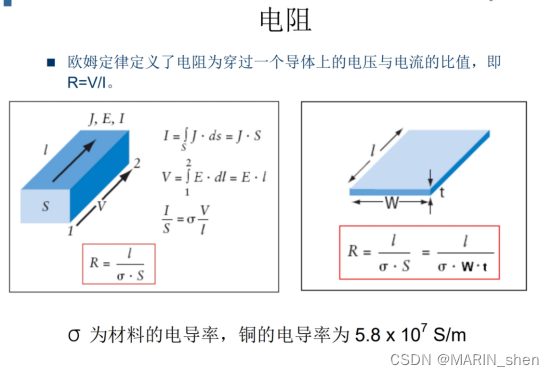

我们通过欧姆定律的公式 R=U/I

得知由于导体并非理想,所以会存在电阻,导致电压上的下降。我们从上面的公式也可以得出一个结论就是:导体的电阻值与导体的长度成正比,与导体的横截面积成反比,若我们将互联的走线的长度加倍,则走线导体的电阻值加倍;若是我们增加一倍的导体的横截面积,则导体的电阻值减少一倍。这个也是我们在改一些PI工程师的意见的时候经常会遇到让你把电源走线能够加粗的加粗,能够铺铜的尽量不要走线去做了。

我们经常会在一个主芯片的器件资料中看到类似于芯片的电源要求,常见主芯片的一些电源Vdd的误差是(+-%3到+-%5),一些core电源的直流压降可能要求会更加严格一些,有的是+-1%左右了。

我们往往会把手册这些电源的直流压降的误差直接当做是实际的sink端口的电源的直流压降的误差值了,这个是不正确的。一般来说我们芯片手册的电源直流压降的误差是其实是包括了直流压降和交流噪声的总和的,不过很多的电源芯片厂商都没有给出一个推荐的比例关系,IC 的容忍值通常 5-10%,这个值里既包含了电源噪声,又包含了直流压降,占比值为 2:8。例如,例如:5V 电源,波动范围 5%,波动值为 5Vx5%=250mV,实际负载端的电压为 4.75V~5.25V, 直流压降所占比例为 250mV X 80%=200mV,也就是说负载端的直流压降部分可以接受的范围为 4.8V-5.2V。

这个算的话是比较严格的了,我这边通常的做法就是EE同事那边先去做出一份WCCA表格,计算出VRAM的最恶劣的使用情况,然后加上负载端口的芯片手册的要求,然后对比一下两者的下限余量即可,就是我们PCB板子上走线的允许的压降误差了。

好了这次我就给大家分享一下我之前给乌克兰同事学的如何使用CST软件去做电源的直流压降仿真,其实cadence也有自己的仿真软件是PowerDC这个软件,这个软件在win10 cortana搜索即可,或者在Cadence\Cadence_SPB_17.2-2016\tools\bin找到.powerdc.exe,我的是Cadence17.2,要是你的cadence是16.6可能需要额外安装sigrity,不过后面还有热仿真、PowerSI仿真等,装17.2还是省事一些,后面小编会分几期讲解之前用的power?dc去仿真电源直流压降,这次主要还是说CST这个软件了。好了,大家请退后,小编我要开始讲课了。

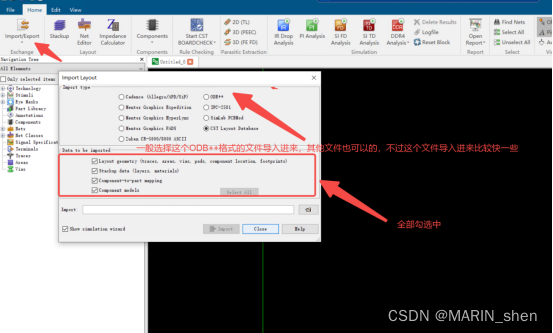

1,首先打开软件找到这个下图所示的这个界面

2,在home里面选中import。导入你的文件,一般最好的格式是ODB++文件。

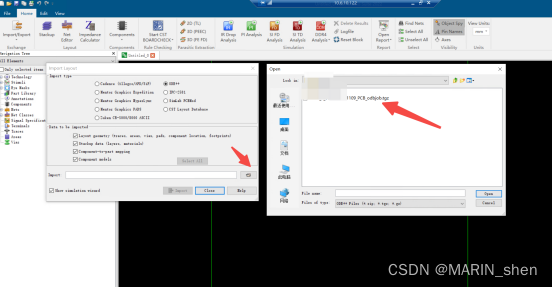

3,在import那栏路径下找到你输出ODB++文件。

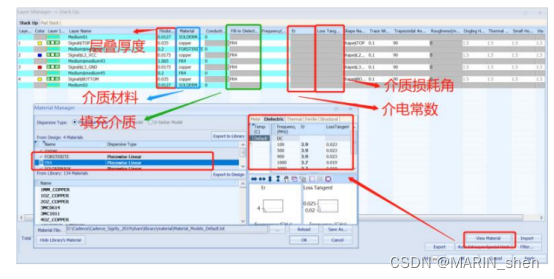

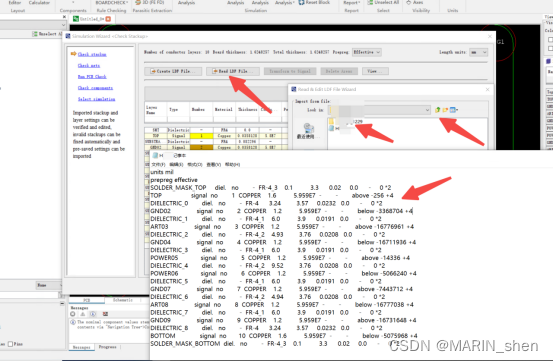

4,导入好文件后就可以去修改你的层叠参数了,这个地方要去注意一下,CST和cadence自带的仿真软件power --DC在这个层叠设置上还是有一些区别的,power --DC这个软件是可以直接改一些参数的,如下图所示:

??

但是CST这个软件就不能这样改了,CST软件是只能编辑已经设置好的层叠的文本文件,然后再去读取进来。

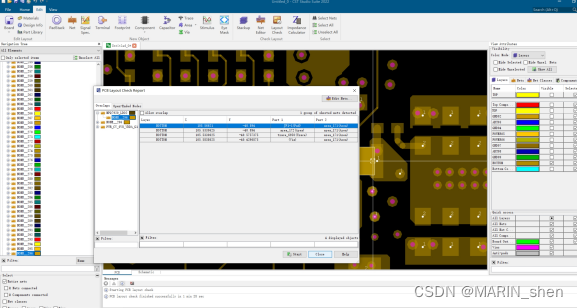

5,这个层叠设置好后最好是去检查一下板子上有没有叠孔,开短路等,所以说这个仿真一般是需要layout那边做到布线评审状态的时候才发出来比较好,因为用allegro软件检查起来比较方便一些,这个毕竟是一个第三方的仿真软件而已。具体设置如下图所示

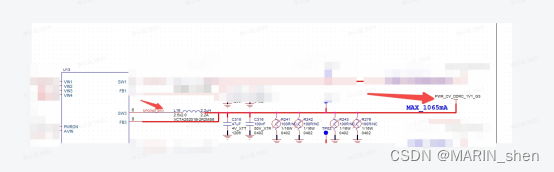

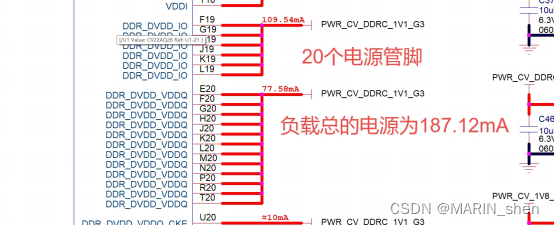

6,pcb检查没有问题后,我们单板需要仿真的电源网络为PWR_CV_DDRC_1V1_G3,

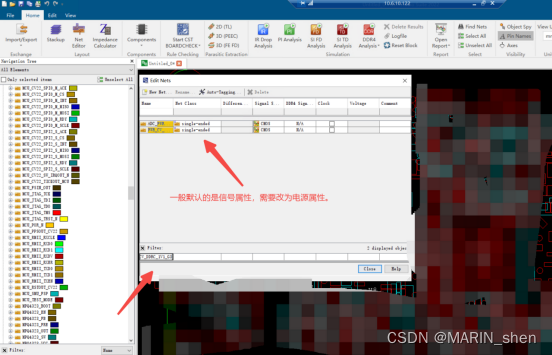

我们首先要把电感前后端口的网络设置成power属性,即MPQ7920_SW3和PWR_CV_DDRC_1V1_G3都要设置成power属性,这个设置在NET Editor里面设置好你的选中的电源网络信号,把相应的信号属性改为power属性即可,

7,分离元器件电感前端的网络MPQ7920_SW3和上面一样的设置即可。

8,还可以直接在这个里面输入网络名字在这个里面改网络属性也是可以的,看个人的使用习惯了。

9,最后记得把板子上所有带GND的NET设置成GND属性。

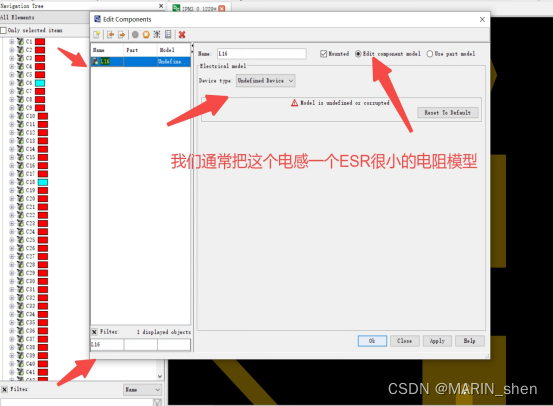

10,下面就是开始我们的Vram端口的器件的设置了,首先是设置分离器件电感,具体操作如下图所示:

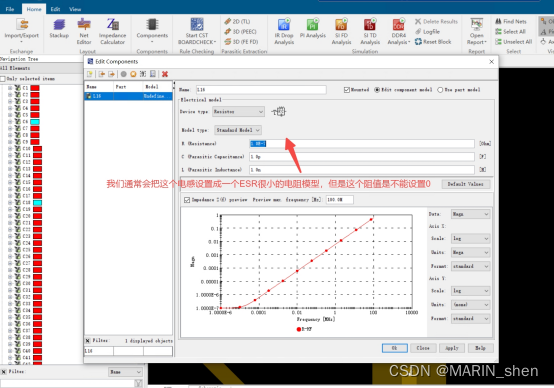

11,我们在仿真的时候不考虑电感的内阻带来的影响的话,我们就把电感的内阻设置成一个ESR很小的电阻模型,

12,我们仿真是直流电源的压降,对于这些器件我们就不用再去考虑器件本身的L和C带来的影响了,我们可以把电阻阻值设置成很小的内阻,就类似于一根导线了,但是切记不能把电阻值设置为0 了。

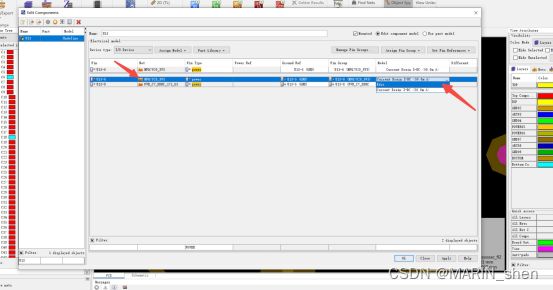

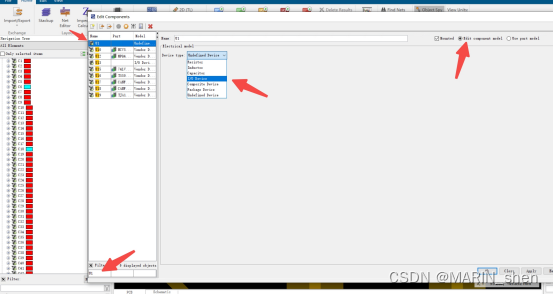

13,接着我们就要开始设置我们的VRAM芯片和我们的sink负载端口了。首先找到你的Vram电源芯片,具体的设置如下图所示:这个和电感的设置的区别是模型的类别要选择是I/O device了。

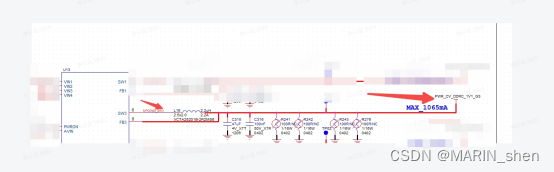

U13上面有两个电源网络属性,这个就是我们前面已经设置好的了。打开原理图我们通常是把U13的SW管脚当做是电源输出端口,FB反馈脚当做是一个电流消耗很小的SINK端口。

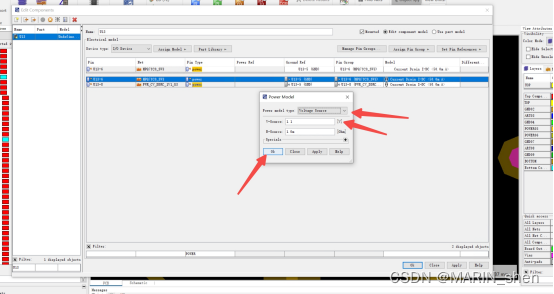

14,在CST设置具体如下图所示:

1,首先把SW管脚设置成Voltage source。

2,接着把FB管脚设置成current drain。

15,需要注意的一点就是:其实除了vram的SW这个网络需要设置成source,其他的类似于MCU的ADC,FB等都可以统一设置成SIKN端口,也就是软件中的current drain。

16,可能有的视频教学中会把Vram电源输入端口也考虑进去的,类似下图所示的级联的仿真。

但是我们在仿真的时候就不需要考虑太多级联的电源了,即不考虑我们的输入端口的电电压波动带来的影响,我们只看vram芯片的输出部分的SW区域的电压就好了。我们一般都是一段段的去看我们的电源压降的情况。这样观察起来更加直观了,当然你若是想做这种的级联仿真也是可以的,看个人习惯了吧。

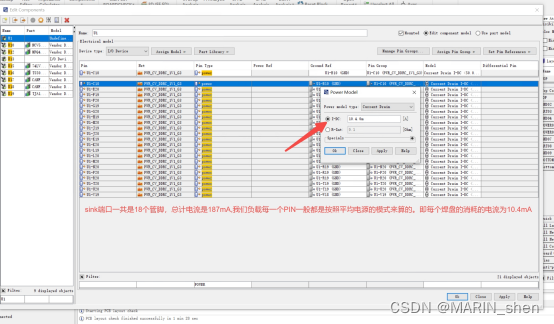

17,下面就是开始sink端口的设置了,一般我们都是在Equal Current 模式下 Sink 端口的每个电源 pin 的电流相等,等于总电流除以 pin 数。

sink端口芯片的设置具体如下图所示:

1,

2,

3,

4,

18,ADC采样电阻的设置和前面的分离元器件电感的设置是一样的:

19,MCU也是负载芯片,设置方法和上面的负载芯片U1一样,就是负载端口的电流消耗比较小,一般设置成10MA即可。

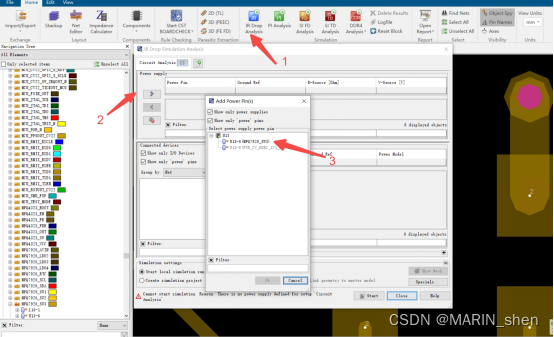

20,以上的器件和网络都设置好以后,我们就可以开始进行电源的直流压降仿真了,具体步骤如下图所示:

?1,

2,

3,

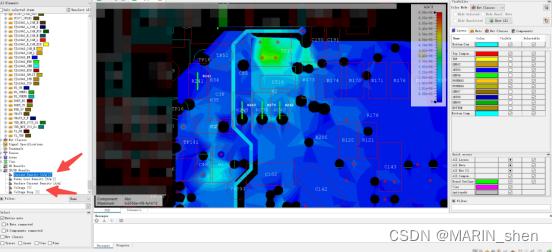

4,下图就是仿真后的结果了:包括一些数据和2D以及3D的仿真结果。

以上就是这次电源直流压降仿真的所有步骤了,后面我这边再去单独出一遍文章讲解如何去看这些仿真数据。小编在这里祝愿大家在新的一年里,财源广进,事业步步高升。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!