基于PCIe的NVMe学习

一:基本概念

1.UltraScale:是Xilinx ZYNQ 系列产品

2.spec:大家现在别纠结于具体的命令,了解一下就好。老板交代干活的时候,再找spec一个一个看吧————猜测估计是命令表之类的。

Admin指令:——如下:

IO指令——如下:

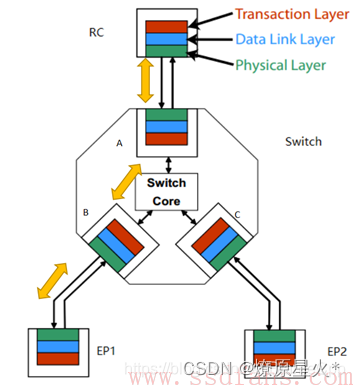

3.TLP报文部分:在学习TLP报文之前需要了解pcie的分层结构,绝大多数的总线或者接口(也包括pcie),都是采用分层实现的如下图:

事务层(Transaction Layer)根据上层(软件层或者应用层)请求(Request)的类型、目的地址和其它相关属性,把这些请求打包,产生TLP,也就是Transaction Layer Packet。然后这些TLP往下,经历数据链路层,物理层,最终到达目标设备。根据软件层的不同请求,事务层产生四种不同的TLP请求:

-

Memory (主流)

-

IO

-

Configuration(非主流——上电枚举和配置阶段才会有host发起)

-

Message(非主流——中断,或者有错误等情况下)

4.最常见的tcp:PCIe线上主流传输的是Memory访问相关的TLP,Host与device,或者device与device之间,数据都是在彼此的Memory之间

5.除了,Memory write和Message是 psot(及不需要回应的tlp外),其余tlp都是 non—post(及需要响应的)

二:pcie相关知识(用xilinx的ip核进行管理,相关参数在gui界面设置)

1.但PCIe是可以最多32条道的(x32)

2.全双工模式

3.pcie拓扑结构:所有pcie的设备均挂在pcie总线上,谁要使用需要得到总线相关的使用权。

4.PCIe Endpoint,就是PCIe终端设备,比如PCIe SSD,PCIe网卡

5.Host与PCIe设备之间,或者PCIe设备与设备之间,数据传输都是以Packet(Transaction Layer Packet)形式进行的.

7.RC是树的根,或者主干,它为CPU代言——所有的配置空间(Configuration)的访问,都是Host发起的,确切的说是RC发起的

如上图:Switch就是负责:脱衣服看数据究竟是发送给哪个EP1的。

8.一个TLP最大载重是4KB,数据长度大于4KB的话,就需要分几个TLP传输。

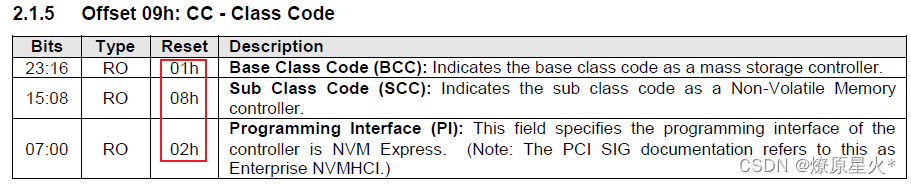

9.gui 界面的class code ——010802

三:ssd相关知识

1.现在很多SSD都开始使用PCIe接口——为了追求速度更快,上限速度就是pcie的接口速度

2.SSD——半双工

四:NVMe相关知识——他是一种通信协议

1.NVMe是一种Host与SSD之间通讯的协议,它在协议栈中隶属高层——在三国的话,就是诸葛亮的角色

2.军师设计好计谋,就交由手下五虎大将去执行——虎将PCIe去完成任何命令。

3.虽然NVMe的命令可能可以由别的接口协议完成,但NVMe与PCIe合作形成的战斗力无疑是最强的。

4.AHCI和SATA的协议犹如刘备去指挥虎将PCIe——垃圾。还需诸葛(NVMe)来指挥。

5.所有SATA接口的SSD,你去看性能参数,会发现都不会超过600MB/s——垃圾。

6.NVMe有两种命令:一种叫Admin Command,用以Host管理和控制SSD。二种叫I/O Command,用以Host和SSD之间数据的传输。

7:命令有了,那么,Host又是怎么把这些命令发送给SSD执行呢——?

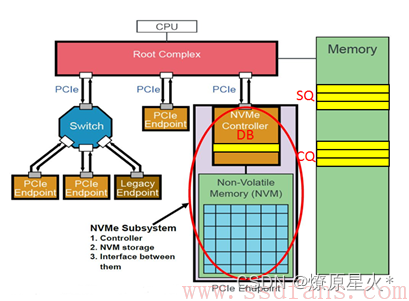

8:NVMe有三宝如下图——DB ,SQ,CQ

9:如上图,RC(root complex)就是CPU的代言人,小蜜。

10.

说,NVMe处理命令需要几步?答:八步:

第一步:Host写命令到SQ;

第二步:Host写DB,通知SSD取指;

第三步:SSD收到通知,于是从SQ中取指;

第四步:SSD执行指令;

第五步:指令执行完成,SSD往CQ中写指令执行结果;

第六步:然后SSD发短信通知Host指令完成;

第七步:收到短信,Host处理CQ,查看指令完成状态;

第八步:Host处理完CQ中的指令执行结果,通过DB回复SSD:指令执行结果已处理,辛苦您了!

11.?有SQ就必然有CQ? ,SQ/CQ中的”Q”,是Queue,队列的意思.

12.无论host想从ssd读数据还是写数据(host都是拿来主义,ssd都是快递员)Host也有两种方式来告诉SSD数据所在内存位置,一是PRP (Physical Region Page, 不是P2P!),二是SGL (Scatter/Gather List)。

13.Physical Region Page:PRP Entry本质就是一个64位内存物理地址。

五:解读复旦大学的demo

1.用MicroBlaze核解析Admin指令,IO指令用PL逻辑实现。——因为nvme有两种命令形式为Admin指令(Host管理和控制SSD),IO指令(以Host和SSD之间数据的传输)

2.设计中创建了一个Admin Queue,8个IO Queue(如demo 工程)

3.启用了XDMA的4条stream通道(传输数据。数据可以是SQE、CQE等指令,也可以是要转移的数据。在demo设计中,2条steam用于读写SQE/CQE/PRP,2条steam用于读写数据。)、descriptor bypass通道(Descriptor Bypass仅针对通道提供了描述符旁路模式的仿真模型。此设计可以扩展以支持其他通道。可通过1111来全部打开)(找到了均通过XDMA的ip的gui界面设定的)。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!