数字IC设计流程

目录

?

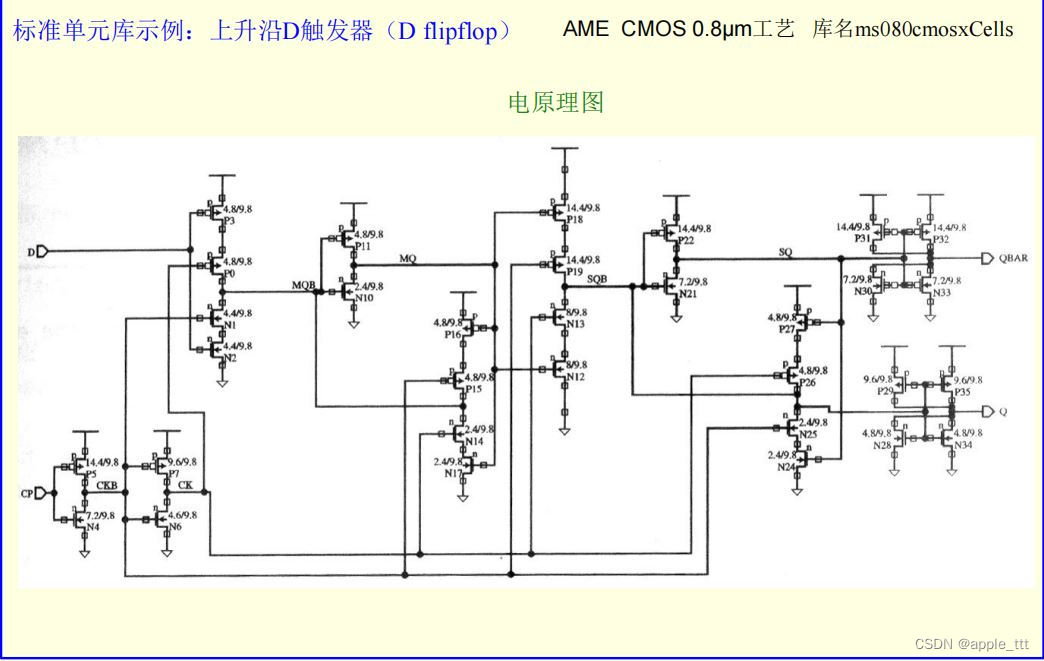

5.2 标准单元库示例:上升沿D触发器(D flipflop)

?

一、引例——RFID芯片

? ? ? ? 大家应该对RFID并不陌生,所谓的RFID技术其实就是无线电射频技术 ( Radio Frequency Identification,RFID)的英文简称,该技术主要借助于磁场或者是电磁场原理,通过无线射频方式实现设备之间的双向通信,从而实现交换数据的功能,该技术最大特点就是不用接触就可以获得对方的信息。

? ? ? ? 其中的无源RFID系统通过电磁感应线圈获取能量来对自身短暂供电,完成信息交换。其结构简单、成本低、故障率低,使用寿命较长。然而,无源 RFID的有效识别距离通常较短,一般用于近距离的接触式识别。无源RFID系统的典型应用包括:公交卡、二代身份证和校园卡等。

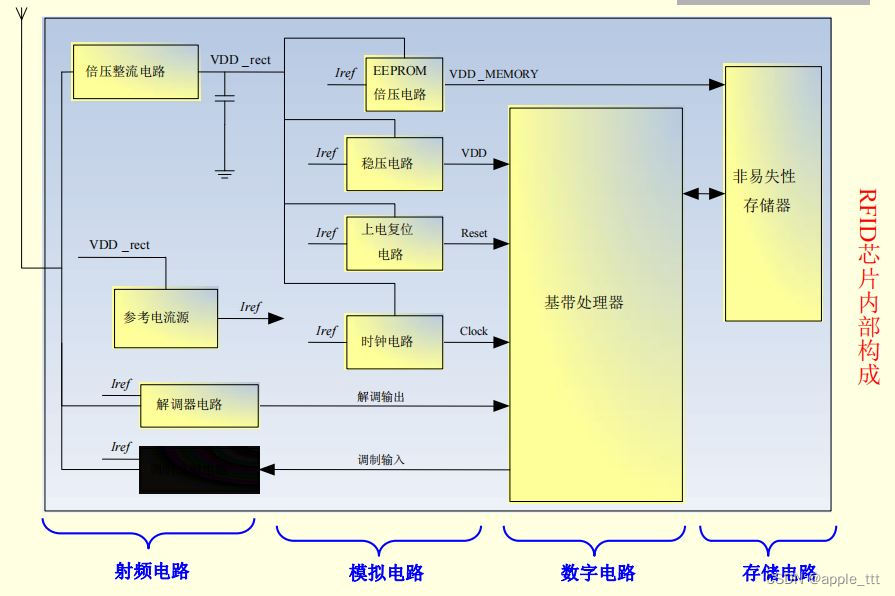

? ? ? ? 其内部结构如下:

? ? ? ? 其内部主要分成了射频电路模块、模拟电路模块、数字电路模块和存储电路模块。

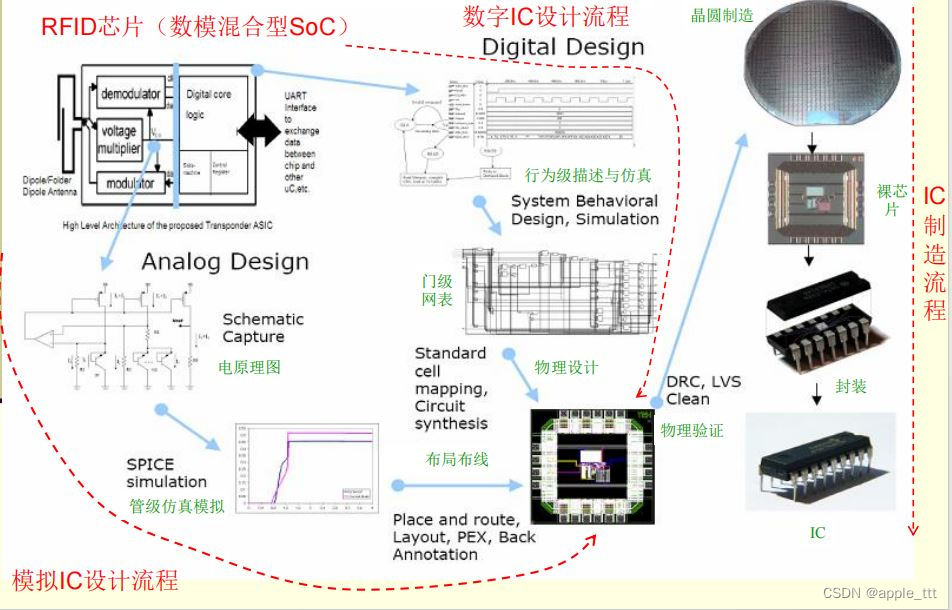

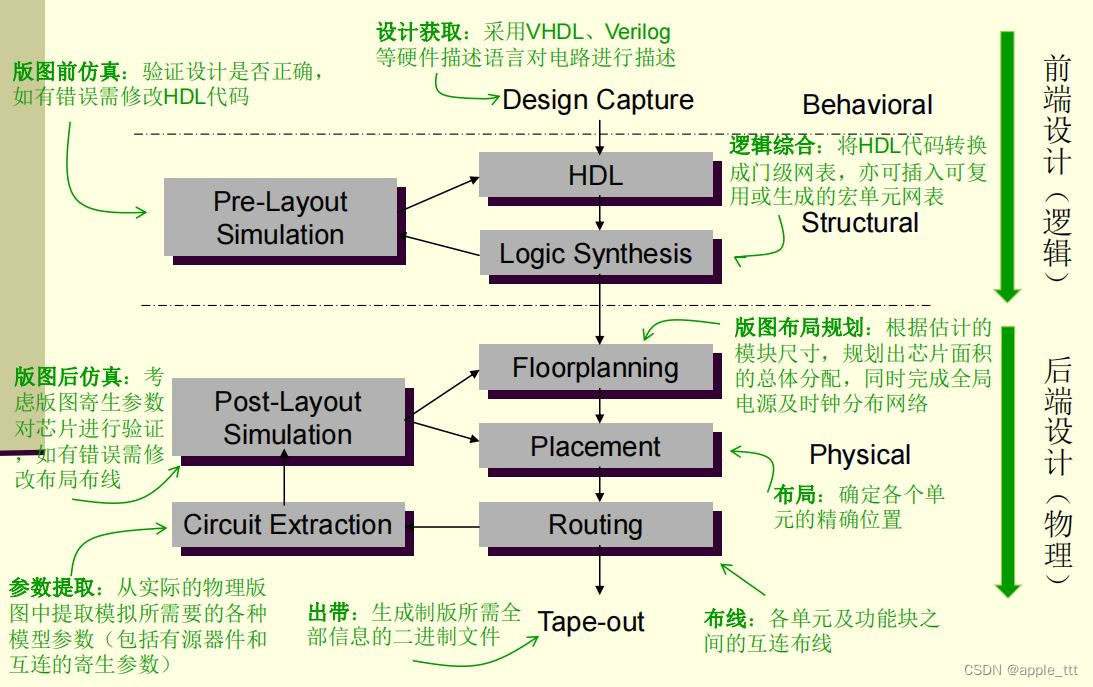

? ? ? ? 主要设计流程如下:

? ? ? ? 可以看到,设计的时候模拟IC与数字IC是分开的,模拟的部分首先设计出电路原理图,然后经过管级仿真模拟、布局布线;数字的部分则是通过行为级描述和仿真得出门级网表,然后经过物理设计。在此之后统一进行物理验证、晶圆制造、封装等过程,最终得到我们的IC产品。这里我们关注的重点是数字IC设计的流程。

二、数字IC设计流程的发展史

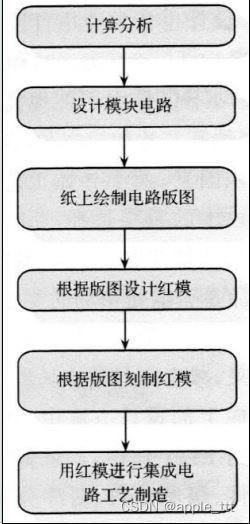

第一阶段:人工设计

? ? ? ? 这个阶段的设计规模大概是几百个门。其设计流程如下:

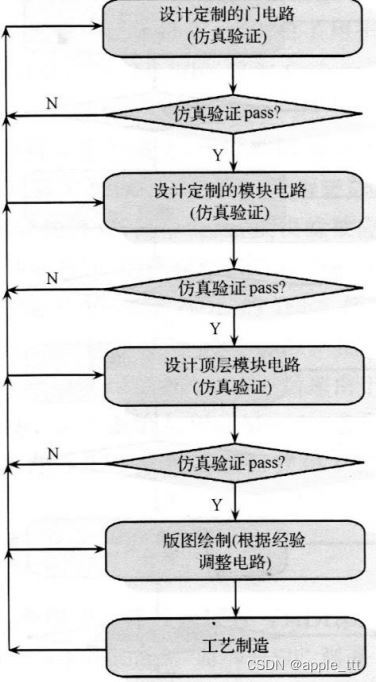

第二阶段:人工为主、计算机为辅?

????????这个阶段的设计规模大概是几万个门。采用Bottom-up流程,使用计算机工具:CAD(Computer-Aided Design)工具。其设计流程如下:

第三阶段:人工与计算机平分秋色

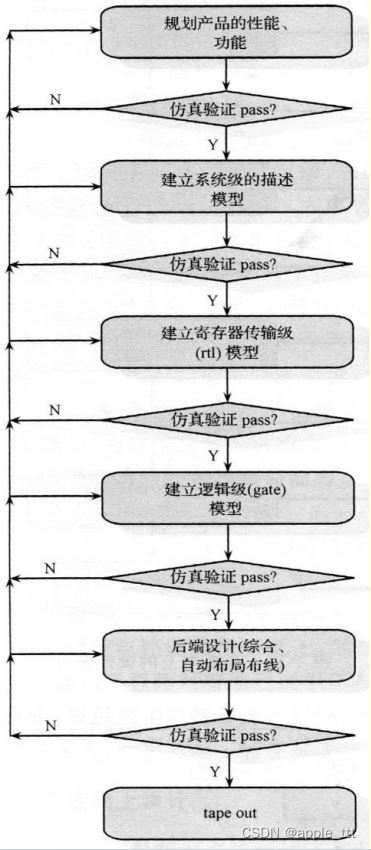

????????这个阶段的设计规模大概是几百万个门。采用Top-down流程,使用计算机工具:EDA(Electron Design Automation)工具。其设计流程如下:

第四阶段:计算机为主、人工辅助

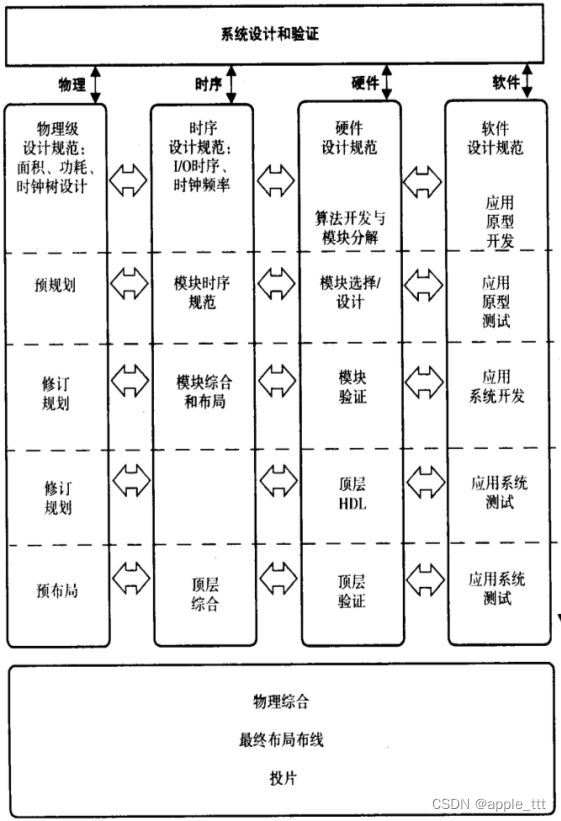

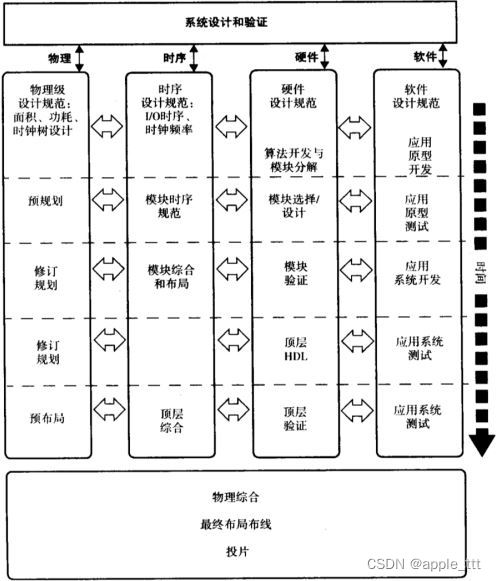

????????这个阶段的设计规模大概是几亿个门。采用Top-down与Bottom-up结合的流程,使用ESL(Electron System Level)工具。其设计流程如下:

三、目前主流的数字IC设计流程

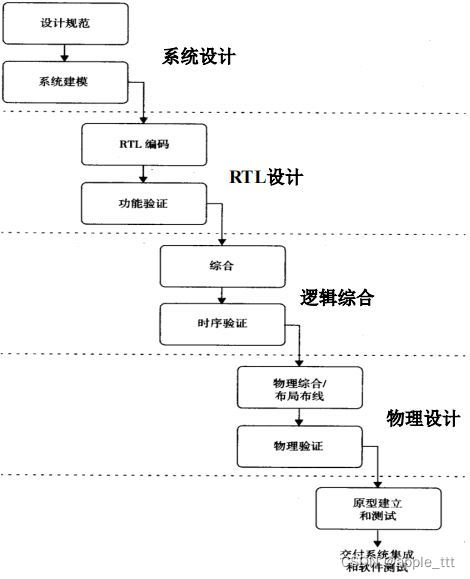

1、ASIC设计流程

????????瀑布式,由顶向下,先时序后物理,先硬件后软件,层次清晰,容易实现

2、Soc设计流程

?

四、Top-Down设计流程

五、工艺库

5.1 概述

- 标准单元(Standard cell):基本组合逻辑门和时序控制单元等

- 宏单元(Macro block):加法器、ALU、SRAM、多路选择器等

- 输入/输出单元(I/O pad cell):输出缓冲器、ESD保护单元等

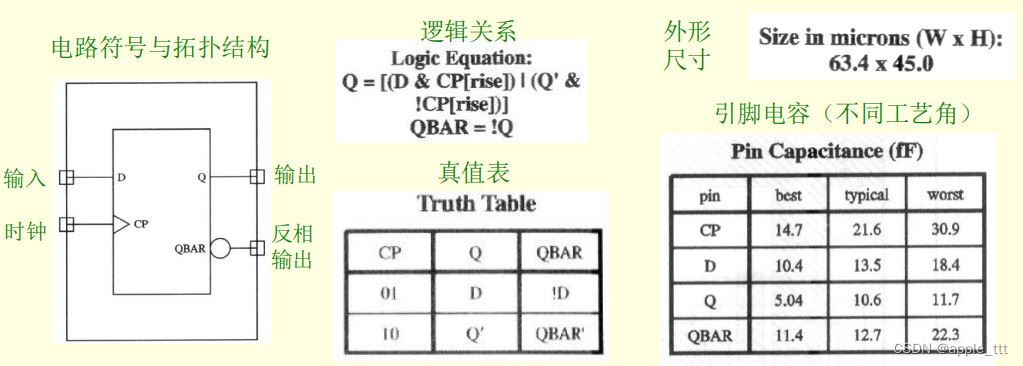

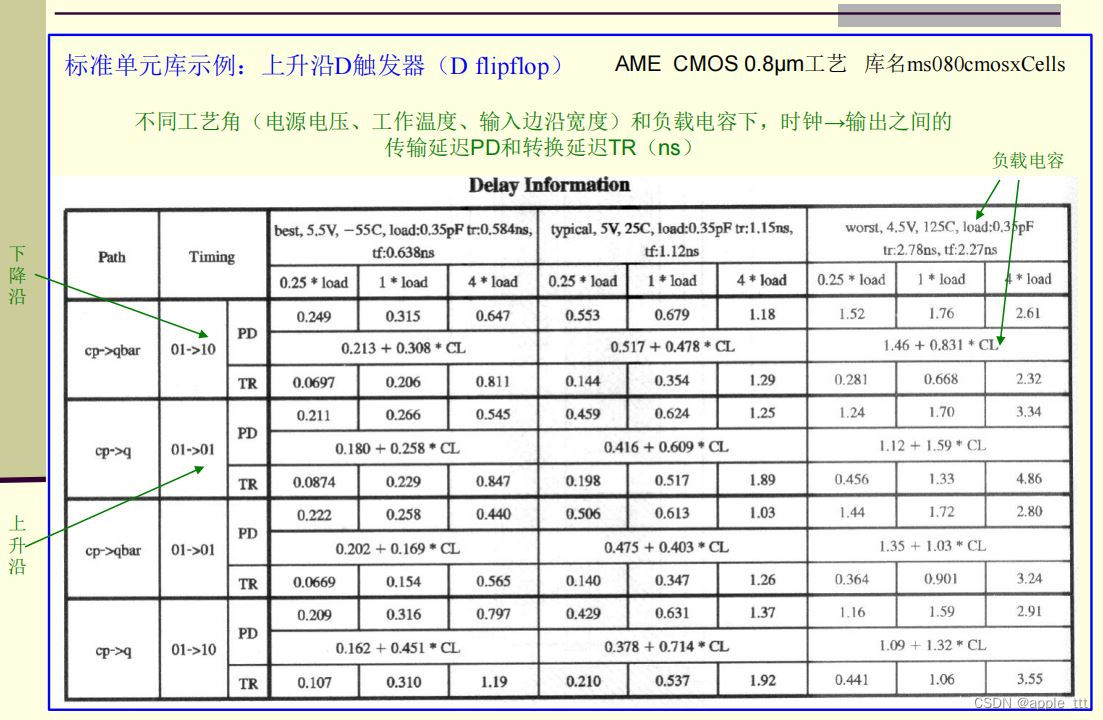

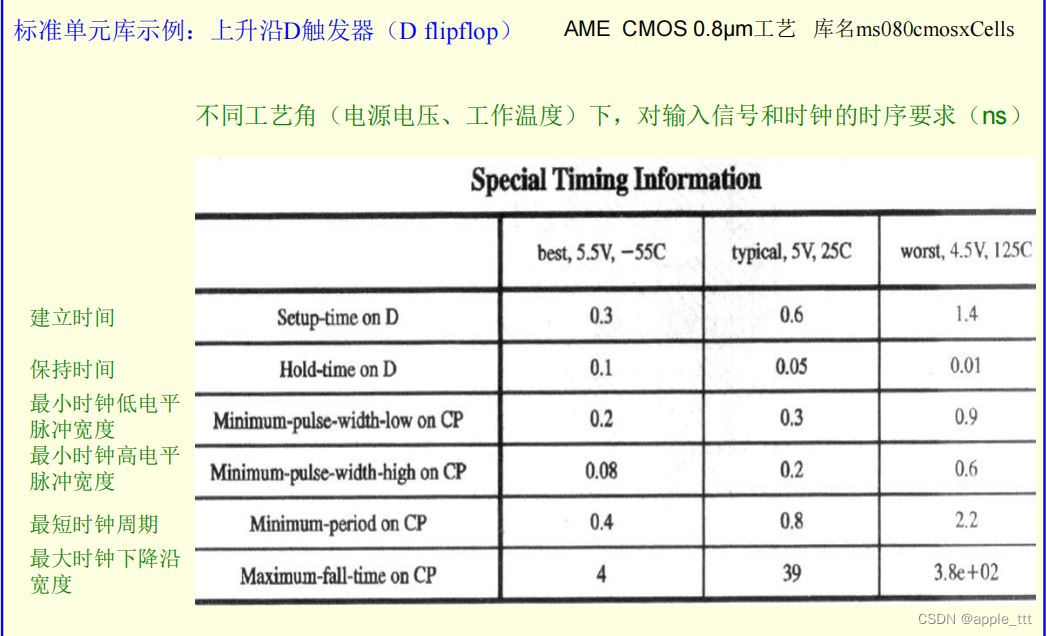

5.2 标准单元库示例:上升沿D触发器(D flipflop)

5.2.1 基本信息

????????AME CMOS 0.8μm工艺 库名ms080cmosxCells

5.2.2 延迟信息

5.2.3 对输入和时钟的要求

5.2.4 电路原理图?

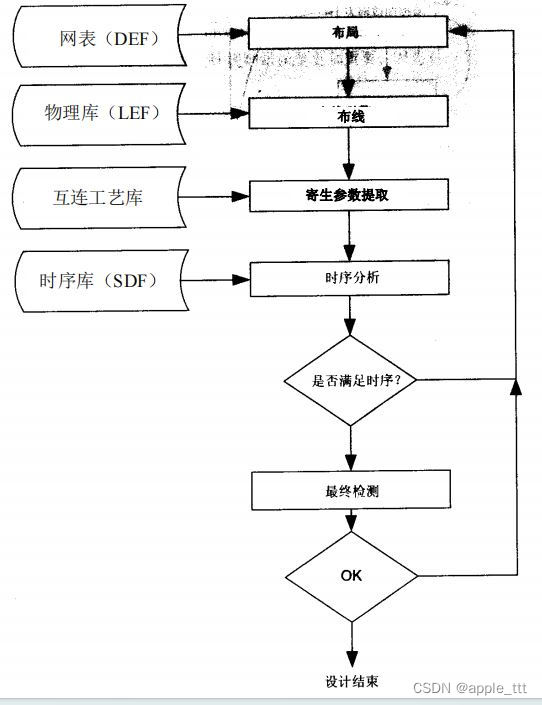

5.3 设计验证所需的库文件

- DEF(Design Exchange Format)文件:设计交换文件,给出被设计电路的网表,用于在不同设计系统之间传递电路设计信息,可用于参数提取、功耗分析、电压降分析等

- LEF(Library Exchange Format)文件:物理库文件,描述单元的物理拓扑信息以及对互连尺寸约束(端口位置、层定义和通孔定义等),以.lef为后缀,主要用于布局布线

- SDF(Standard Delay Format)文件 :时序库文件,描述单元及互连的时序信息,包括管脚与管脚之间、时钟与数据之间以及内部互连的延迟,以.lib为后缀,主要用于静态时序分析

? ? ? ? 这里拓展说一下时序库的内容:时序库文件SDF(Standard Delay Format):ASCII格式,存放由EDA工具生成的时延数据。

1、数据主要内容

- 电路时延(Circuit Delay):单元或器件的时延,有端口到端口(黑盒)和分布时延(白盒)两种建模方式

- 互连时延(Interconnect Delay):连线或互连网络的时延,有点到点的interconnect结构和将互连等效成单元的Port结构

?2、数据来源

- 正标(Forward-annotation):布局布线前,根据线负载模型以及用户的时间约束来定义延迟,通常用于逻辑综合和有时间驱动的布局布线

- 反标(Back-annotation):布局布线后,从实际提取的网表中计算得到的时延,包含了网络的电容和互连的RC时延,通常用于布局布线后的静态时序分析

?

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 栈(顺序存储、链式存储)

- linux shell脚本开发基础操作汇总

- JAVA:OFD Reader & Writer 开源库技术解析

- 手机之变@2023:高端化之“殇”、技术革新与新生机

- 【2024】基于springboot的原神游戏商城系统设计

- 【深度学习目标检测】八、基于yolov5的抽烟识别(python,深度学习)

- Java和Redis实现一个简单的热搜功能

- 【AI】YOLO学习笔记

- innovus:ccopt_design流程

- Broken pipe