verilog语法进阶-移位寄存器原语-单输入单输出

发布时间:2023年12月20日

概述

verilog c代码

module primitive1(

input clk , // system clock 50Mhz on board

input rst_n, // system rst, low active

input a ,

output y1, // output signal

output y // output signal

);

SRLC16_1 #(

.INIT(16'h0000) // Initial Value of Shift Register

) SRLC16_1_inst (

.Q(y), // SRL data output

.Q15(y1), // Carry output (connect to next SRL)

.A0(0), // Select[0] input

.A1(1), // Select[1] input

.A2(0), // Select[2] input

.A3(1), // Select[3] input

.CLK(clk), // Clock input

.D(a) // SRL data input

);

endmodule

原语代码

module primitive1 (

clk, rst_n, a, y, y1

);

input clk;

input rst_n;

input a;

output y;

output y1;

wire N0;

wire N1;

wire a_IBUF_3;

wire clk_BUFGP_5;

wire y1_OBUF_8;

wire y_OBUF_9;

GND XST_GND (

.G(N0)

);

VCC XST_VCC (

.P(N1)

);

SRLC16_1 #(

.INIT ( 16'h0000 ))

SRLC16_1_inst (

.A0(N0),

.A1(N1),

.A2(N0),

.A3(N1),

.CLK(clk_BUFGP_5),

.D(a_IBUF_3),

.Q(y_OBUF_9),

.Q15(y1_OBUF_8)

);

IBUF a_IBUF (

.I(a),

.O(a_IBUF_3)

);

OBUF y_OBUF (

.I(y_OBUF_9),

.O(y)

);

OBUF y1_OBUF (

.I(y1_OBUF_8),

.O(y1)

);

BUFGP clk_BUFGP (

.I(clk),

.O(clk_BUFGP_5)

);

endmodule

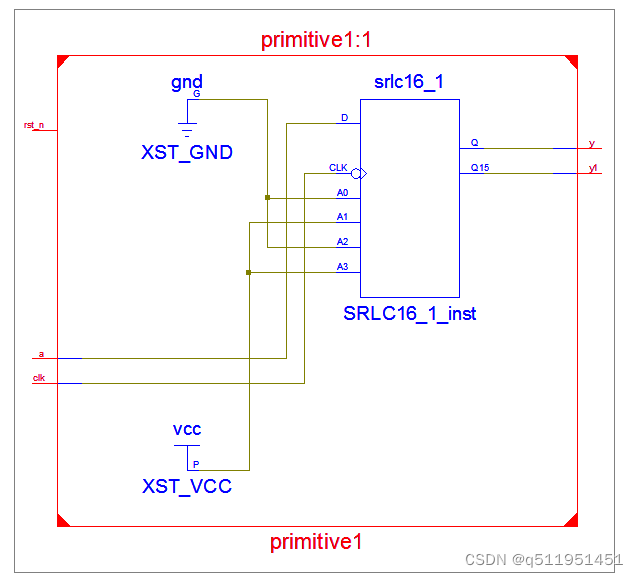

RTL结构图

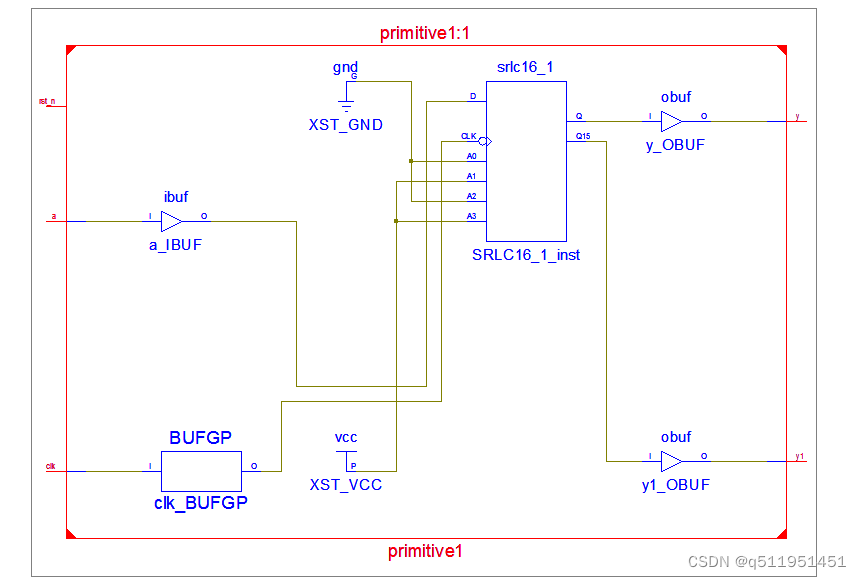

技术原理图

文章来源:https://blog.csdn.net/q511951451/article/details/135029906

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 【MySQL】事务

- Web server failed to start. Port 8080 was already in use. 端口被占用

- Express.js 中动态路由解码:path-to-regexp介绍

- 使用骨传导耳机对人体有没有伤害?一文读懂骨传导耳机有什么危害?

- 便捷记账软件,高效财务管理

- python解决android版数美滑块验证码,30分钟快速解决

- 【数据结构】在链队列中你可能忽视的二三事

- 云原生Kubernetes: Kubeadm部署K8S 1.29版本 单Master架构

- WPF入门到跪下 第十章 MVVM-基本数据处理

- 云服务器 nginx自启动、mysql自启动、pyhton后端自启动