CPU测试方案浅析

一、CPU概述

中央处理器(CPU)作为计算机系统的运算和控制核心,是信息处理、程序运行的最终执行单元。应用处理器SoC是在中央处理器的基础上扩展音视频功能和专用接口的超大规模集成电路,是智能设备的“大脑”,在智能设备中起着运算及调用其他各功能构件的作用。

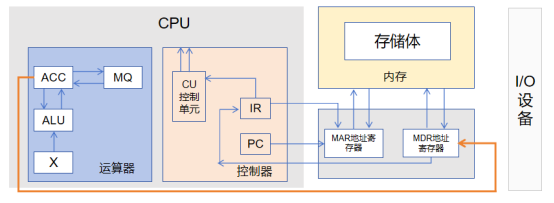

CPU内部主要由运算器、控制器、寄存器三大部分组成。运算器负责算术运算(+、-、*、/基本运算和附加运算)和逻辑运算(包括移位、逻辑测试或比较两个值等);控制器负责应对所有的信息情况,调度运算器把计算做好;寄存器它们可用来暂存指令、数据和地址。既要对接控制器的命令,传达命令给运算器;还要帮运算器记录处理完或者将要处理的数据。

二、CPU的生产测试流程

近年来,随着人工智能、大数据等新技术的快速发展,CPU的应用场景也越来越广泛。在服务器领域,大型数据中心和云计算都需要高效的CPU;在移动设备领域,智能手机和平板电脑更需要低功耗高效的处理器。随着物联网、5G等新技术的出现,CPU将在更多的领域发挥其作用。

CPU的未来发展趋势是多样化和高性能化。在多样化方面,CPU将更加智能化,支持更多的场景和应用,例如自然语言处理、图像识别等;在高性能化方面,CPU将继续研发更高的运算速率和更低的功耗,满足人们对计算能力的不断追求。同时,CPU的发展也将面临一些挑战,如热量问题、功耗过大等。因此,未来的CPU还需要更多的创新和技术突破。

CPU的制造过程需要经过多个步骤,通常包括以下几个阶段:

① 设计阶段

② 掩膜制造阶段

③ 制造晶圆阶段

④ 芯片切割和打磨阶段

⑤ 工艺加工阶段–流片前测试

⑥ 封装和测试阶段–流片后测试

三、CPU测试场景

从CPU的生产测试流程可以看出从宏观上看,CPU芯片主要分为流片前测试和流片后测试,而测试内容包括静态功耗、动态功耗、时钟速度、内存接口速度、热设计功率、可靠性等。

CPU流片前的芯片主要是在硬件仿真器上,模拟一个芯片工作的环境,把芯片的引脚都引出,检测芯片的功能,或者在各种严苛环境下看芯片能否正常工作,然后将FPGA板或者仿真器上的网口和测试仪器进行连接,通过测试仪模拟流量或者线速流量进行CPU功能和性能的验证。

CPU流片后封装好的芯片集成在PCIE板上,此时主要是测试CPU的整体工作环境–PCIE总线性能,同时也测试了外设设备的功能和性能,包括网卡、磁盘等。

四、如何使用测试仪进行CPU测试

那么,如何使用信而泰测试仪进行CPU测试呢,下面就进行简单地介绍(主要是二三层流量的转发测试),除了这些测试仪还可以自定义报文,导入现网报文进行模拟测试等。

测试拓扑:

二层转发性能测试

(1)打开Renix测试软件,并预约测试端口(根据实际端口需求进行选择)

注:如果只是测试单端口转发性能,只需要连接两个端口即可,如果需要进行压力测试,那么可以根据性能连接尽可能多的端口进行全连接打流测试;

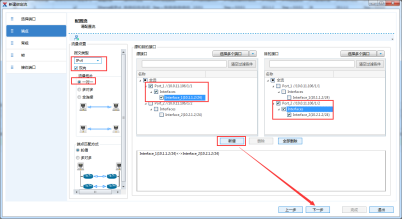

(2)配置流量模型,如果只连接了两个端口,那么选择两个端口互相发送流量,也就是测试两个端口的转发性能,如果是连接了多个端口,也可以多个端口全连接打流,进行压力测试;

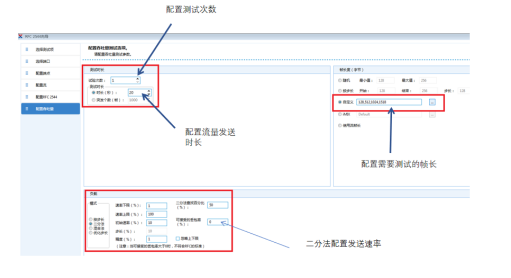

(3)配置吞吐量测试参数,可以根据实际需要测试,建议测试帧长为64,128,256,512,1024,1280,1518等7个字节,测试次数可以选择3-5次,取多次测试的平均值;

(4)启动RFC2544测试,待测试完成后查看测试结果即可,吞吐量需要看不丢包情况下的最大转发速率。

三层转发性能测试(可能需要添加TCP或者UDP头部)

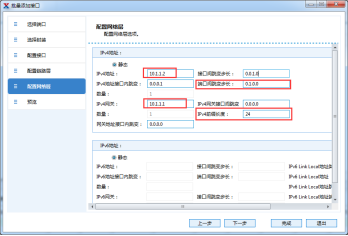

(1)先配置接口,选择实际连接的端口下配置接口,配置接口的时候mac不能冲突,IP根据实际需求进行配置,网关一般是设备上直接和测试仪端口连接的那个口的IP;

(2)配置绑定流–选择源目接口,也就是对应的IP之间进行打流,在配置的时候可以选择是否添加UDP或者TCP包头,也可以配置对应的帧长,载荷参数等;

(3)按照需求配置完成后,配置最大的发送速率,启动测试仪的流量发送即可。

自定义报文测试

(1)可以通过测试仪端口模拟特定的流量发送到被测系统,查看系统的处理是否正确

(2)在测试仪上创建流模板,添加Custom包头,需要添加的内容可以自行定义

(3)可以将现网抓取的报文直接导入测试仪生成流模板,然后发送流量

五、BigTao-V系列测试仪

信而泰推出的BigTao硬件测试平台,信而泰BigTao-V系列网络测试仪是拥有信而泰全球领先架构的面向中低端路由器、交换机及同级别网络转发设备的研发类测试产品。它采用模块 化设计,由机箱、板卡和软件三部分组成。 该系列网络测试仪可提供2个或6个插槽,支持从10M到400G多种速率的测试模块任意组合,为CPU产品研发测试保驾护航。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 大数据与深度挖掘:如何在数字营销中与研究互动

- Python中选择排序和冒泡排序的区别

- 深入理解 Golang 中 Channel 的用法:从简单到复杂

- 【中位数问题】两个已升序数组确定其中位数

- 写一个文字滑动切换样式效果

- 梅溪湖街道房屋在线租赁管理系统的设计与实现(源码+开题)

- Python 常见的 10 个错误及其解决方法

- 全国职业技能大赛高职组(最新职业院校技能大赛_大数据应用开发样题解析-模块C:实时数据处理-任务二:实时指标计算)

- 51单片机三种编译模式的相互关系

- [足式机器人]Part2 Dr. CAN学习笔记-Advanced控制理论 Ch04-3Phase Portrait相图,相轨迹