Placement 提要总结

Standard cell相关信息

1、时序库lib(liberty library format)

lib用于描述物理单元的时序和功耗信息的重要库文件,包含物理单元库的基本属性和每个单元的具体时序信息。

物理单元库的基本属性:单元库名称、文件版本、产生日期及PVT环境等;定义电压、电流、电容、时间等基本单元;定义电路传输时间和信号转换时间的电压百分比。

每个单元的具体时序信息:包含单元的延迟时间、泄漏功耗,内部功耗等。包括每个单元的Timing、Power、Area、Direction、function、Noise、Pin capacitance、DRV(max trans/max capacitance)等。

2、物理库lef(design exchange format)

technology LEF:包含布局布线规则和晶圆厂的工艺信息。

Cell LEF:用于定义标准单元、模块单元、IO单元和各种特殊单元的物理信息。包括cell size、site、pin layer/direction/location/type、pg layer 等。

3、lib & lef

lib文件描述的单元信息与物理库的单元一一对应。

主要内容

摆放standard cell,place_opt_design,需要在满足时序要求的同时,尽量减小面积和功耗,实现时序优化,面积优化,功耗优化。

- 关键单元应该摆放在核心区域;

- 标准单元必须摆对正确位置;

- 没有overlap,cell摆放基于正确的site;

- 没有违反floorplan constraint(fence、region、guide);

- 没有违反place constraint(cell padding、edge constraint)。

如何执行place

输入命令“place_opt_design”,工具会自动将std cell摆放进die box空余位置。Place_opt_design其实是两个command合在一起。 虽然写入的只有一句命令,但是实际工具在做的时候,是集成了placedesign和optdesign以实现更快的运行时间和更好的PPA。

1、glogal place(placedesign)

只是单纯把std cell 摆进了die box里,并没有摆到相关的逻辑旁边,会有overlap,方向错误等问题。

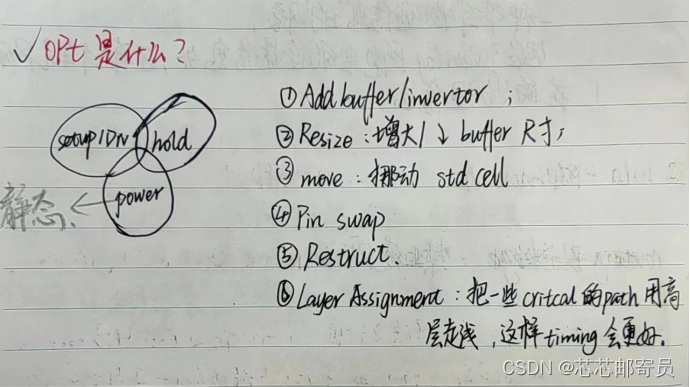

2、opt design

把global place里面非合法的std cell,做opt之前,要先做refine place、Legalize placement,合法化。

再去做opt优化。

Place and opt

1、check initial timing

检查DC出来的网表的timing情况,为后边的timing opt提供优化方向。如果DC出来的时序很差,PR也很难做好。

2、Area opt

面积优化时,如果X4和X2的单元同样可以驱动目标单元,则会优先使用X2驱动单元以减小面积。

3、Drv opt

DRV包括:transition、max?fanout、noise、max capacitance。工具会在不影响timing的情况下进行Drv的优化。值得一提的是做STA时,先修DRC,再去修setup,再做recovery,修hold,这时的DRC称为DRV。

4、Timing opt

area可以修的不是那么好,transition也可以相对比较大,但是timing一定要好。其他地方可以trade off,但是timing一定要好。

5、Congestion opt

对于设计中部分区域的congestion比较大的问题,工具会将绕不通的几条线往其他的区域绕,从而优化congestion。

6、Power consumption opt

VT swap:LVT低阈值,漏电流较大,但是延迟较小;SVT标准阈值居于两者中间;HVT高阈值,漏电流小,但是延迟大。在关键路径上最好用LVT的库,考虑到降低功耗,最好用HVT的库。

Down size:在保证timing的情况下,大驱动换小驱动,较少功耗损失。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 成倍提高生产力工具Notion

- springboot进行Swagger配置

- 标签蛋白纯化|蛋白纯化-卡梅德生物

- 【【ZYNQ基础模块串口的意义】】

- Java 异常及处理|Error、Throwable、Exception

- SkyWalking相关问题及答案(2024)

- 企业账号基础知识

- Python将Labelme文件的真实框和预测框绘制到图片上

- MySQL 8.0中引入的选项和变量(七)

- 如何在Nginx服务器上安装阿里云ssl证书