计算机组成原理 指令

指令

指令格式和分类

指令格式

相关概念

Ad(Address) 形式地址

AC(Accumulation register)累加寄存器

ALU(Arithmetic logic unit)算术逻辑单元

MQ(Multiplier-Quotient Register)乘商寄存器

DR(Data Register) 数据寄存器

AR(Address Register) 地址寄存器(MAR)

IR(Instruction Register) 指令寄存器

BR(Buffer Register) 缓冲寄存器(MBR)

ID(Instruction Decoder) 指令译码器

PC(ProgramCounter) 程序计数器

OP(Operate Code): 操作码 指令中用于指出操作性质的字段。

了解指令

指令系统

每种计算机系统均有一组指令提供给用户使用

指令

般由操作码和地址码两部分构成,其中操作码在前,地址码在后,地址码的个数可变

|操作码OP| 地址码|

操作码是指明指令操作性质的命令码,它提供指令的操作控制信息,不可缺少

操作数地址码用来描述该指令的操作对象及其所在位置

|OP|4|A2|A3(结果)|A4(下地址)|

指令含义:$ (A_1) OP (A_2) ->A_3,A_4=$下一条将要执行指令的地址

指令执行

| 00000000 | 000001 | 000010 | 000011 | 000100 |

|---|---|---|---|---|

| OP | A 1 A_1 A1? | A 2 A_2 A2? | A 3 A_3 A3?(结果) | A 4 A_4 A4?(下地址) |

一条指令的执行 (假设每个地址都是主存地址)

取指令访存1次 (假设指令字长=存储字长)

取两个操作数访存2次

存回结果访存1次

共访存4次

取指

PC(程序计数器)=0 ? 指向第一条指令的位置,PC存放了当前欲执行指令的位置。

MAR(地址寄存器)=0 ? PC把地址0交给了地址寄存器MAR

MDR(数据寄存器)=000001 0000001000 ? MAR根据地址在0的存储单元中取出指令,交给了数据寄存器MDR

IR(指令寄存器)=000001 0000001000 ? MDR将指令交给了指令寄存器IR

分析

OP(IR)=000001 ? 获取指令操作码

PC=PC+1 ? 地址为0的存储单元中的指令执行结束,程序计数器PC自动+1

执行

MAR=Ad(IR)=0000001000 ? 获取数据地址

MDR=X ? 从MAR获取真实数据的值

ACC=MDR=x ? MDR将数据放入累加器ACC中

取指

PC=1

MAR=1

MDR=000100 0000001001

IR=000100 0000001001

分析

OP(IR)=000100

PC=PC+1

执行

MAR=Ad(IR)=0000001001

MDR=a

MO=MDR=a 从MDR读取数据放入乘商寄存器MO

X=ACC=x 把ACC中的值放入通用寄存器X

ACC=ax

按地址码分类

四地址指令

|OP|

A

1

A_1

A1?|

A

2

A_2

A2?|

A

3

A_3

A3?(结果)|

A

4

A_4

A4?(下地址)|

指令含义:

(

A

1

)

O

P

(

A

2

)

?

>

A

3

,

A

4

=

(A_1)OP (A_2) ->A_3,A_4=

(A1?)OP(A2?)?>A3?,A4?=,下一条将要执行指令的地址,完成一条指令访存4次

三地址指令

|OP|

A

1

A_1

A1?|

A

2

A_2

A2?|

A

3

A_3

A3?(结果)|

指令含义 :

(

A

1

)

O

P

(

A

2

)

?

>

A

3

(A_1)OP (A_2) ->A_3

(A1?)OP(A2?)?>A3?完成一条指令访存4次。区别在于地址码位数不同

二地址指令

|OP|

A

1

A_1

A1?|

A

2

A_2

A2?|

指令含义:

(

A

1

)

O

P

(

A

2

)

?

>

A

1

(A_1)OP (A_2)->A_1

(A1?)OP(A2?)?>A1?完成一条指令访存4次

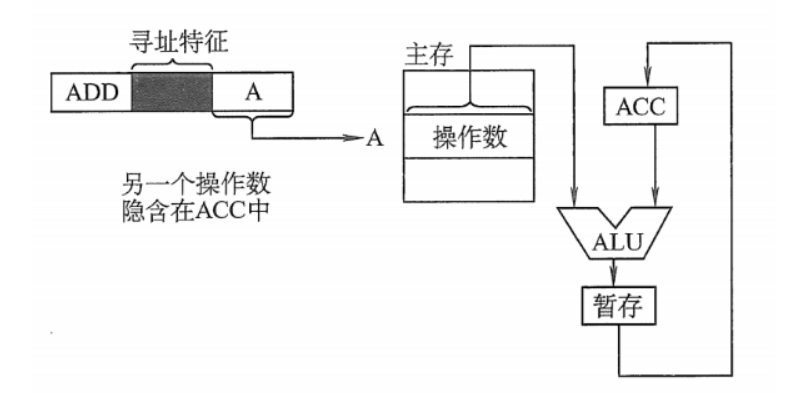

一地址指令

指令含义 :

(

A

1

)

O

P

(

A

2

)

?

>

A

1

(A_1)OP (A_2)->A_1

(A1?)OP(A2?)?>A1?,完成一条指令访存3次。

(

A

C

C

)

O

P

(

A

1

)

?

>

A

C

C

(ACC) OP (A_1)->ACC

(ACC)OP(A1?)?>ACC,约定目的地址为ACC,完成一条指令访存2次

零地址指令

- 不需要操作数的指令,如空操作指令、停机指令、关中断指令等

- 零地址的运算类指令仅用在堆栈计算机中。

通常参与运算的两个操作数隐含地从栈顶和次栈顶弹出,送到运算器进行运算,运算结果再隐含地压入堆栈

按操作码分类

定长指令字结构

指令字长固定的指令

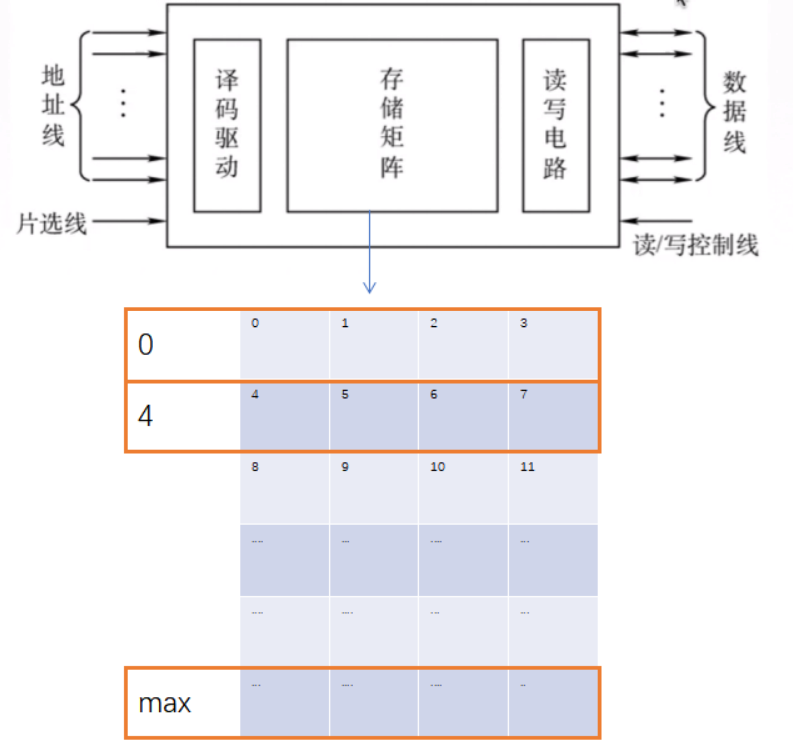

59.png?origin_url=image-74.png&pos_id=img-fBitwosy-1704330847076)

变长指令字结构

指令字长不固定的指令

列题

假设指令字长为16位:前4位为基本操作码字段OP

4位基本操作码若全部用于三地址指令,则有16条

但至少须将1111留作扩展操作码之用,即三地址指令为15条

111111留作扩展操作码之用,二地址指令为15条

111111111111留作扩展操作码之用,一地址指令为15条

零地址指令为16条

列题

设指令字长固定为16位,试设计一套指令系统满足:

a有15条三地址指令

b有12条二地址指令

c有62条一地址指令

d有32条零地址指令

设地址长度为n,上一层留出m种状态,下一层可扩展出

m

?

2

n

m*2^n

m?2n种状态

| 有15条三地址指令 | 0000-1110 | A 1 A_1 A1? | A 2 A_2 A2? | A 3 A_3 A3? |

| 有12条二地址指令 | 1111 | 0000-1011 | A 2 A_2 A2? | A 3 A_3 A3? |

| 有62条一地址指令 | 1111 | 1100-1111 | 0000-1101 | $A_3 |

| 有32条零地址指令 | 1111 | 1100-1111 | 1110-1111 | 0000-1111 |

按长度分类

单字长指令: 指令长度=机器字长

半字长指令、双字长指令

按操作类型分类

数据传送类

数据传送目的

- LOAD 作用:把存储器中的数据放到寄存器中

- STORE 作用: 把寄存器中的数据放到存储器中

运算类

算术逻辑操作 - 算术:加、减、乘、除、增1、减1、求补、浮点运算、十进制运算

- 逻辑: 与、或、非、异或、位操作、位测试、位清除、位求反

移位操作

算术移位、逻辑移位、循环移位 (带进位和不带进位)

程序控制类

转移操作

- 无条件转移 :JMP

- 条件转移:

- JZ:结果为0

- JO:结果溢出

- JC:结果有进位

- 调用和返回CALL和RETURN

- 陷阱(Trap)

输入输出操作

CPU寄存器与IO端口之间的数据传送 (端口即IO接口中的寄存器)

寻址方式

指令寻址

指令寻址

找到下一条欲执行指令的指令地址

顺序寻址: (PC)+1

PC ? 当前地址 —> 地址+1

| 000010 | 000011 | 000100 | |

|---|---|---|---|

| OP | A 1 A_1 A1? | A 2 A_2 A2? | A 3 A_3 A3?(结果) |

跳跃寻址: (PC)+A

| 00000000 | 000010 | 000011 | 000100 |

|---|---|---|---|

| OP | A 1 A_1 A1? | A 2 A_2 A2? | A 3 A_3 A3?(结果) |

数据寻址

数据寻址

找到本条指令的操作数地址

寻址特征

表明某种数据寻址方式

| 寻址方式 | EA | |

|---|---|---|

| 操作码(OP) | 寻址特征 | 形式地址(A) |

| 寻址方式 | EA1 | 寻址方式 | EA2 | |

|---|---|---|---|---|

| 操作码(OP) | 寻址特征 | 形式地址(A1) | 寻址特征 | 形式地址(A2) |

隐含寻址

不是显式的给出操作数的地址,而是在指令中隐含着操作数的地址

| 寻址方式 | EA1 | |

|---|---|---|

| OP | A |

优点:指令执行阶段不访问主存,指令执行时间最短

缺点: A的位数限制了立即数的范围

立即数寻址

形式地址A就是操作数本身,又称为立即数,一般采用补码形式

| 寻址方式 | EA1 | |

|---|---|---|

| OP | # | A |

CPU执行:

- 取指令访存1次

- 执行指令访存0次

- 不考虑存放结果

- 共访存1次

优点: 指令执行阶段不访问主存,指令执行时间最短

缺点: A的位数限制了立即数的范围

直接寻址

形式地址A就是操作数的真实地址,即EA1=A

| 寻址方式 | EA1 | |

|---|---|---|

| OP | 看情况 | A |

CPU执行:

- 取指令访存1次

- 执行指令访存1次

- 不考虑存放结果

- 共访存2次

优点:简单,指令执行阶段仅仅访问一次主存,不需要设计专门计算操作数的地址

缺点: A的位数限制了寻址的范围,而且操作数的地址不容易更改

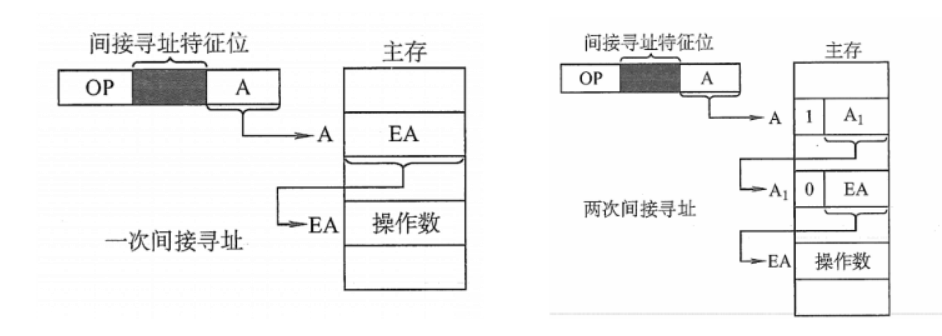

间接寻址

指令的地址字段给出的形式地址不是操作数的真正地址,而是操作数有效地址所在的存储单元的地址,也就是操作数地址的地址,即EA1=(A)

| 寻址方式 | EA1 | |

|---|---|---|

| OP | 看情况 | A |

CPU执行:

- 取指令访存1次

- 执行指令访存2次

- 不考虑存放结果

- 共访存3次

优点: 可以扩大寻址范围,便于编制程序

缺点:指令在执行阶段要多次访存,多次访存的寻址需根据存储字的做高位确定

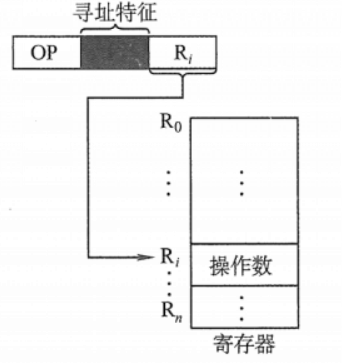

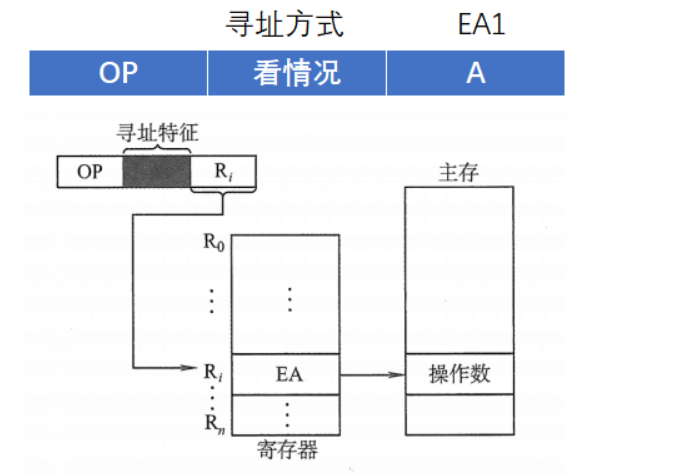

寄存器寻址

在指令字中直接给出操作数所在的寄存器编号,即EA =Ri其操作数在由Ri所指的寄存器内。

| 寻址方式 | EA1 | |

|---|---|---|

| OP | 看情况 | A |

CPU执行:

- 取指令访存1次

- 执行指令访存o次

- 不考虑存放结果

- 共访存1次

优点:指令在执行阶段不访问主存,只访问寄存器,指令字短且执行速度快

缺点: 寄存器价格昂贵,计算机中寄存器个数有限

寄存器间接寻址

寄存器Ri中给出的不是一个操作数,而是操作数所在主存单元的地址,即EA=(Ri)。

| 寻址方式 | EA1 | |

|---|---|---|

| OP | 看情况 | A |

CPU执行:

- 取指令访存1次

- 执行指令访存1次

- 不考虑存放结果

- 共访存2次

优点: 比一般的间接寻址快很多

缺点: 寄存器价格昂贵,而且在执行阶段需要访问主存

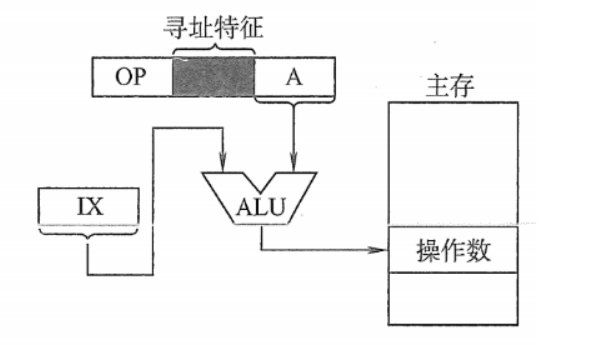

变址寻址

有效地址EA等于指令字中的形式地址A与变址寄存器IX的内容相加之和,

即EA=(IX)+A,其中IX为变址寄存器(专用),也可用通用寄存器作为变址寄存器

| 寻址方式 | EA1 | |

|---|---|---|

| OP | 看情况 | A |

CPU执行:

- 取指令访存1次

- 执行指令访存1次

- 不考虑存放结果

- 共访存2次

优点:可以扩大寻址范围;在数组处理方面,可以设A为数组的首地址,不断改变IX,所以十分适合编制循环程序

缺点:寄存器价格昂贵,逻辑比较复杂

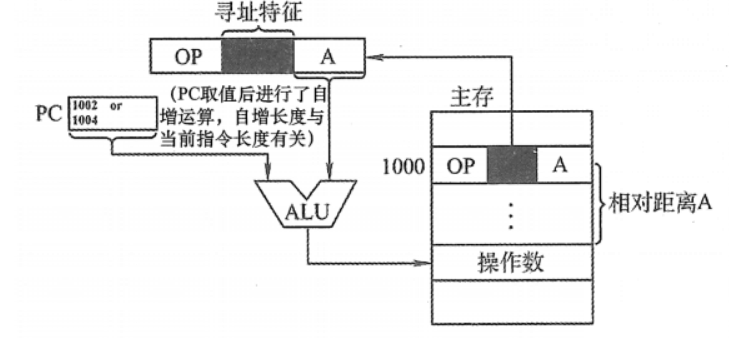

相对寻址

把程序计数器PC的内容加上指令格式中的形式地址A而形成操作数的有效地址,即EA=(PC)+A,其中A是相对于当前指令地址的位移量,可正可负,补码表示。

| 寻址方式 | EA1 | |

|---|---|---|

| OP | 看情况 | A |

CPU执行:

- 取指令访存1次

- 执行指令访存1次

- 不考虑存放结果

- 共访存2次

优点: 操作数的地址不是固定的,随着PC的变化而变化,并且与指令地址之间总是相差一个固定值,因此便于程序浮动,广泛用于转移指令

缺点: 寄存器价格昂贵,逻辑比较复杂

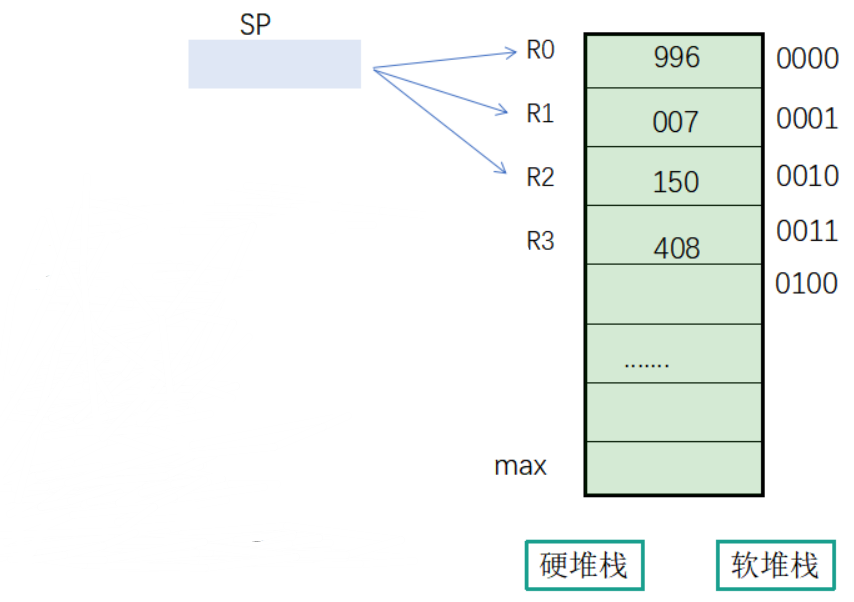

堆栈寻址

存储区中被读/写单元的地址是用一个特定的寄存器给出的,该寄存器称为堆栈指针 (SP)

| 寻址方式 | EA1 | |

|---|---|---|

| OP | 看情况 | A |

完成一次加法: 记栈顶单元Msp

(Msp)–>ACC ? 数据移入累加寄存器ACC

(SP)+1–>SP ? 栈指针加一

(Msp)–>X ? 数据移入通用寄存器

(SP)+1–>SP ? 栈指针加一

(ACC)+(X)–>T

(SP)-1=>SP(Y)–>Msp ? 回到栈顶

CPU执行:

- 取指令访存1次

- 软堆栈执行指令访存

- 不考虑存放结果

偏移寻址

变址寻址

基址寻址

相对寻址

总结

| 寻址方式 | 有效地址 | 访存次数(不考虑存放结果) |

|---|---|---|

| 隐含寻址 | 程序指定 | 2 |

| 立即数寻址 | A是操作数 | 1 |

| 直接寻址 | EA=A | 2 |

| 一次间接寻址 | EA=(A) | 3 |

| 寄存器寻址 | EA=Ri | 1 |

| 寄存器间接一次寻址 | EA=(Ri) | 2 |

| 相对寻址(爱情转移) | EA=(PC)+A | 2 |

| 基址寻址(K歌之王) | EA=(BR)+A | 2 |

| 变址寻址(十年) | EA=(IX)+A | 2 |

| 堆栈寻址 | 根据情况决定 | 硬堆栈不访存/软堆栈访存 |

指令集

RISC和CISC的特点| CISC | RISC |

|---|---|

| 指令就是程序 | 指令是一个动作 |

| X86架构 | ARM架构 |

| 指令使用不均匀 | 只保留基本指令 |

| 实例: 设计一副扑克牌 | |

| 52张扑克牌就要有52个电路设计,但是这种设计是比较通用的。 | 13张不同的数字(A~K)4和花色设计17种电路,然后多条指令组合 |

RISC和CISC的对比

| 类别 | CISC | RISC |

|---|---|---|

| 指令系统 | 复杂,庞大 | 简单,精简 |

| 指令数目 | 一般大于200条 | 一般小于100条 |

| 指令字长 | 不固定 | 定长 |

| 可访存指令 | 不加限制 | 只有Load/Store指令 |

| 各种指令执行时间 | 相差较大 | 绝大多数在一个周期内完成 |

| 各种指令使用频度 | 相差很大 | 都比较常用 |

| 通用寄存器数量 | 较少 | 采用优化的编译程序,生的目标代码程序成的代码较为高效 |

| 目标代码 | 难以用优化编译生成高效 | |

| 控制方式 | 绝大多数为微程序控制 | 绝大多数为组合逻辑控制 |

| 指令流水线 | 可以通过一定方式实现 | 必须实现 |

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 数位排序(第十三届蓝桥杯pythonB组)

- UE虚幻引擎项目更改名字怎么操作?

- 想要学习大语言模型?这些开源模型带你轻松入门!(附论文和代码)

- 小米造车1000天,只有「性价比」是大家的期待吗?

- 低压系统母线为什么必须装设弧光保护

- 跨境电商的语言障碍:翻译工具的必要性

- 对象合并(相同的相加,不同的创建)

- 类中,构造方法、普通方法、类方法、静态方法和魔术方法的区别

- c++动态内存

- Android 车联网——CarPowerManagementService介绍(七)