FIFO IP核使用

发布时间:2023年12月30日

目录

FIFO IP核使用

FIFO简介

FIFO 的英文全称是 First In First Out, 即先进先出。与 FPGA 内部的 RAM 和 ROM 的区别是没有外部读写地址线, 采取顺序写入数据, 顺序读出数据的方式,使用起来简单方便,缺点就是不能像 RAM 和 ROM 那样可以由地址线决定读取或写入某个指定的地址。

根据 FIFO 工作的时钟域,可以将 FIFO 分为同步 FIFO 和异步 FIFO:

同步 FIFO 是指读时钟和写时钟为同一个时钟,在时钟沿来临时同时发生读写操作

异步 FIFO 是指读写时钟不一致,读写时钟是互相独立的,一般用于跨时钟域数据传输

FIFO常用参数

- 将空标志(almost_empty),FIFO 即将被读空

- 空标志(empty),FIFO 已空时由 FIFO 的状态电路送出的一个信号,以阻止 FIFO 的读操作继续从 FIFO中读出数据而造成无效数据的读出

- 将满标志(almost_full),FIFO 即将被写满

- 满标志(full),FIFO 已满时由 FIFO 的状态电路送出的一个号,以阻止 FIFO 的写操作继续向 FIFO 中写数据而造成溢出

- 读时钟,读 FIFO 时所遵循的时钟,在每个时钟的上升沿触发

- 写时钟,写 FIFO 时所遵循的时钟,在每个时钟的上升沿触发

Basic

- Native(常规接口)

- 时钟分别是一般时钟(common)和独立时钟(independent)

Native FIFO

- Read Mode 有两种类型可选,Standard FIFO 是在给了读数据使能后,数据才出来,而 First Word Fall Through 模式是,当前数据提前已经到数据读数据线上,在读使能到来后,下一个数据会到数据线上。

- FIFO 的宽度,FIFO 一次读写操作的数据位 N

- FIFO 的深度,FIFO 可以存储多少个宽度为 N 位的数据

- Reset Pin:这里可以保持默认的勾选复位管脚、复位同步和使能 Safety Circuit,这里的复位是对数据输出以及内部读写指针计数等进行复位,复位后,读写指针清零。这里的复位同步功能是对异步输入的复位信号分别在读写时钟域内先进行同步后再进行读写的各自复位。使用 Safety Circuit 可以认为是一种更加可靠模式,内部通过额外的逻辑电路让 FIFO 复位的更加可靠

- 勾选 Reset Pin 后 fifo 模块的管脚会多出 wr_rst_busy 和 rd_rst_busy 两个信号输出,这两个信号分别表示的是写/读时钟域复位忙信号(为 1 表示忙,处于复位中,为 0表示复位完),所以每次给一个异步复位信号对 FIFO 进行复位时,需要等到 wr_rst_busy 从 1 变为 0 后才能对 FIFO 进行写数据操作(在 FIFO 非满情况下,这个是任何写操作时候都需要满足的),在 wr_rst_busy 为 1 时进行读是不允许的;同样的要等到 rd_rst_busy 从 1 变为 0 后才能对 FIFO 进行读操作,在 rd_rst_busy 为 1 时进行读是不允许的。

- 勾选 Reset Pin 后 fifo 模块的管脚会多出 wr_rst_busy 和 rd_rst_busy 两个信号输出,这两个信号分别表示的是写/读时钟域复位忙信号(为 1 表示忙,处于复位中,为 0表示复位完),所以每次给一个异步复位信号对 FIFO 进行复位时,需要等到 wr_rst_busy 从 1 变为 0 后才能对 FIFO 进行写数据操作(在 FIFO 非满情况下,这个是任何写操作时候都需要满足的),在 wr_rst_busy 为 1 时进行读是不允许的;同样的要等到 rd_rst_busy 从 1 变为 0 后才能对 FIFO 进行读操作,在 rd_rst_busy 为 1 时进行读是不允许的。

- 异步复位或同步复位

- 高电平复位或低电平复位

Data Counts

Write Data Count表示FIFO已经写入多少数据

Read Data Count表示FIFO中有多少数据可以读

Status Flags

未使用

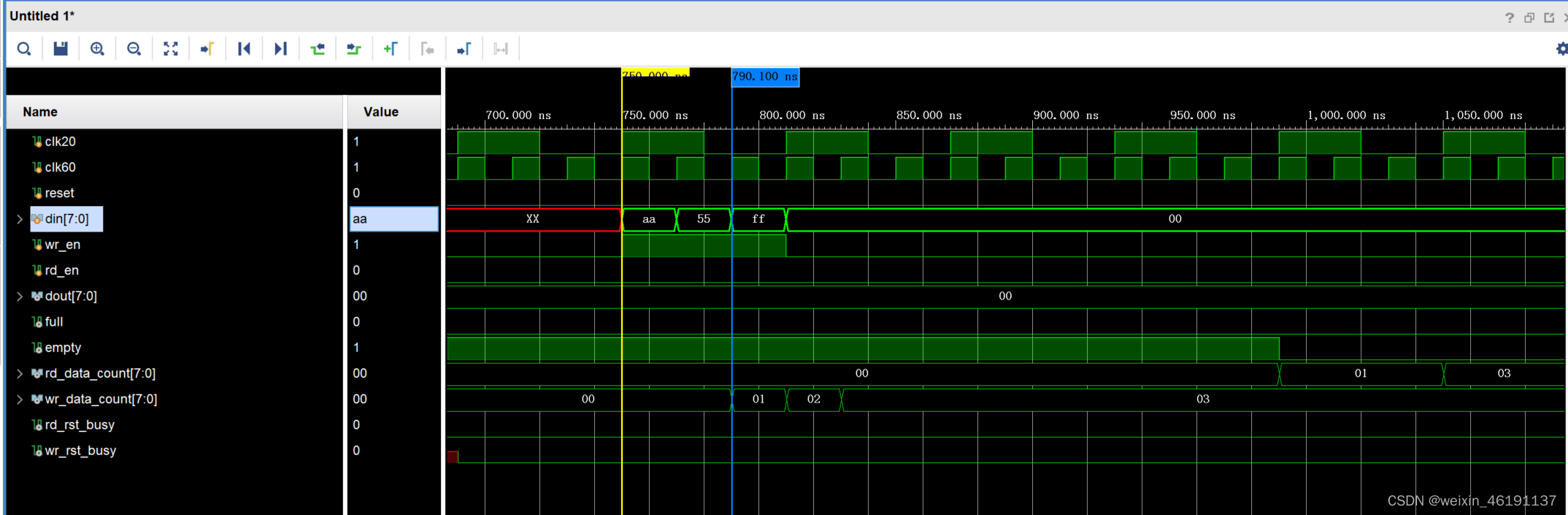

仿真

复位特性

写特性

读特性

标准模式

读使能有效后,延迟一周期才能读出数据

First Word Fall Through 模式

读使能有效时立刻就能独读出数据

参考资料

[1] IP核的使用之FIFO

[2] Vivado FIFO IP核使用教程

[3] FIFO IP核应用教程

文章来源:https://blog.csdn.net/weixin_46191137/article/details/135180772

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 系列十五、Redis面试题集锦

- RIS 系列 Beyond One-to-One: Rethinking the Referring Image Segmentation 论文阅读笔记

- uni-app 饼状图

- 饥荒Mod 开发(十七):手动保存和加载,无限重生

- go 语言中 json.Unmarshal([]byte(jsonbuff), &j) 字节切片得使用场景

- 初识大数据应用,一文掌握大数据知识文集(1)

- Linux5.2、进程等待

- zookeeper之集群搭建

- Chrome 浏览器插件 cookies API 解析

- EnlightenGAN论文阅读笔记