ZYNQ 7020 PL feature 解读

1. 组成

CLB, RAM, DSP, IO block,XADC, PCI-E, etc

2. CLK

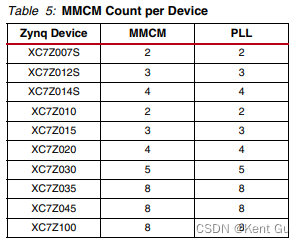

Each device in the Zynq-7000 family has up to 8 clock management tiles (CMTs), each consisting of one mixed-mode clock manager (MMCM) and one phase-locked loop (PLL). See Table 5.

2.1,?Clock Distribution

Each device in the Zynq-7000 family provides six different types of clock lines (BUFG-global, BUFR-regionn, BUFIO, BUFH, BUFMR, and the high-performance clock) to address the different clocking requirements of high fanout, short propagation delay, and extremely low skew.

2.2,Global Clock Lines,

In each device, 32 global clock lines have the highest fanout and can reach every flip-flop clock, clock enable, and set/reset as well as many logic inputs. There are 12 global clock lines within any clock region driven by the horizontal clock buffers (BUFH). Each BUFH can be independently enabled/disabled, allowing for clocks to be turned off within a region, thereby offering fine-grain control over which clock regions consume power. Global clock lines can be driven by global clock buffers, which can also perform glitchless clock multiplexing and clock enable functions. Global clocks are often driven from the CMT, which can completely eliminate the basic clock distribution delay.

2.3,Regional Clocks,

Regional clocks can drive all clock destinations in their region. A region is defined as any area that is 50 I/O and 50 CLB high and half the device wide. Each device in the Zynq-7000 family has between four and fourteen regions. There are four regional clock tracks in every region. Each regional clock buffer can be driven from either of four clock-capable input pins, and its frequency can optionally be divided by any integer from 1 to 8.

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- LinkedList元素使用Lanbda表达式循环打印

- 树状结构的tree

- 鸿蒙(HarmonyOS)项目方舟框架(ArkUI)之线性布局容器Row组件

- Broadcom交换芯片56620架构

- 基于ssm框架的博客系统

- Nat Med | 高效的体内基因编辑可预防小鼠肥厚型心肌病

- shell编程

- 鸿蒙(HarmonyOS 3.1) DevEco Studio 3.1开发环境汉化

- HarmonyOS 应用开发学习笔记 状态管理概述

- DataProcess-VOC数据图像和标签一起进行Resize