数字逻辑期末复习【个人期末复盘】【有不足之处欢迎斧正】

1.组合逻辑电路分析

分析电路功能时,需要先列出电路的真值表,然后分析电路的真值表(例如功能为同或)

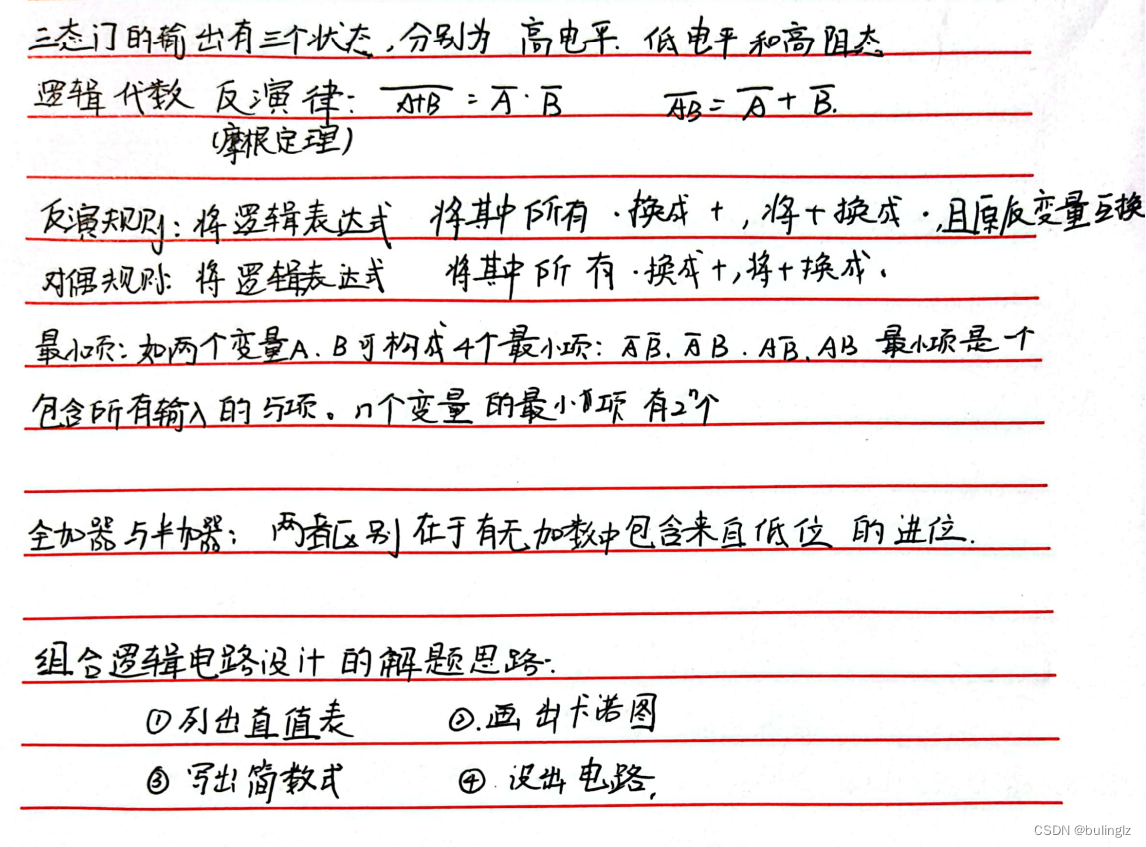

全加器与半加器的区别在于有无低位进位作为加数

找逻辑表达式可以使用卡诺图,划卡诺圈

如果题目要求设计一个逻辑电路,先写出真值表对应的卡诺图,然后圈出对应的卡诺圈。利用题目要求的实现方式来实现逻辑电路的设计。从输出依次得到输出

题目中的低位和高位需要注意,严格遵守题目的高低位顺序

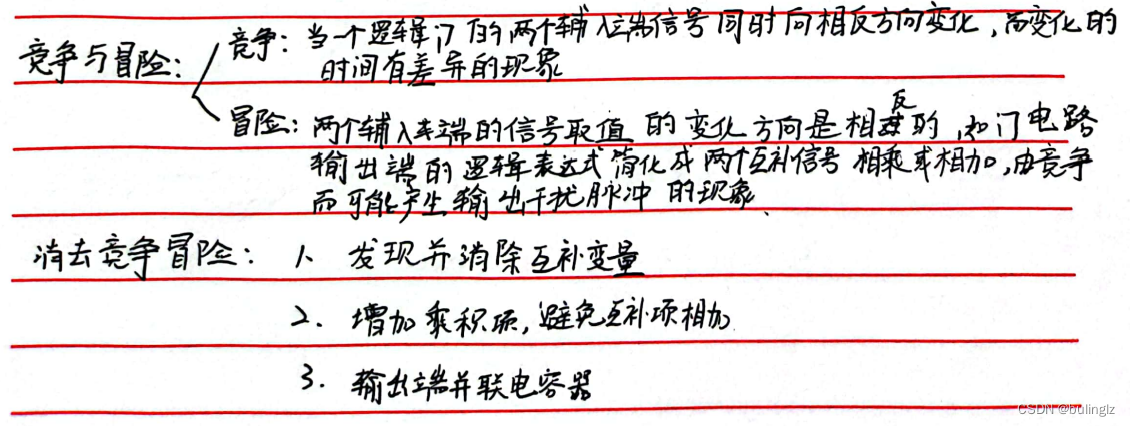

2.竞争与冒险

时电路中存在延迟造成的,当卡诺圈存在相切时,便存在竞争与冒险

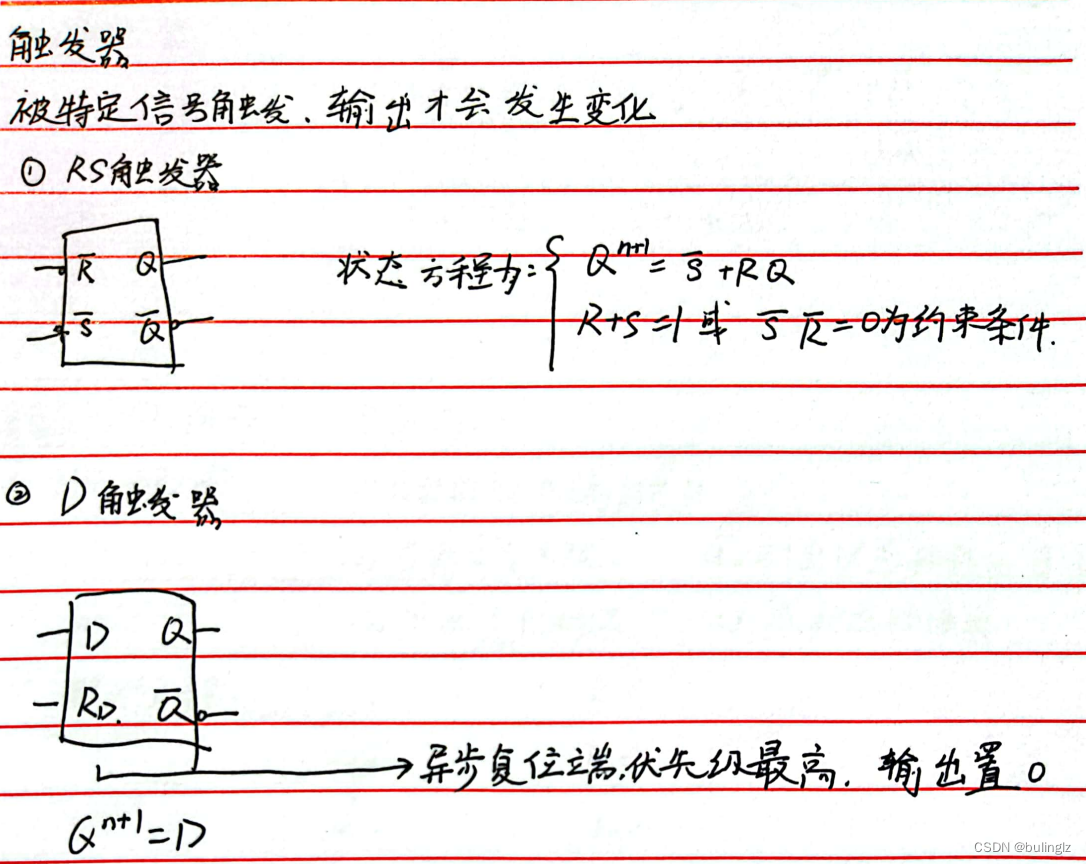

3.触发器

当被特定信号触发时,输出发生变化。触发器的输出是由当前状态和当前输入决定的

也可以说是输入信号和电路的初始状态

触发方式有三种:

电平触发,主从和边沿触发

RS触发器是电平触发,约束条件是R+S=1

分析时首先分析异步复位

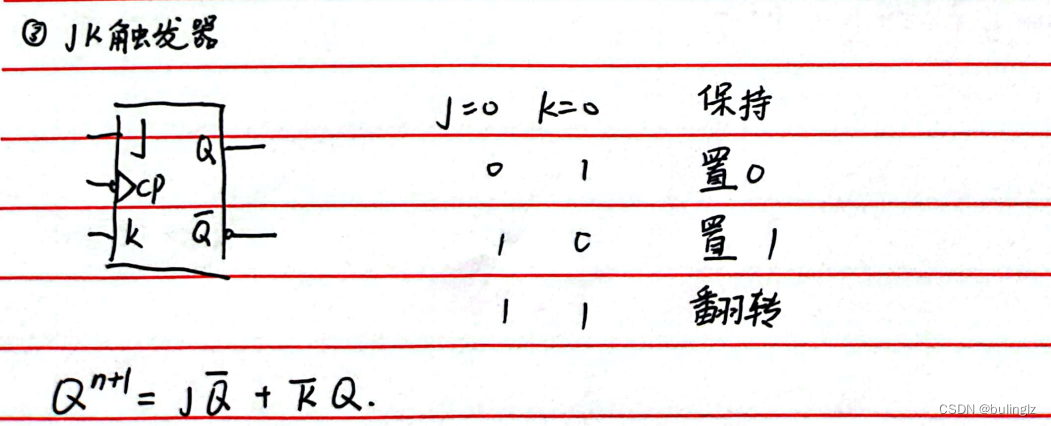

JK触发器,J是输出反转,K是输出保持。

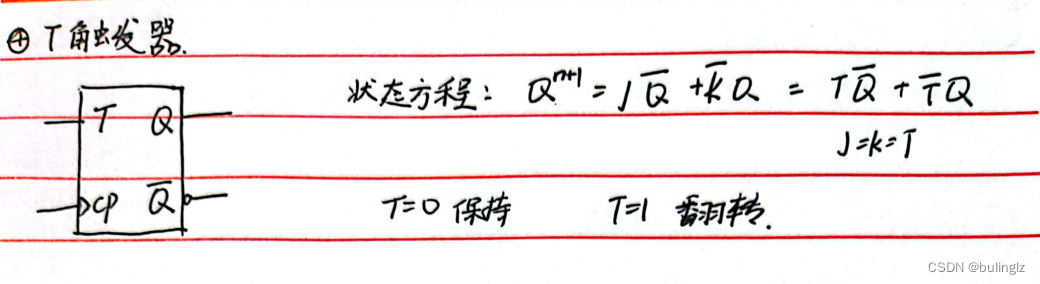

T触发器是JK触发器演变过来的

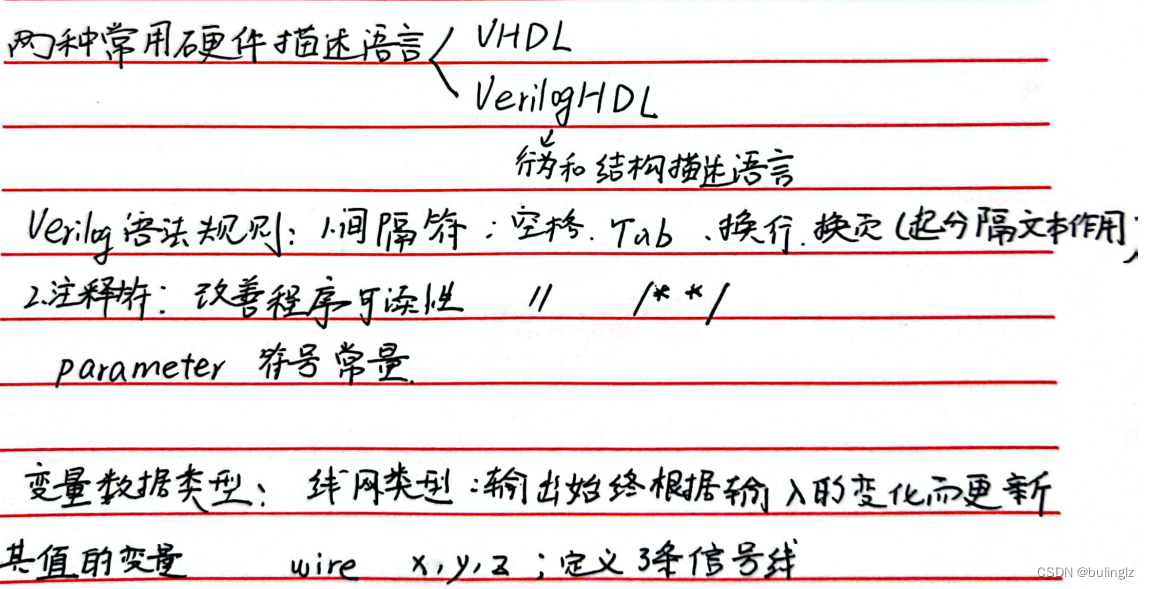

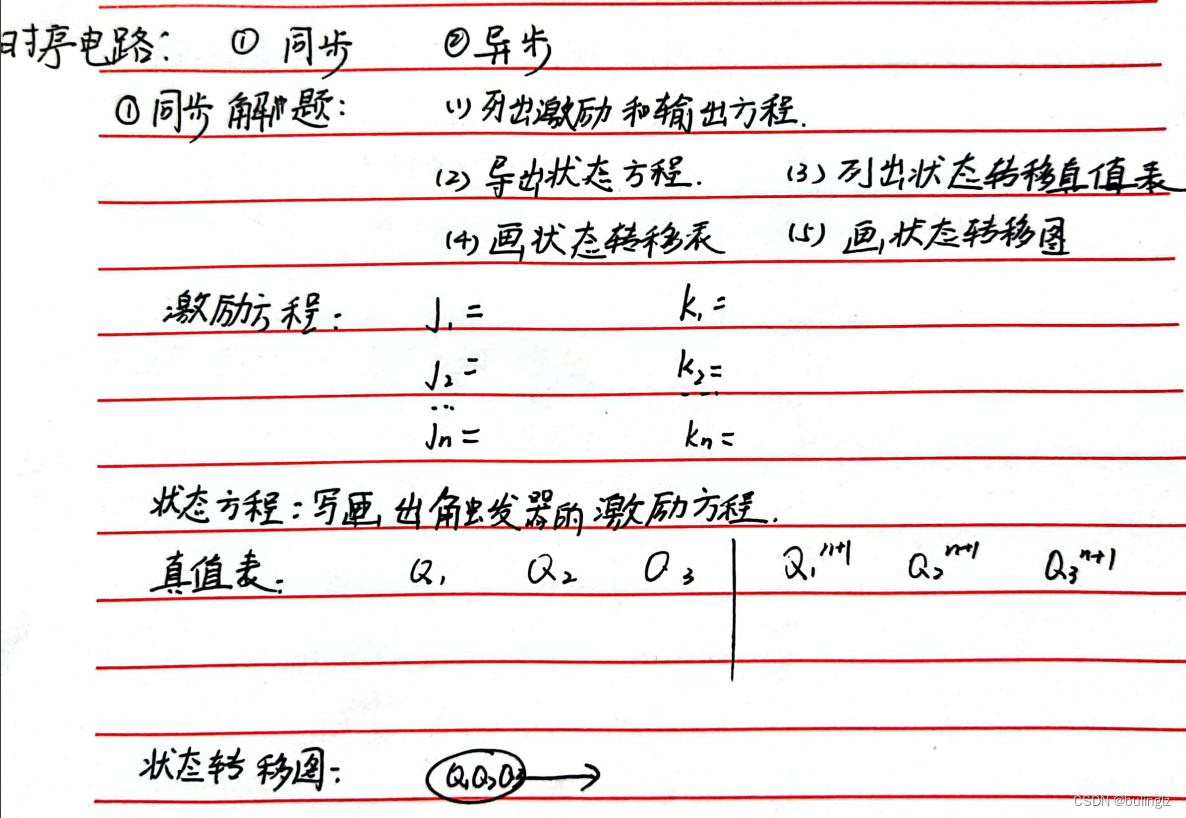

4.时序逻辑电路

同步和异步的区别

CP同时控制两个触发器,而异步是由多个进行控制

先写出激励(驱动)方程和输出方程,进而得到状态方程,列出状态方程的真值表

5.同步时序逻辑电路设计

列写状态转移真值标,然后利用卡诺图得到状态方程和输出方程,导出激励方程,最后画出电路图

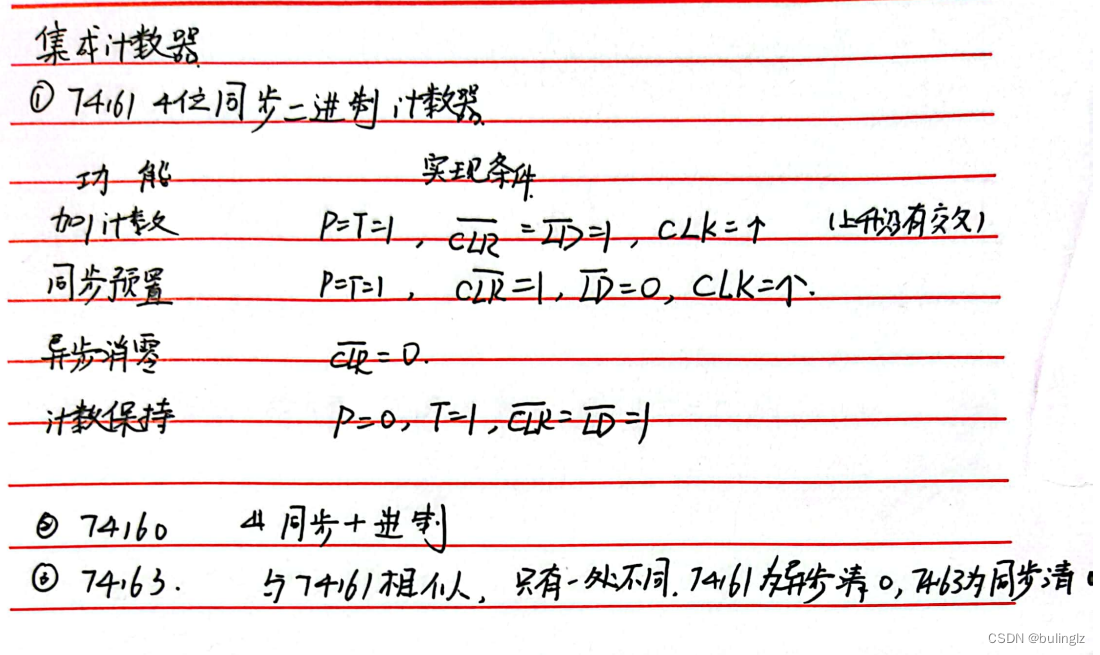

6.常用计数器分析

RCO 进位标志输出

P T 计数控制端

CLK控制信号触发控制端

LD非 有效时输出等于输入

74161 加1计数 同步预置 异步清零(CLR等于0,输出立即变为0) 计数保持

74160 为十进制计数器

74163 同步清零

计数器的设计? 同步置数法/异步清零法

7.构造一个模10同步计数器需要10个状态,需要4个触发器

因为,模10计数器需要计10个数,十进制9->二进制1001;需要注意的是,一个触发器可以表示一位二进制数,因此需要四个触发器

8.全加器

全加器能进行加数、被加数和低位来的进位信号相加,并根据求和结果给出该位的进位信号。

全加器与半加器的区别在于有无低位进位作为加数

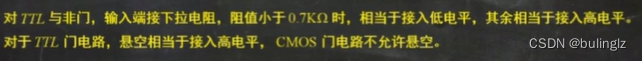

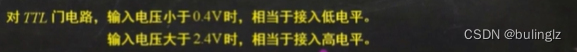

9.移位寄存器与集成逻辑门

![]()

(对于CMOS电路只要接地就相当于低电平)

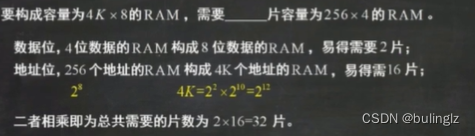

10.半导体存储器

半导体存储器从存/取两方面可将功能分为两大类,即RAM(具有易失性)和ROM(具有非易失性)

若存储的容量为512*32位,则该存储器地址线有条,数据线有条

? ? ? ? ?思路·:对存储容量的描述即存储容量=字数*位数;存储器中有n条地址线,即有2^n个存储空间;若存储器中有m条数据线,则位数为m;本题512K=2^9K(K为2的十次方)

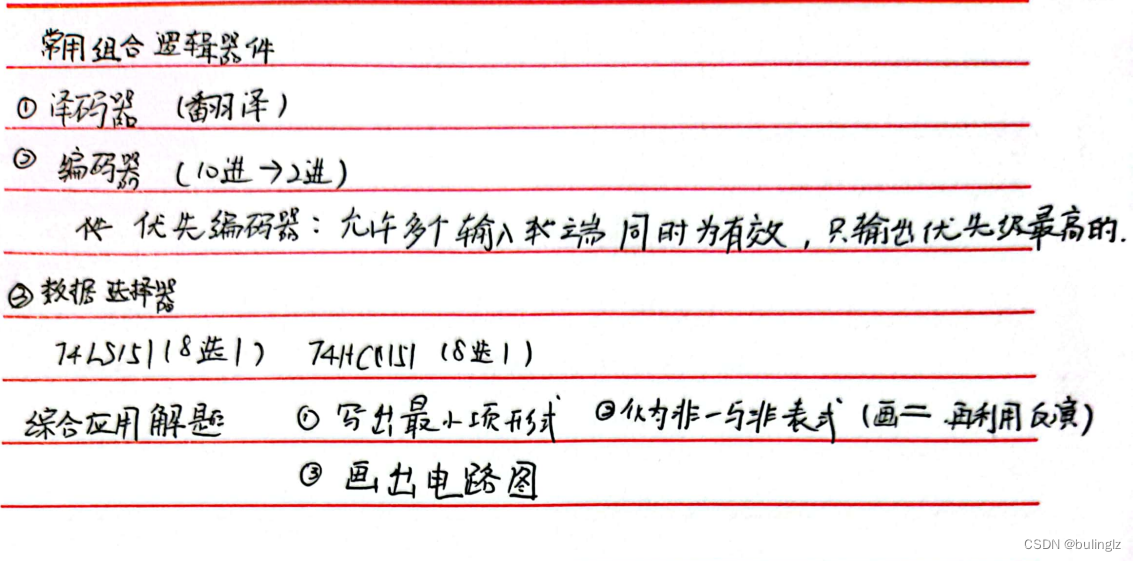

11.计数器、寄存器、触发器属于时序电路,但是译码器不属于时序电路

12.下降沿触发的 JK 触发器:在CP脉冲的下降沿到来瞬间使 触发器的状态(Q的值)才发生变化

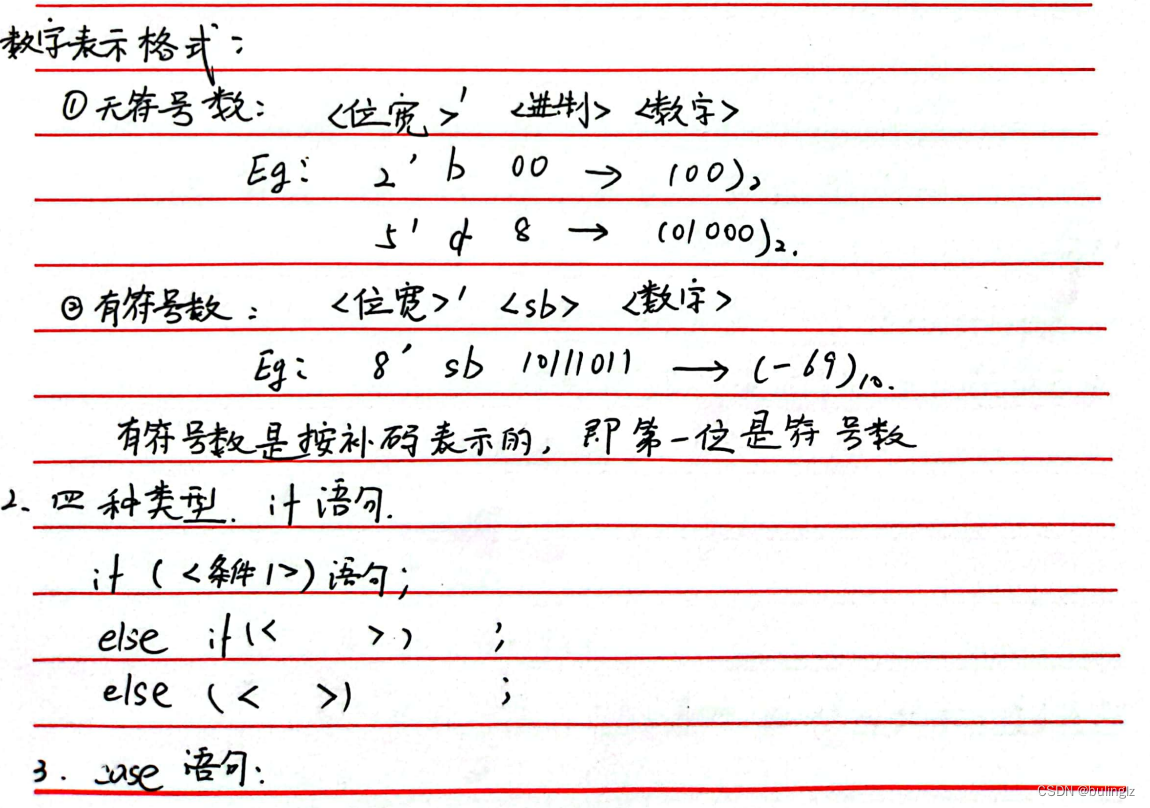

13.常用数制转换:

????????十进制数用下标“D”表示,也可省略。二进制数用下标“B”表示。八进制数用下标“O”表示。十六进制数用下标“H”表示

????????非十进制数转换成十进制数:采用按权展开相加法。具体步骤是,首先把非十进制 数写成按位权展开的多项式,然后按十进制数的计数规则 求其和。

????????十进制数转换成其它进制数:

????????????????????????????????????????????????整数转换:除基数取余法;纯小数转换:乘基数取整法

怎样在数据转换中,保证转换的精度不变?

答:转换后的精度与转换前的进度在同一个数量级就可以了。

????????二进制数转换成八进制数或十六进制数:三位二进制数对应一位八进制数。四位二进制数对应 一位十六进制数

14.正码,反码与补码

正数的原码、反码和补码形式相同。求负数的 补码时,为了避免做减法运算,一般方法是:先求 出负数的反码(将原码的数值位逐位求反),然后 在最低位加1即可得到补码

15.CMOS漏极开路(OD)门和三态输出门电路

CMOS的提出:输出短接,在一定情况下会产 生低阻通路,大电流有可能导 致器件的损毁,并且无法确定 输出是高电平还是低电平

漏极开路:(a)工作时必须外接电源和电阻;(b)与非逻辑不变(c) 可以实现线与功能;

????????上拉电阻对OD门动态性能的影响:Rp的值愈小,负载电容的充电时间 常数亦愈小,因而开关速度愈快。 但功耗大,且可能使输出电流超过允 许的最大值IOL(max) 。Rp的值大,可保证输出电流不能超 过允许的最大值IOL(max)、功耗小。 但负载电容的充电时间常数亦愈大, 开关速度因而愈慢。

CMOS 反相器:对于NMOS管,其栅极电压VG=1(高电平)时,NMOS管导通。;对于PMOS管,其栅极电压VG=0(低电平)时,PMOS管导通。

CMOS反相器的重要特点:第一,vI是高电平还是低电平 ,TN和TP中总是一个导通而 另一个截止。CMOS反相器的静态功耗几乎为零。第二,MOS管导通电阻低,截止电阻高。使充、放电时间 常数小,开关速度更快,具有更强的带负载能力。第三,MOS管的,IG≈0,输入电阻高。 理论上可以带任 意同类门,但负载门输入杂散电容会影响开关速度。

????????其他基本CMOS 逻辑门电路:上下对称是非;PMOS管并联是与;PMOS管串联是或

16.能实现线与逻辑功能的是CMOS漏极开路门

17.三态门有意使能控制端,当使能端为无效电平时,输出端为高电平

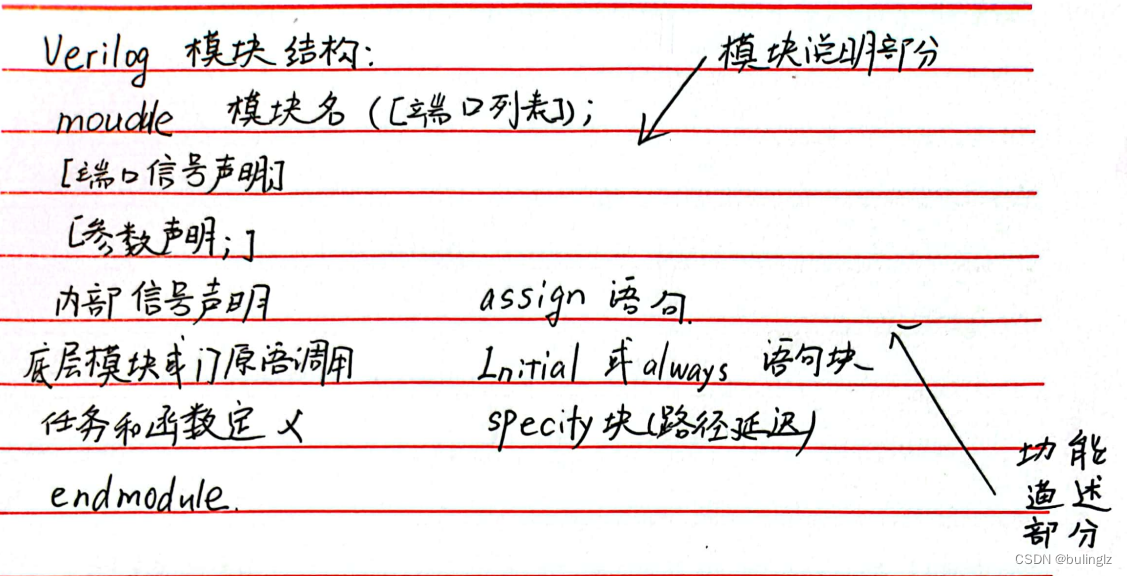

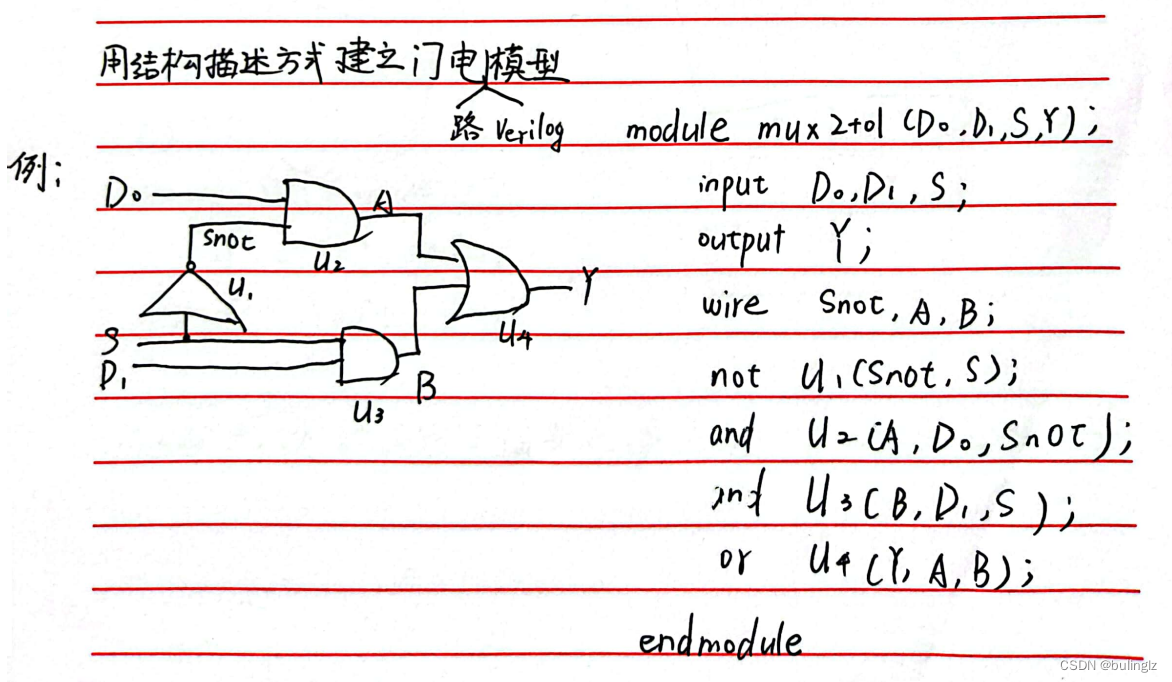

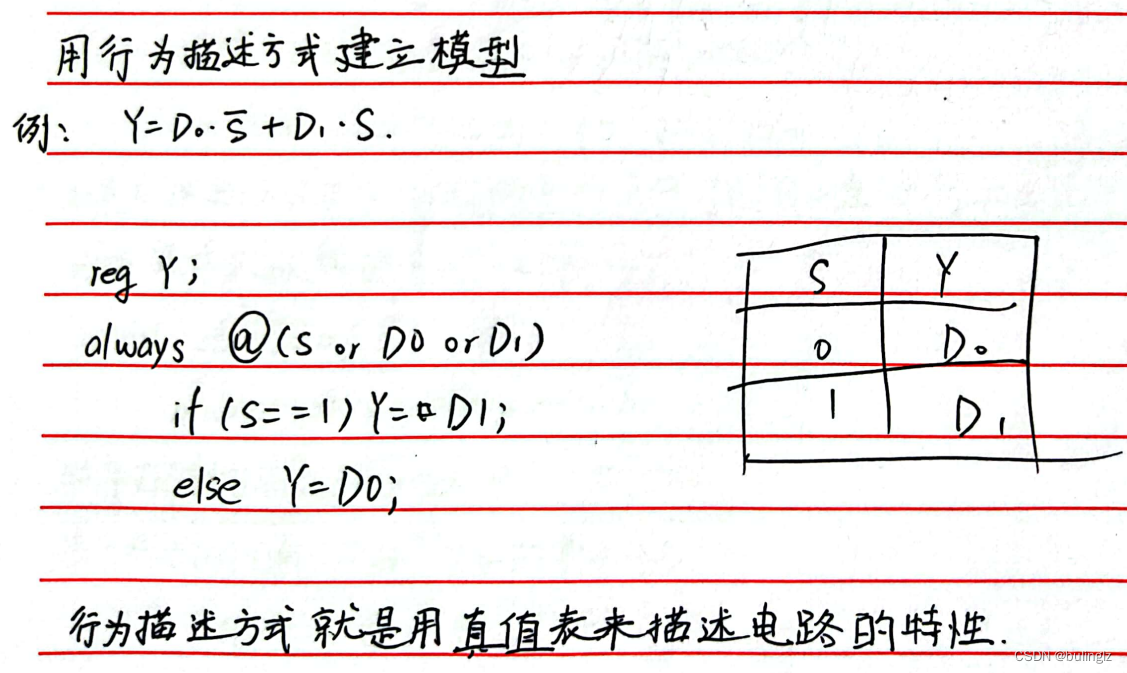

18.在verilog中,用来定义输入引脚的关键词为input,用来定义线网型信号量的关键词是wire,模块的关键词是module

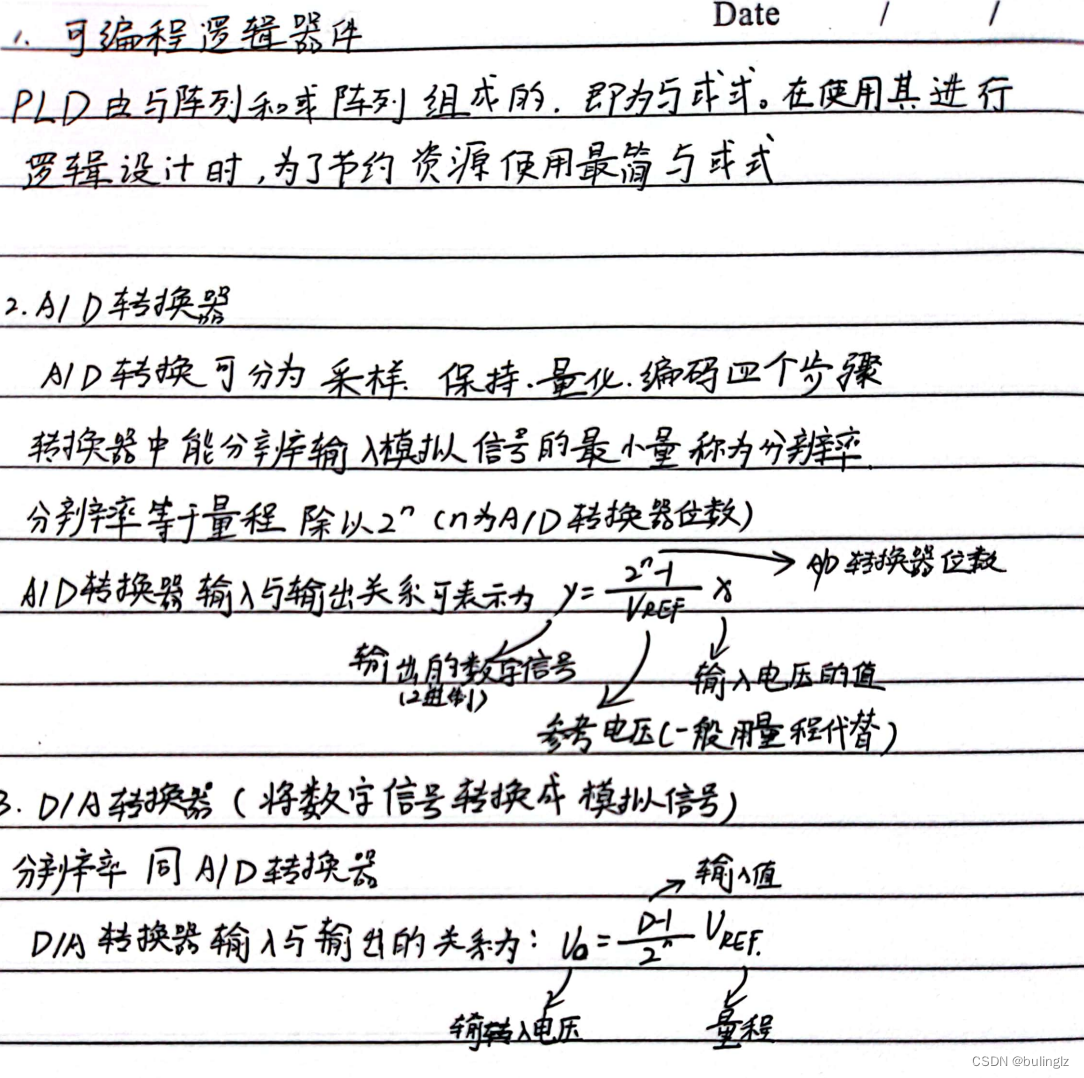

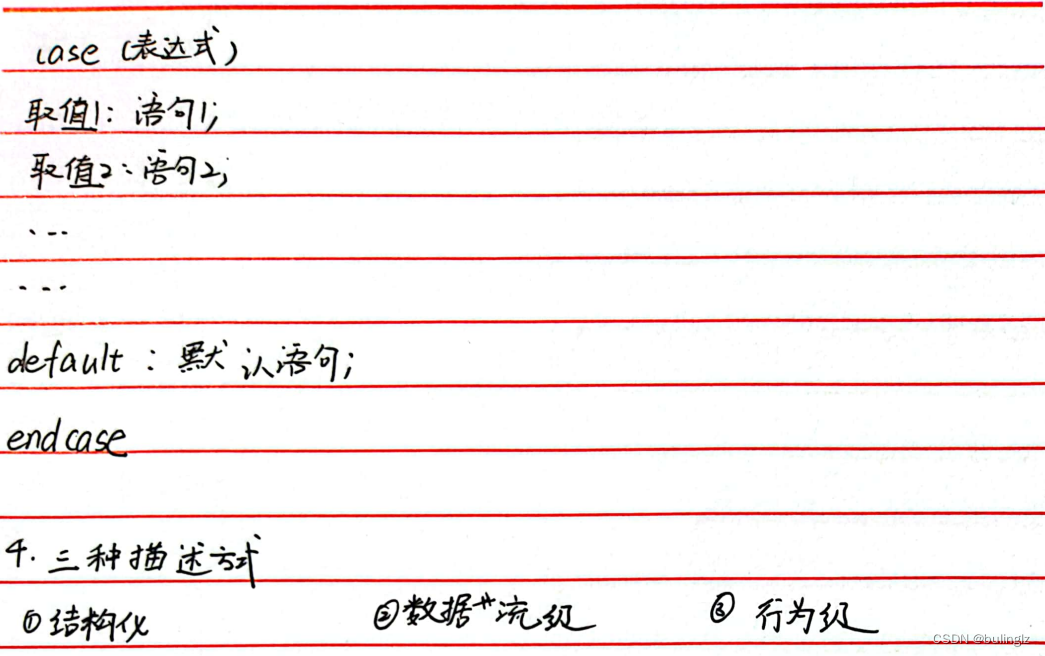

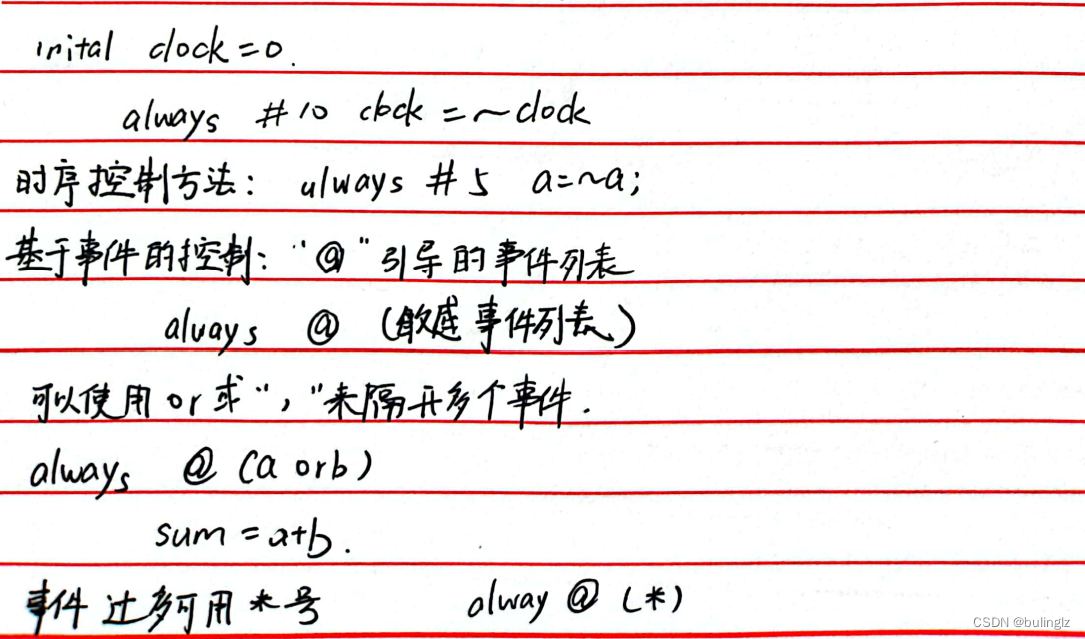

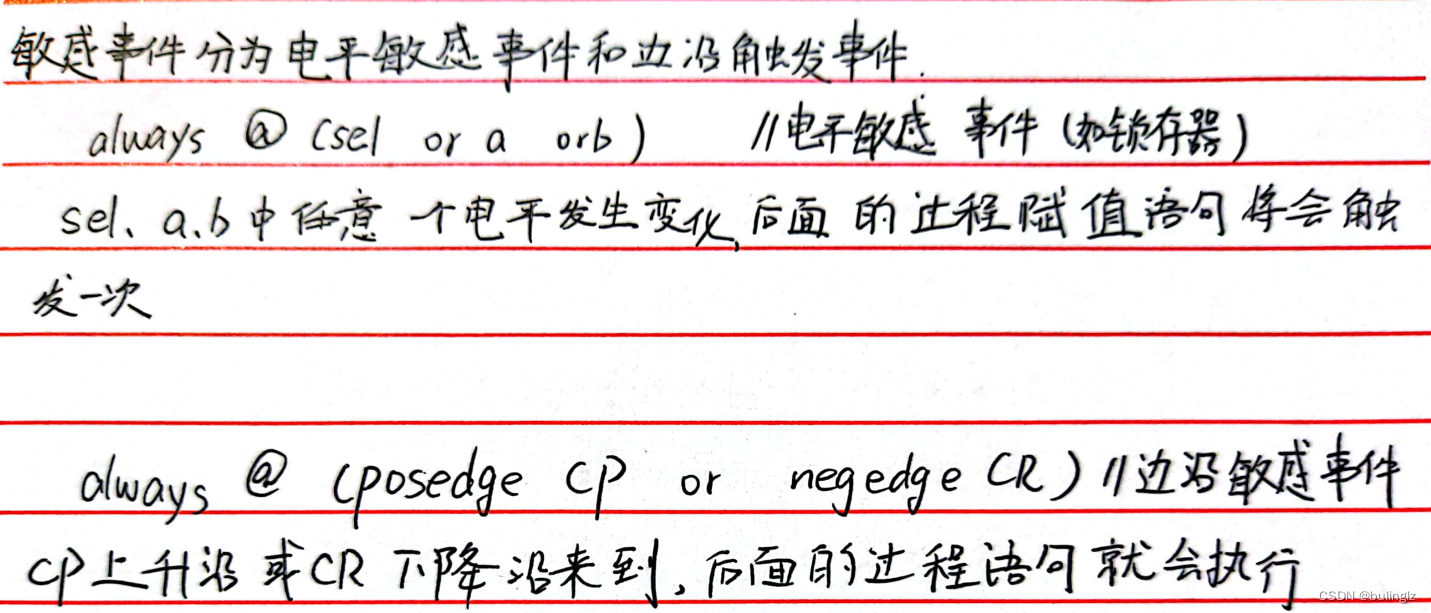

各人上课手抄笔记(字迹潦草,请见谅)

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- web一些实验代码——会话管理

- Linux操作系统基础:从入门到实践

- SpringBoot使用MockMVC单元测试Controller

- 【MySQL】语法 sum(条件表达式) 的巧用

- tag 标签

- 用PDETool计算磁场

- 深入了解鸿鹄电子招投标系统:Java版企业电子招标采购系统的核心功能

- Enhance .NET 8 Apps with Code Editing

- HPV治疗期间如何预防重复感染?谭巍主任讲述具体方法

- TensorRT(C++)基础代码解析