王道考研计算机组成原理——存储系统

存储系统的基础知识?

?

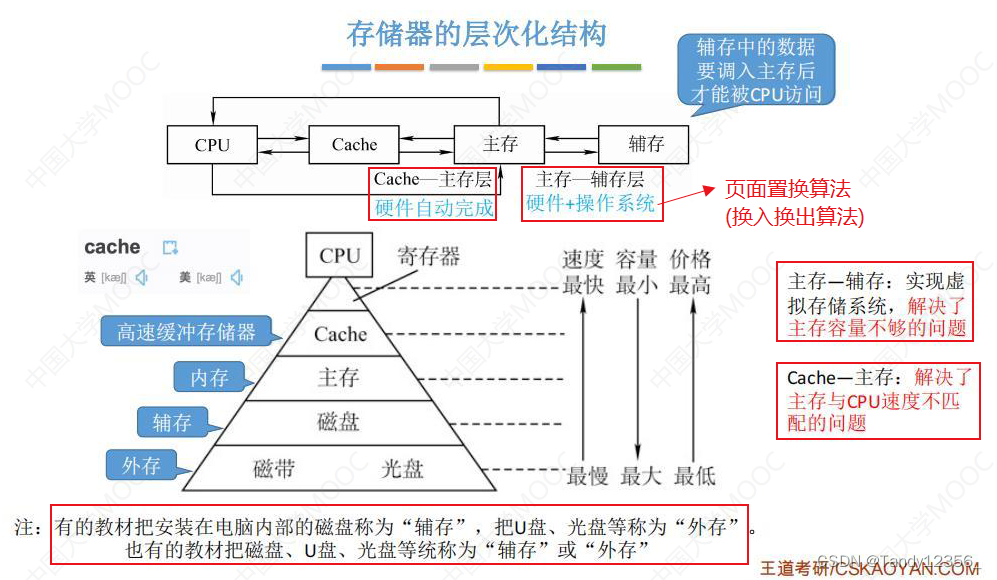

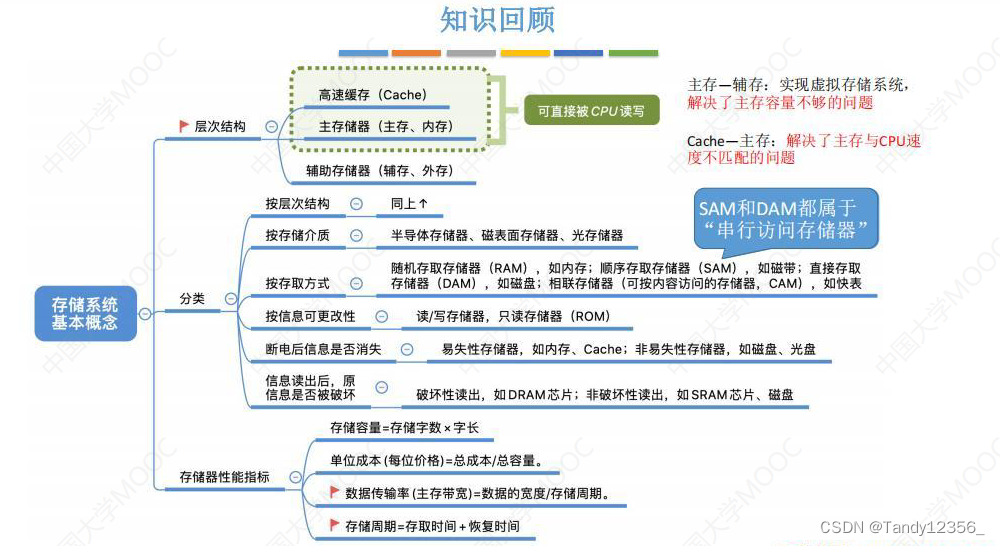

微信打开的时候会有一个人站在地球上,这个过程就是把程序从辅存转移到主存,数据只有调入主存当中才可以被CPU访问

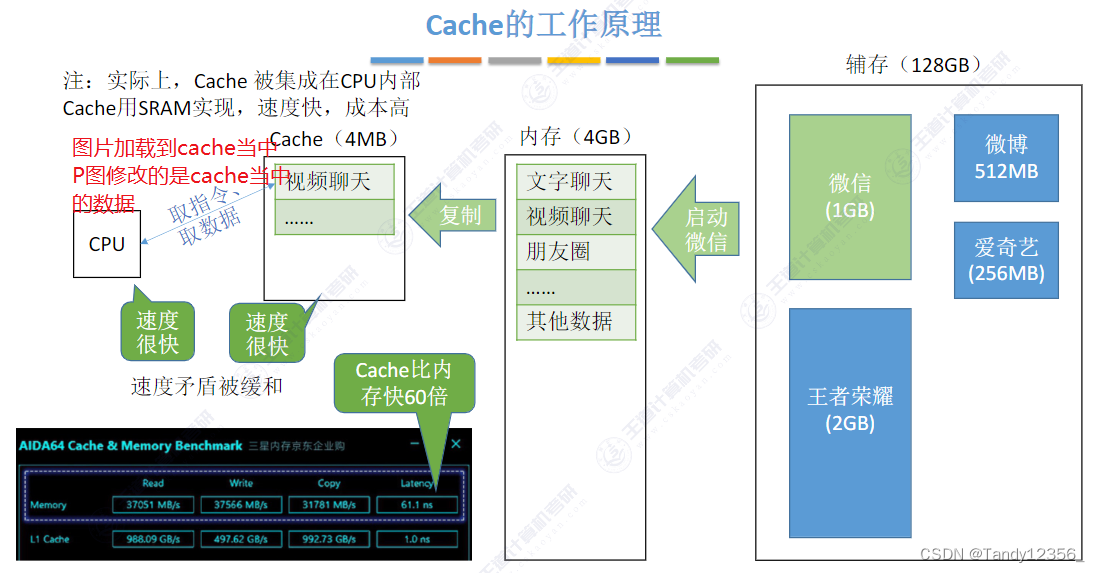

cache:主存速度还是慢,为了进一步缓解CPU和主存之间的速度矛盾

在微信打视频聊天的时候,在这一段比较长的时间内可能会频繁地访问和打视频电话有关的代码和数据,就可以把这部分数据放到cache当中

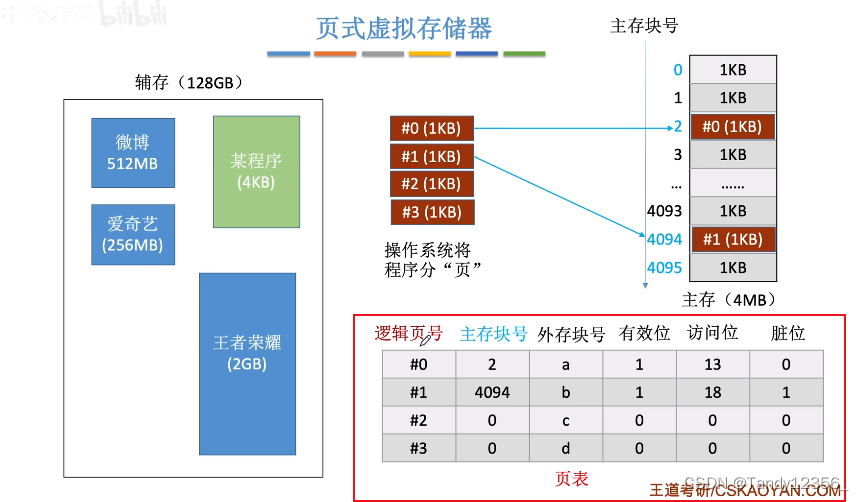

虚拟存储:应用程序员可以看到的主存容量要比实际容量大得多的

其中主存和cache都可以和CPU直接数据交换

主存——辅存:解决了主存容量不足的问题

主存——cache:解决了主存和CPU的速度不匹配的问题

现在的辅存基本都采用的固态硬盘

m.2接口的SD读写速度可达4GB/s

各种存储器类型

光盘:CD-ROM VCD DVD;磁带》顺序存储

机械硬盘:磁盘

磁带不支持随机访问,当你读写某个存储单元当中的数据的时候,显然是和这个存储单元所在的物理位置是有关的,因此磁带只能顺序访问

随机访问指的是你随便指定一个地址,它访问的速度是一样的

磁盘驱动器:两种的结合体,光盘貌似也是?

其他三种是指定地址,然后去访问该地址,相联存储器是根据数据内容查找它的存储位置在哪

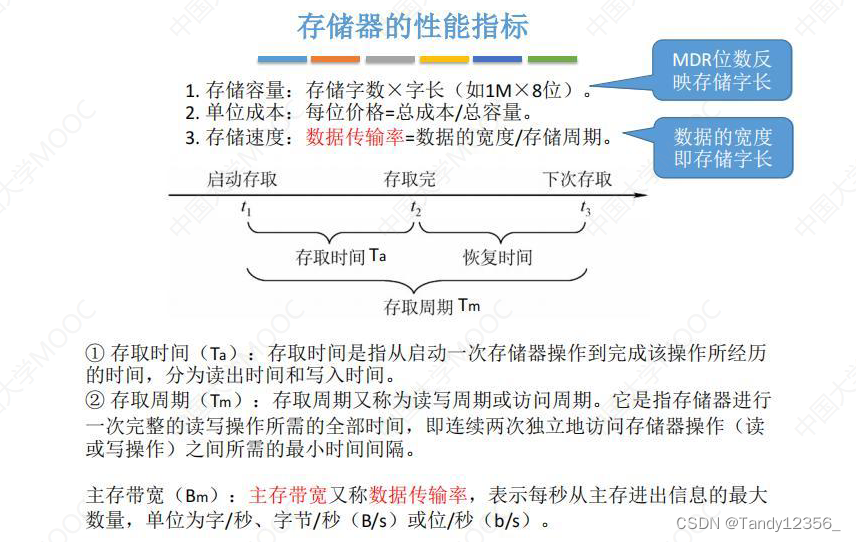

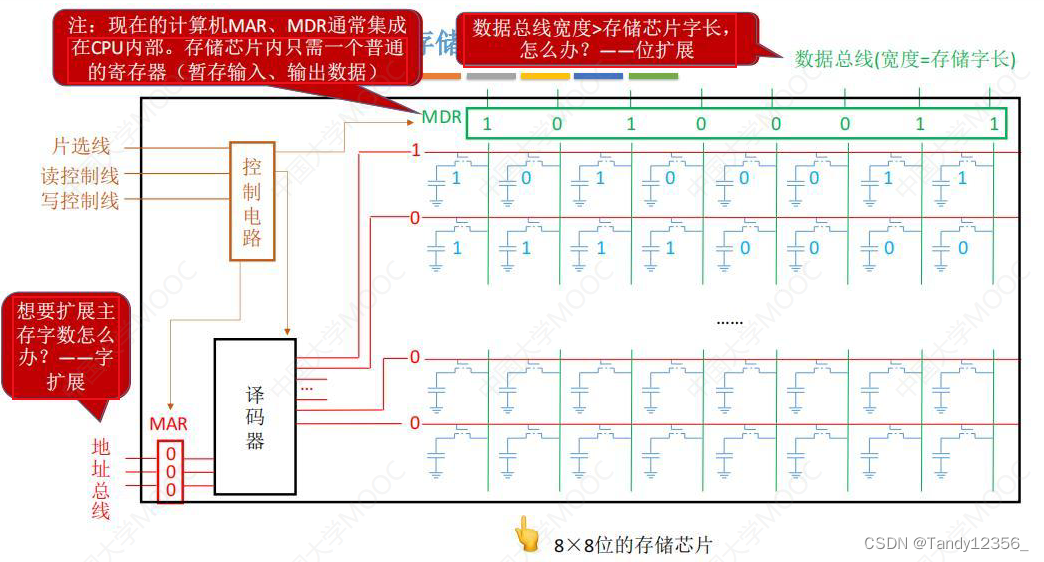

MAR反应的是存储字数,MDR反应的是存储字长?

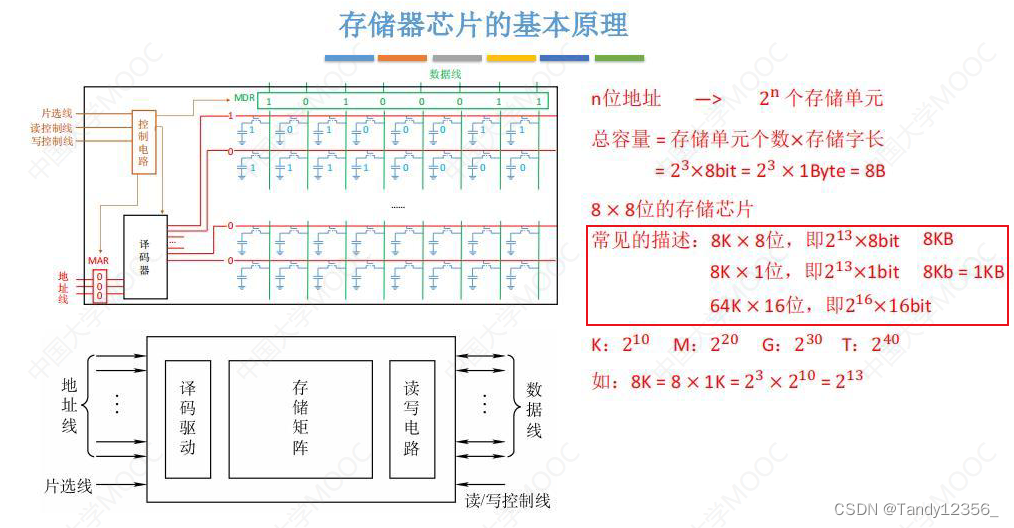

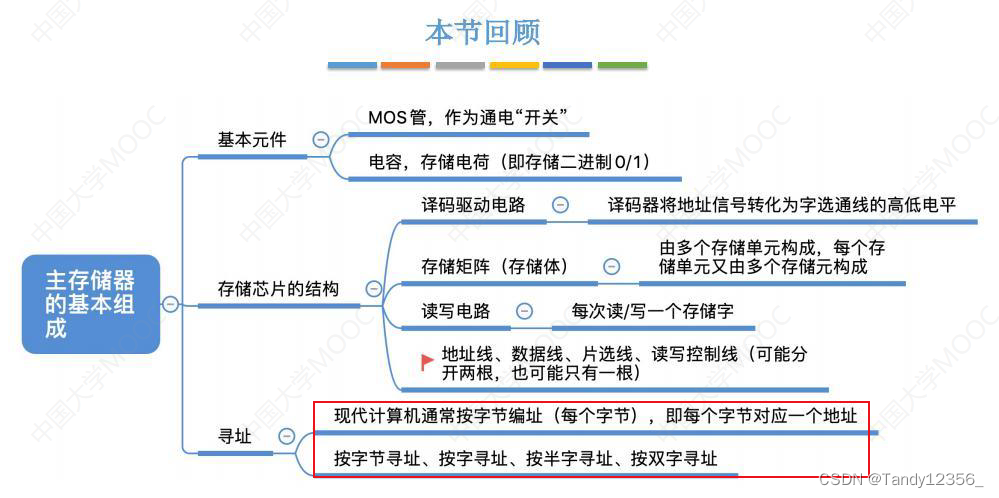

主存储器的基本组成?

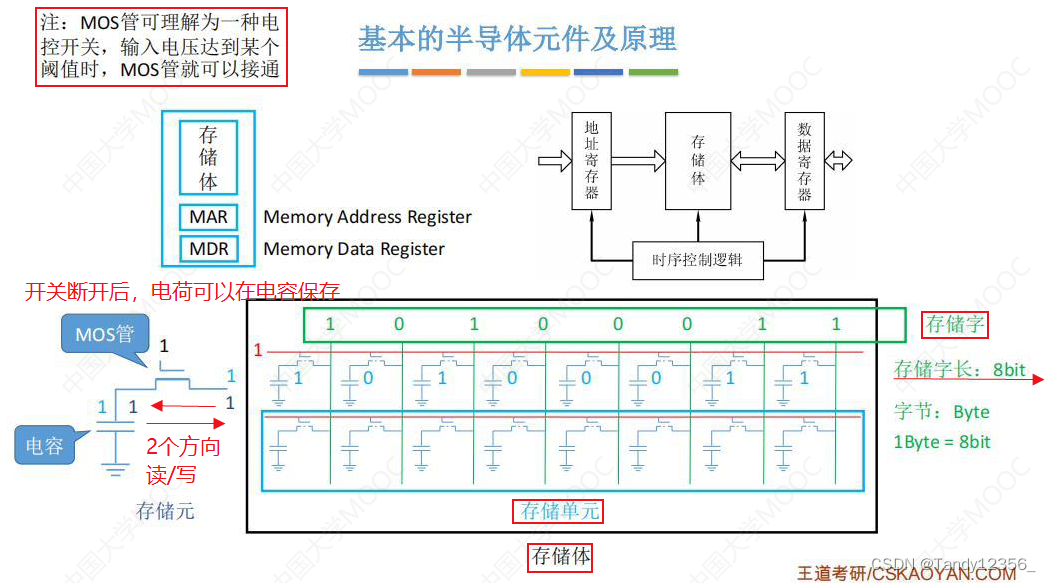

MOS管:电压达到一定条件成为导体,否则不导电,所以它是一个半导体元器件

电容:下方接地,当上面给了5V之后,电荷移动给电容充电,进而保存一个bit的电荷

电容带电荷表示的是一个二进制的1,否则不带电就是0

mos管决定了电容的充/放电(数据的写入/读出)

一次读写都是以存储字为单位的

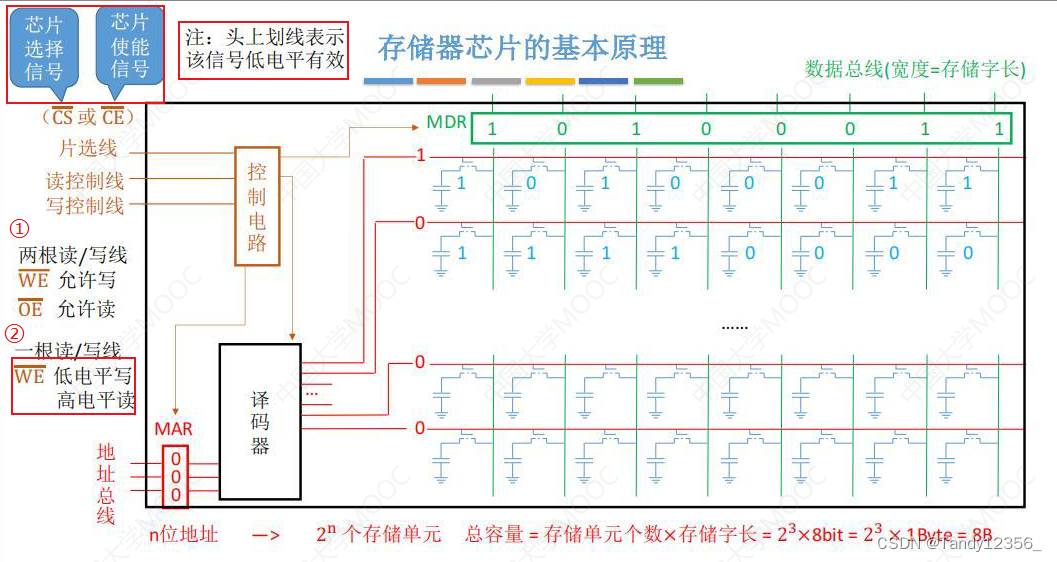

每个地址对应的是译码器的一条输出线,一条输出线一次性读取/写入一整个存储字的内容

红色的线选通之后,通过绿色的线把每一位的信息传送到MDR当中,然后CPU通过数据总线从MDR当中取走一整个的数据

红色的线叫字选线,绿色的叫数据线(位线);地址总线和数据总线都是连CPU的

控制电路:检测当电信号稳定的时候才放入MAR或者取走MDR当中的数据

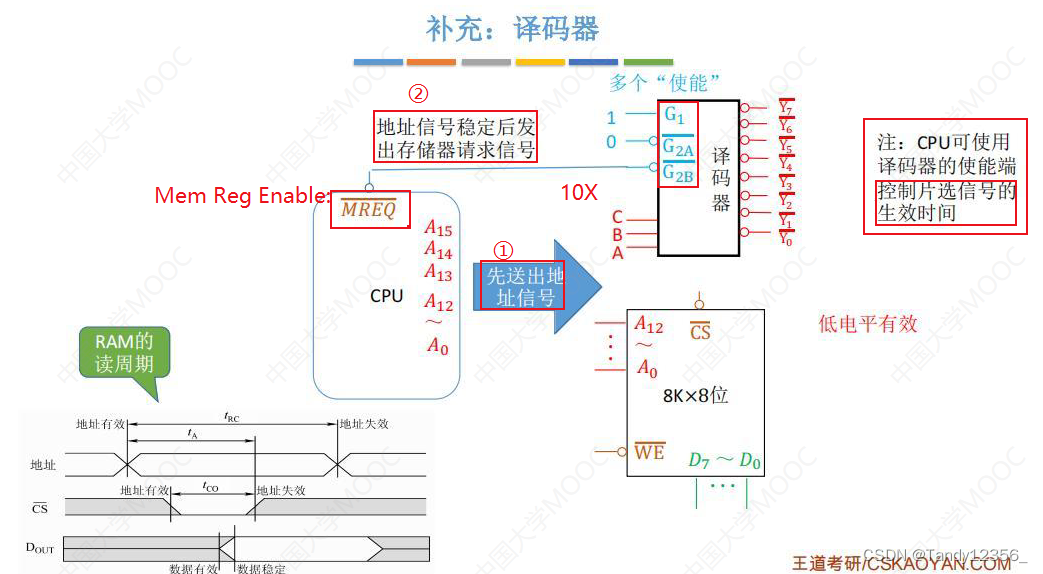

为了让译码器输出的电信号稳定可靠,通常会在译码器的后面接一个驱动器来对电信号进行放大

读写电路:红色、绿色的线+控制电路

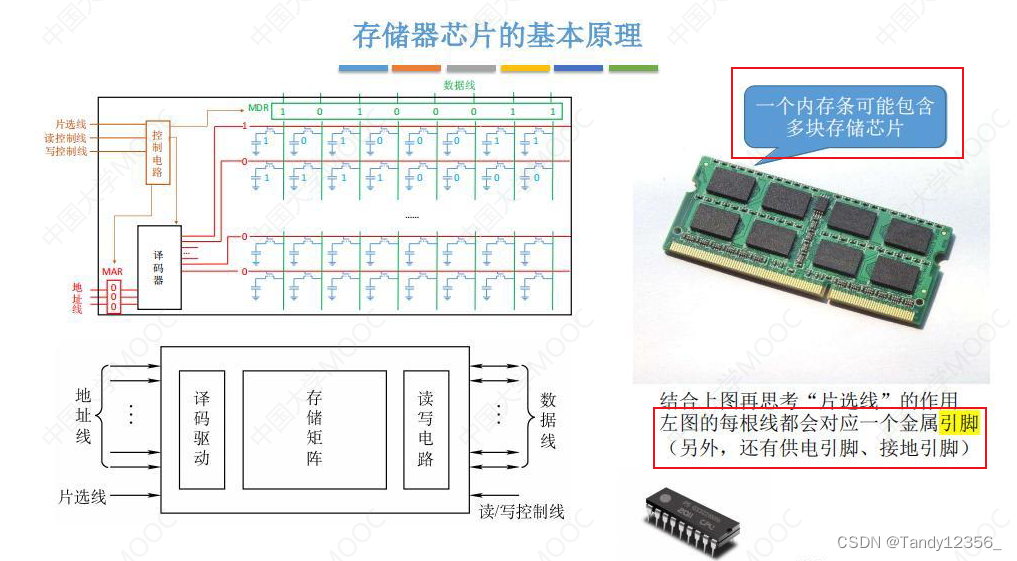

片选线:有很多块小芯片,应该选哪个使用呢?

8×8位的芯片:2^8个存储单元(8位地址)×每个存储单元的存储字长

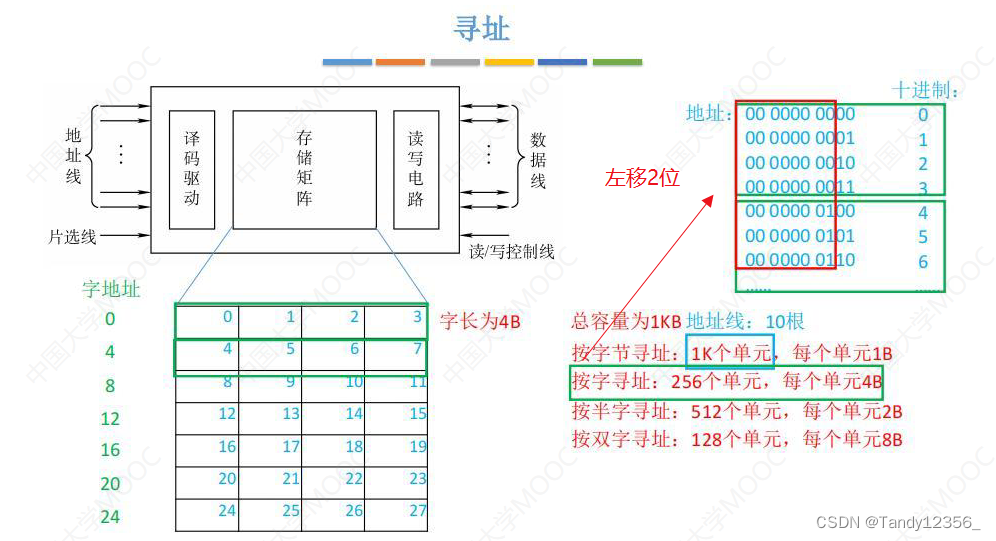

按字节编址,但是支持按字寻址

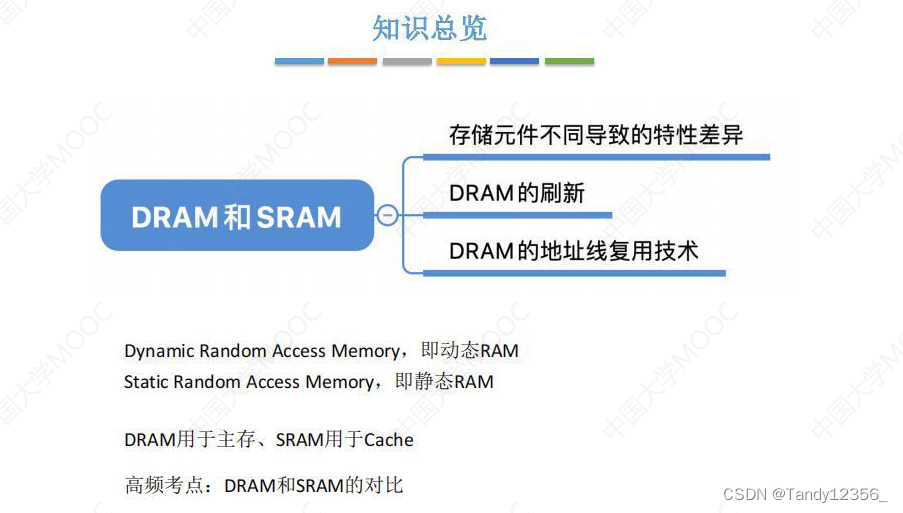

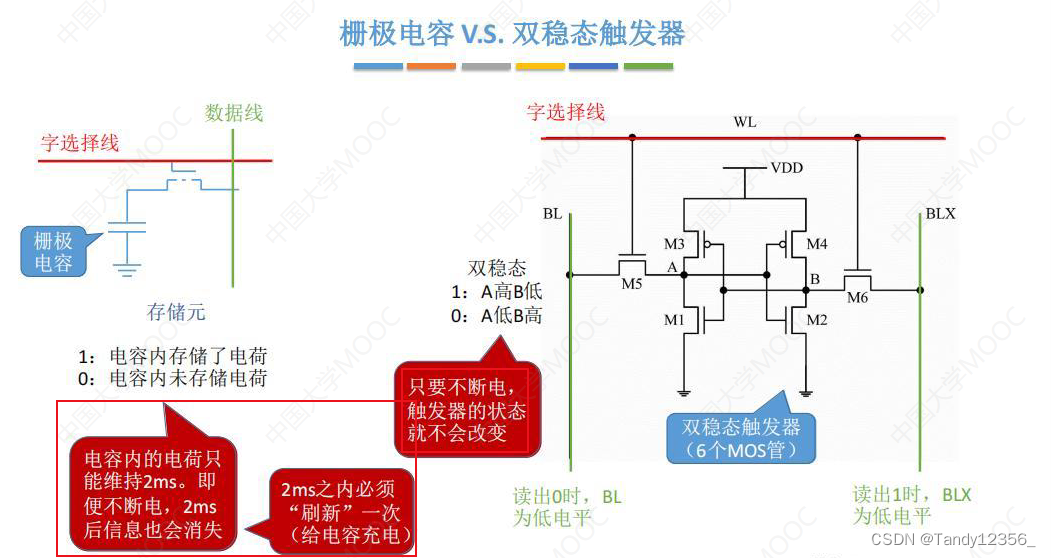

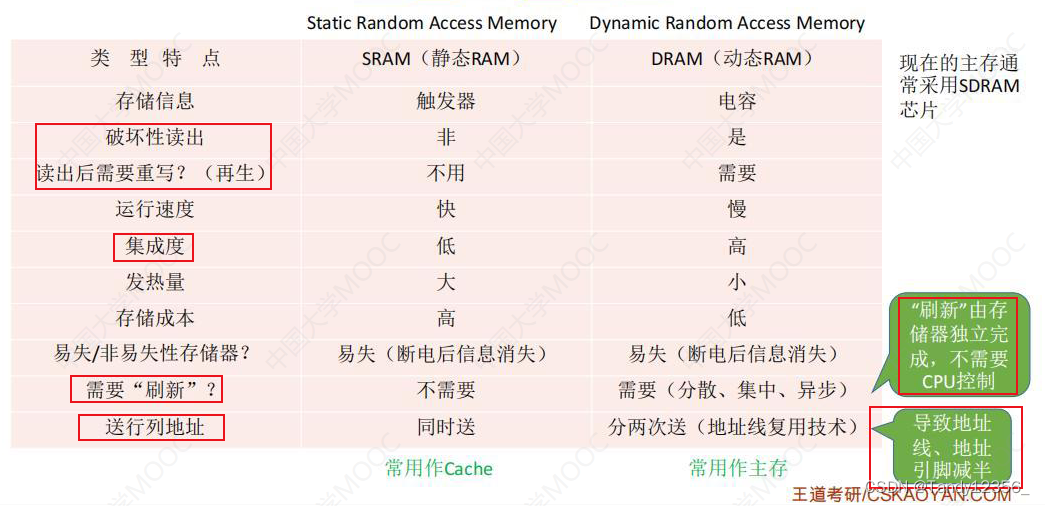

SRAM与DRAM的区别?

只有行和列的选通线同时接通,该存储单元才被选中

刷新一行:先把对应行的MOS管置1让他接通,然后进行读/写(有硬件支持:先读出一行的信息,然后再重新写入)

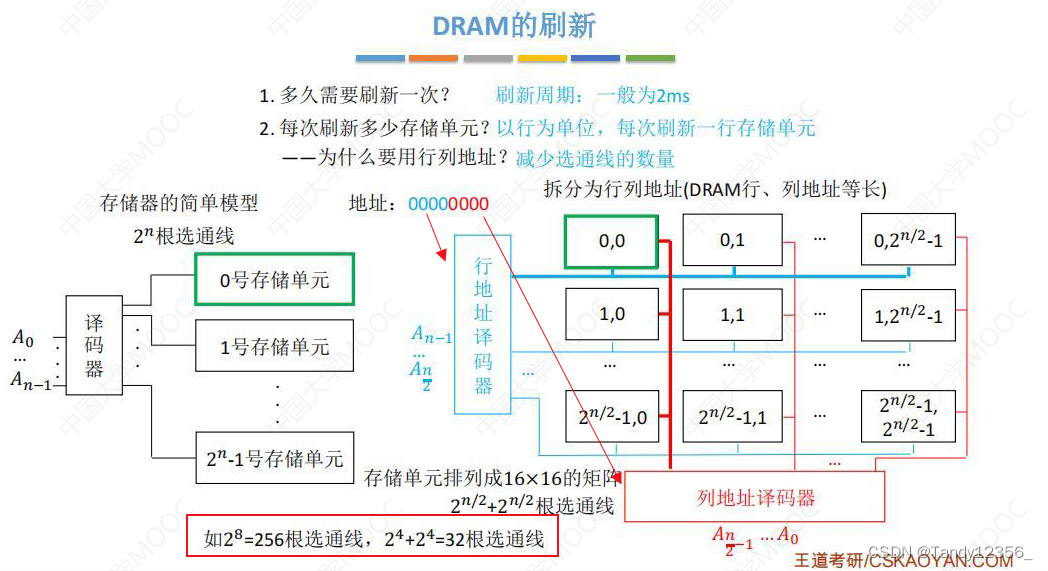

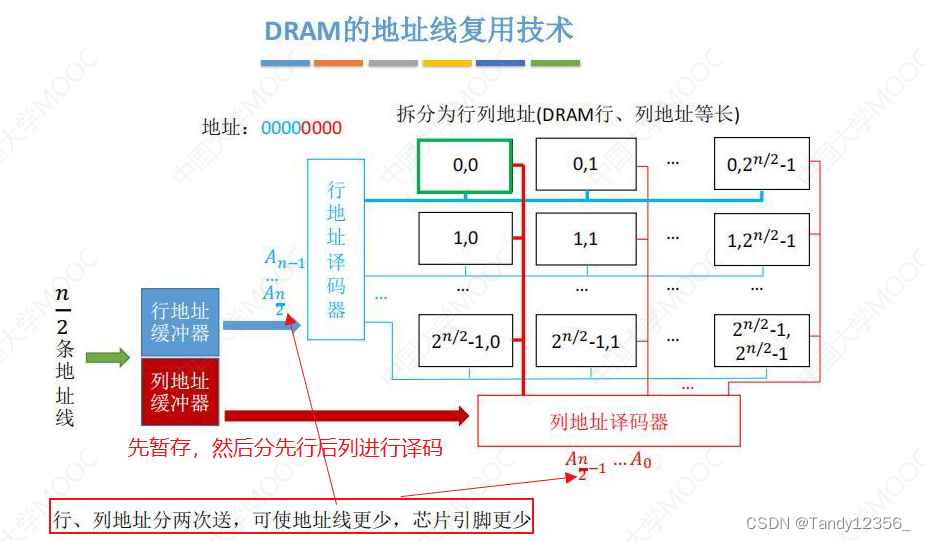

为了让DRAM的地址线更少:地址线复用技术

地址线指的是传入译码器的,当然DRAM内存里面还是(2^n)*(2^n)的布局;以前是n/2位地址线同时传输行和列地址然后进行译码,一共2^n根地址线,现在是行地址译码器和列地址译码器共用n/2根地址线,先翻译行,再翻译列,从而达到减少地址线的目的

DDR3 DDR4都是SDRAM芯片

重写需要消耗一定的时间,使得CPU连续访问同一个内存的时间变长

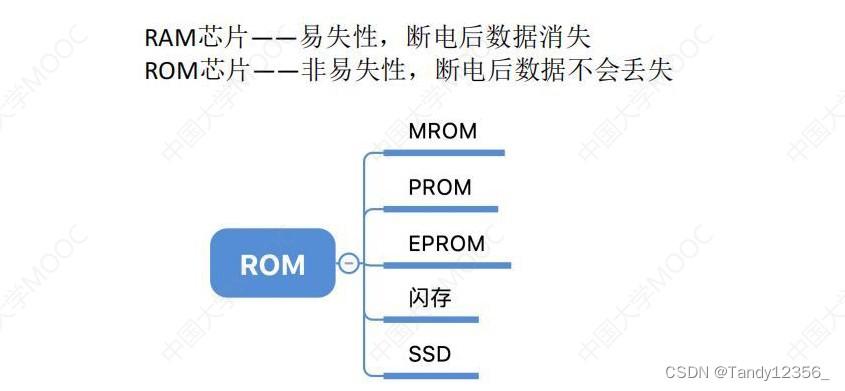

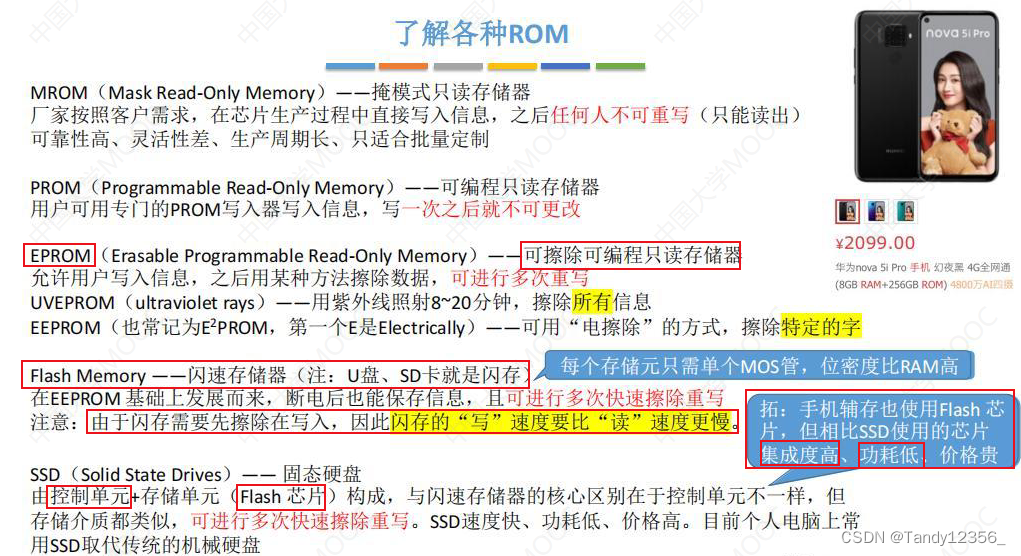

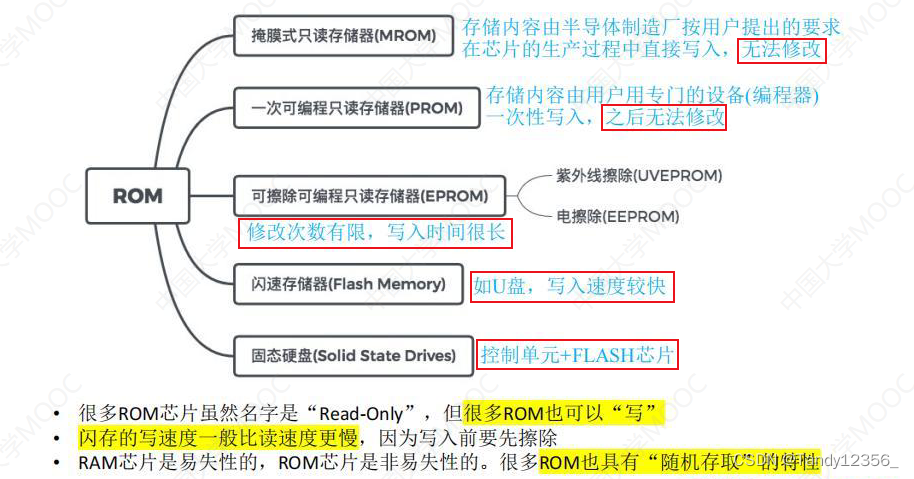

只读存储器ROM?

各种ROM都是支持随机访问的?

因为需要先擦除再写入,所以写比读要慢

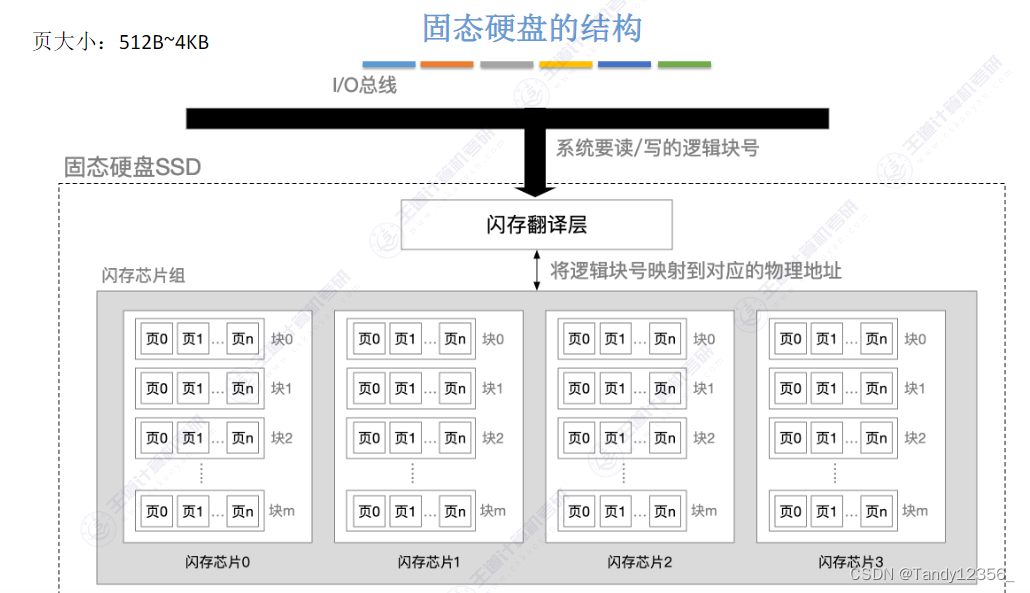

固态硬盘=flash闪存芯片+控制单元组成

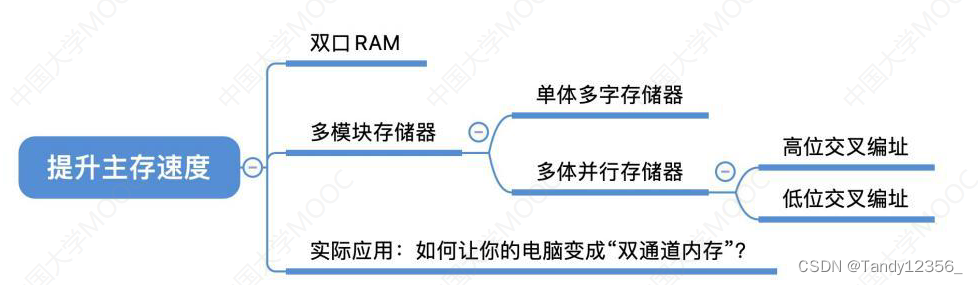

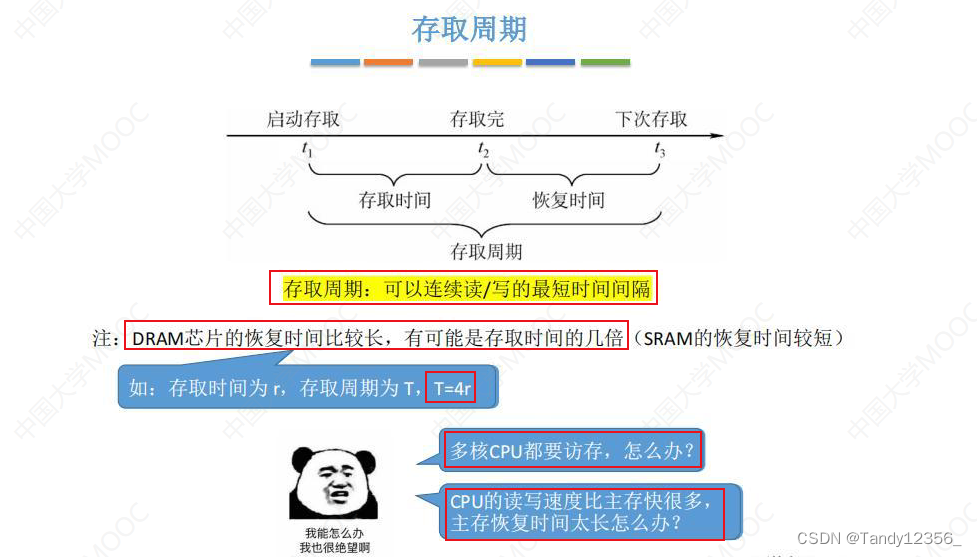

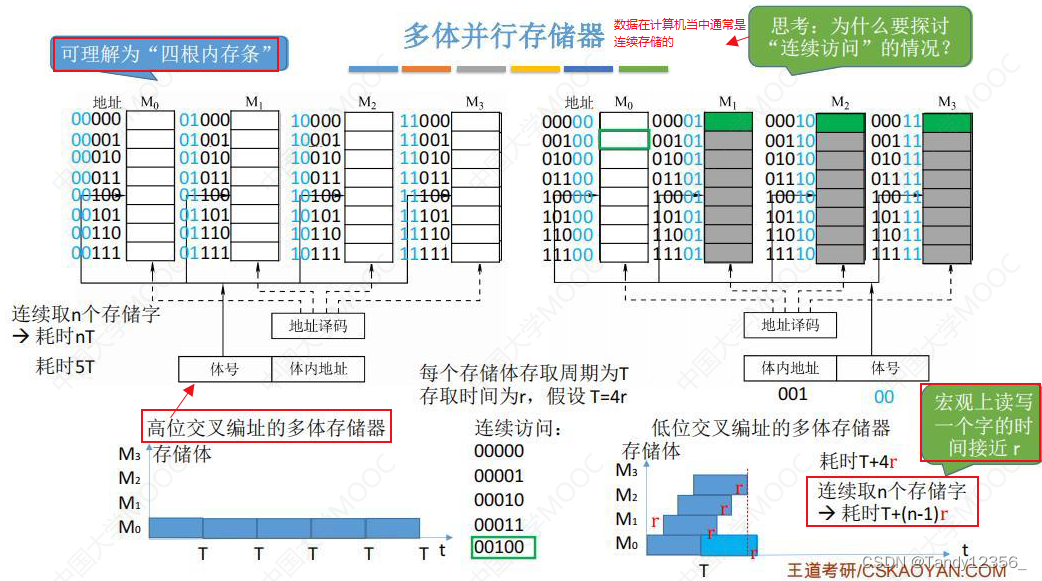

多体并行存储器?

恢复时间:你把电容里面的电荷都读走了,不得再往里面重新写入电荷吗?所以不得安排个恢复时间??

双端口RAM:双核的CPU通过RAM的两个端口来对内存进行并行的访问?

总线设计(在电脑主板)就会更加复杂

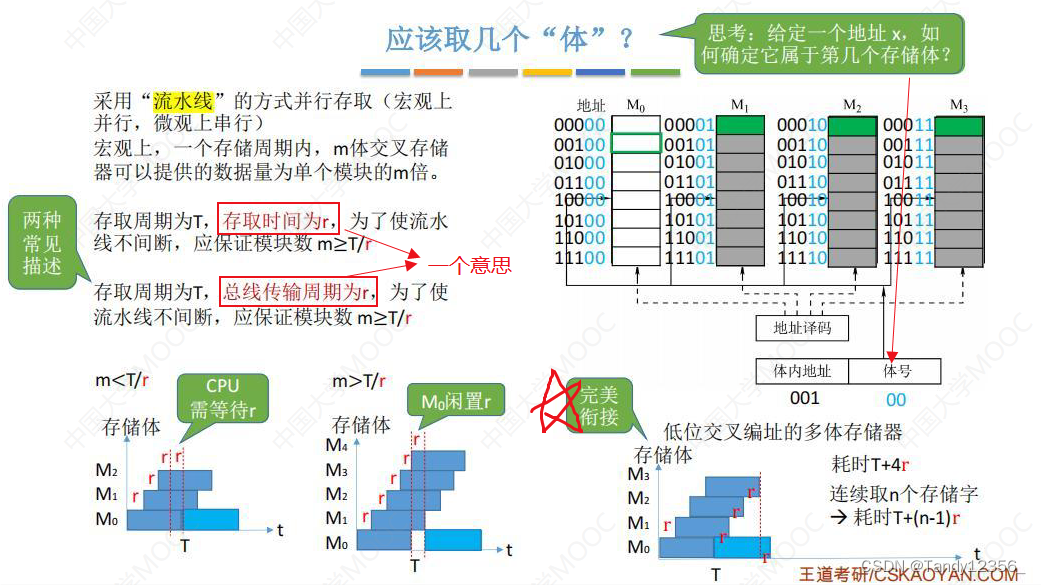

CPU从存储单元当中读/写一个字实际只需要r的时间,后面3r的时间由硬件自动处理,剩下的3r的时间里CPU都是处于空闲的,但是对于这个存储体却并不能进行操作

宏观上n->∞的时候,采用低位交叉编址的内存,CPU连续读写的时间接近r

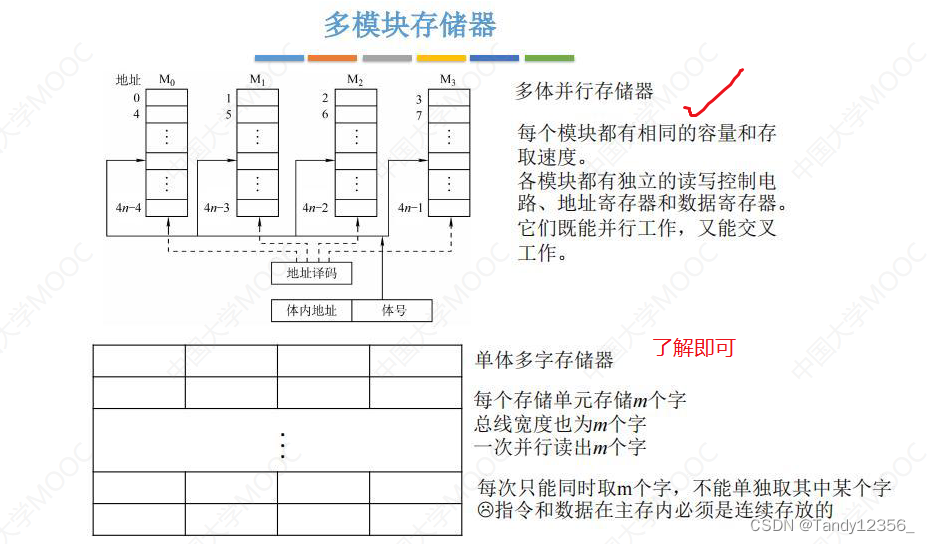

低位交叉编址,可以理解为四个内存条同时工作

当m>T/r的时候有一个存储体就会"偷懒",所以设置m=T/r就最好!发挥最大的效率!

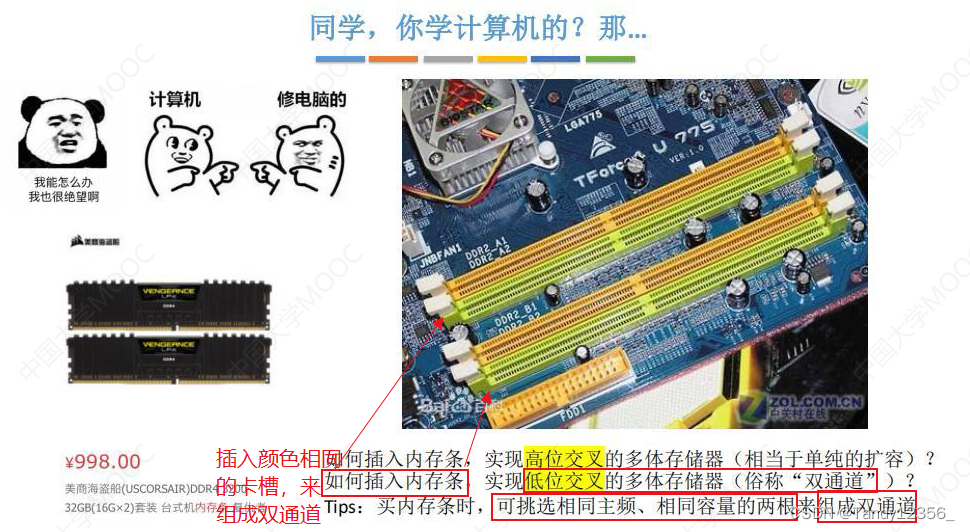

双通道内存:低位交叉的2体(多体)存储器

多体交叉存储器

不对称双通道,更大的内存条那里无法低位交叉变址,使得打游戏的时候性能不稳定,所以需要两块主频、容量都相同的内存条插在颜色相同的卡槽上来组成双通道

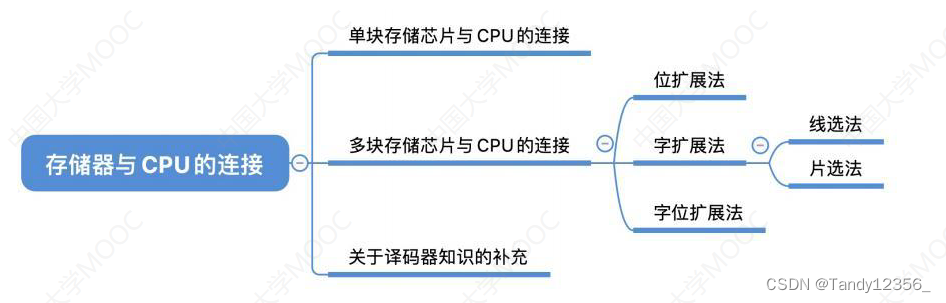

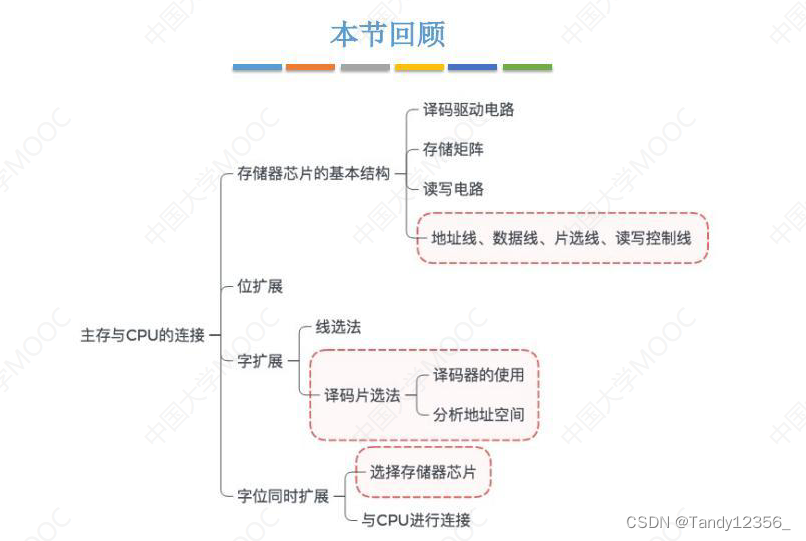

主存与CPU的连接?

多块存储芯片如何与CPU连接?

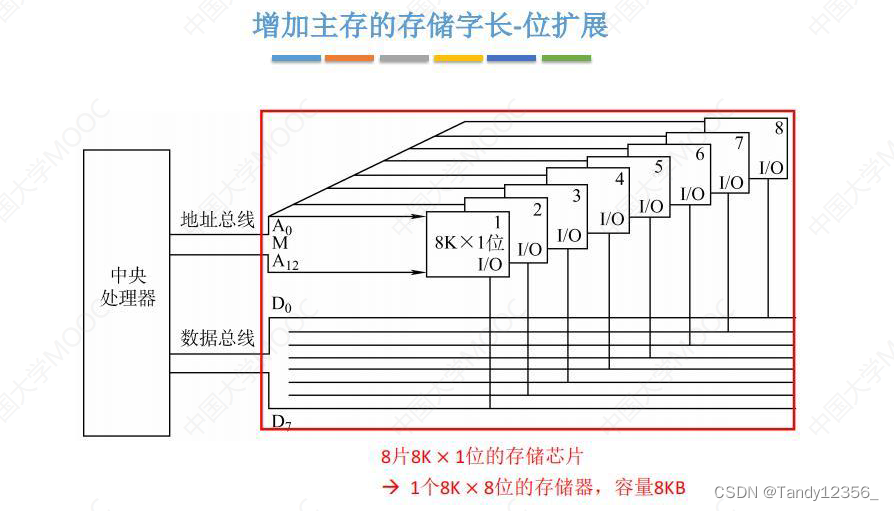

1、增加主存的存储字长(位扩展):每个芯片地址线都连上,数据线各引出一位

位扩展:增加数据的位数

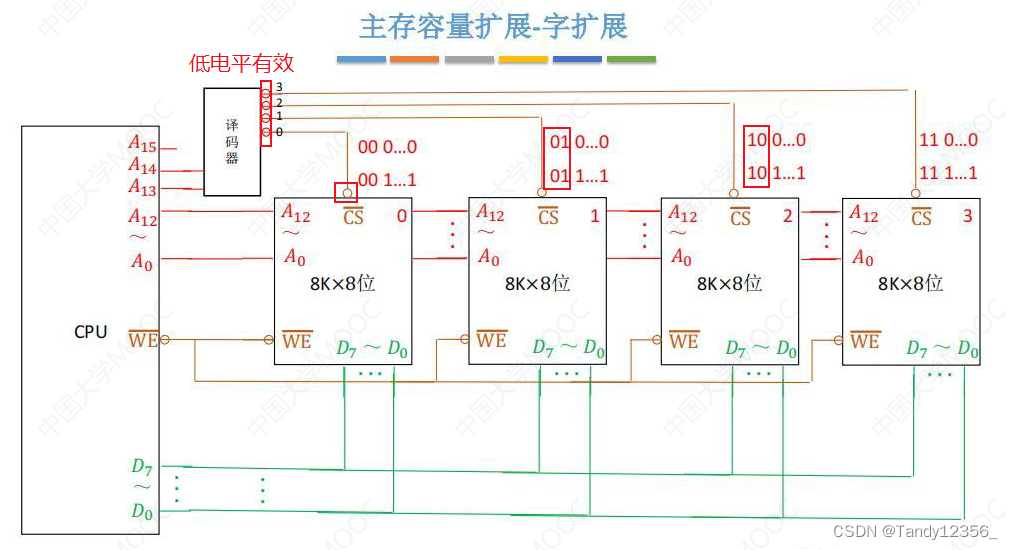

2、字扩展

字扩展:增加存储单元的总数

存储芯片的字长已经有8位了,所以不需要进行位扩展了,数据总线的传输能力已经被使用到极致了,但是CPU的寻址能力并没有被发挥到极致?

线选法:如果两块芯片的片选信号都置1的话,两块芯片的数据都会从数据总线读出,为了区分是哪块芯片,可以让他们的片选线接CPU不同的地址引脚,1代表第一块芯片,0代表第2块芯片

如何避免11 00的情况:译码器编码法

CPU的地址线和每个芯片都是相连的(A0-A12)?

A13-A15:片选线,A0-A12:地址线(每个芯片的地址线都要和CPU直接相连),但是整个字扩展的芯片对外暴露的地址引脚只有A0-A12(在芯片内部共接)

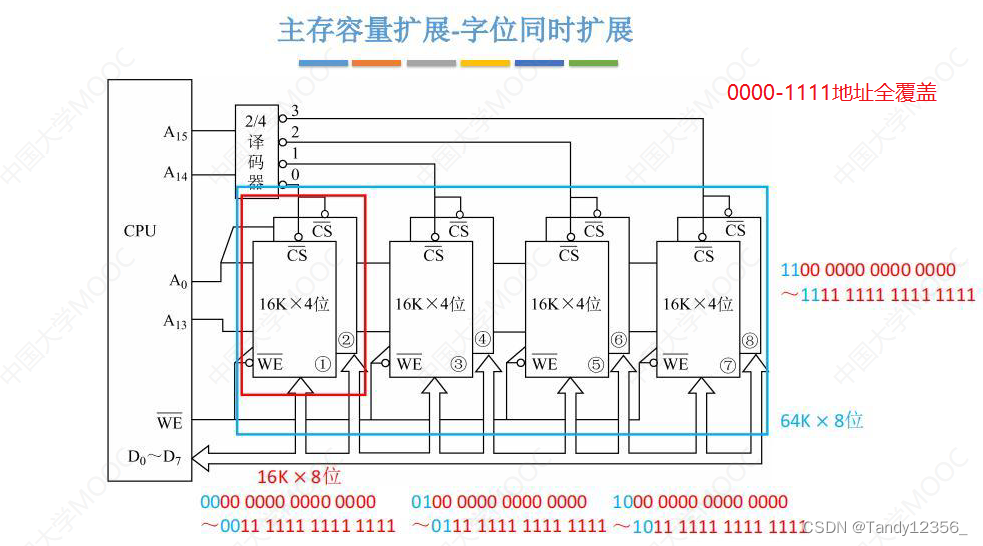

小结:位扩展可以使存储字长更长,从而更好地发挥数据总线的数据传输能力

字扩展可以增加存储器的存储字数,可以更好地利用CPU的寻址能力(范围)

二者可以从不同维度扩展主存的总容量

每两块芯片为一组实现了位扩展(4位->8位)

3-8译码器的硬件组成

使能端类似于片选线,使芯片激活

CPU确定收到稳定的数据信号之后,才会撤销刚刚发出的地址信号

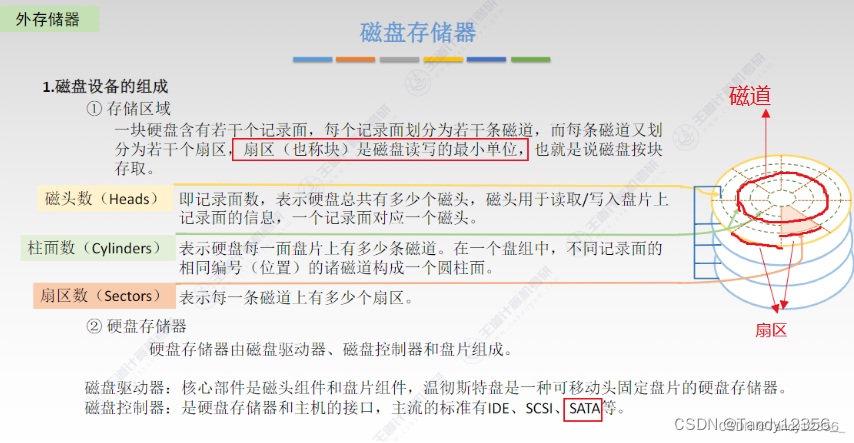

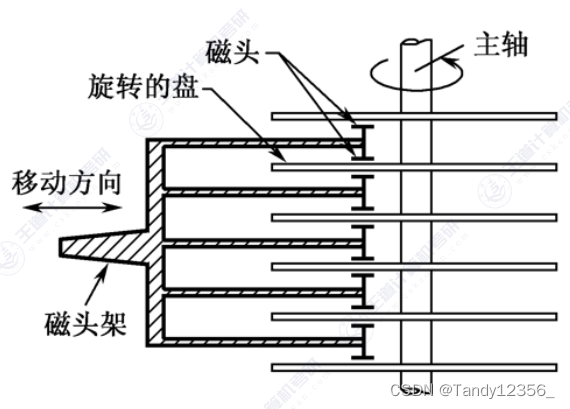

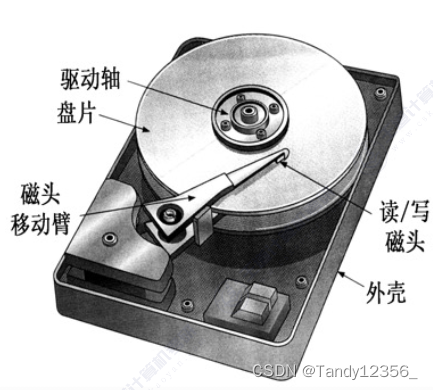

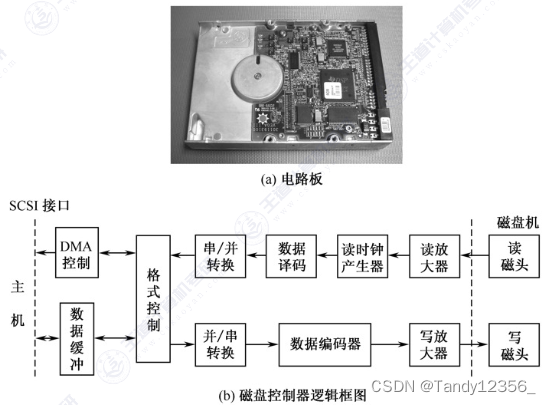

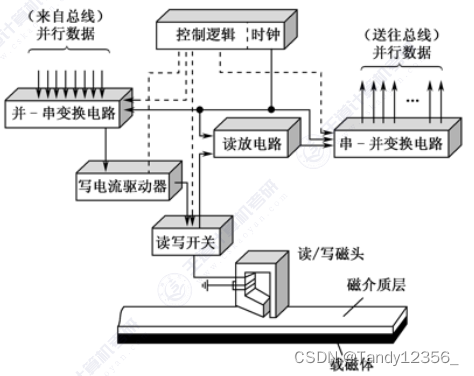

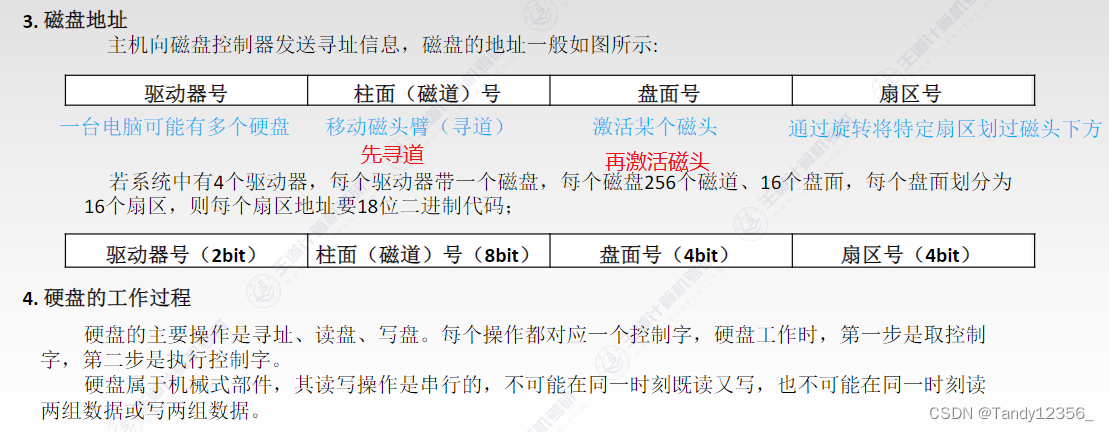

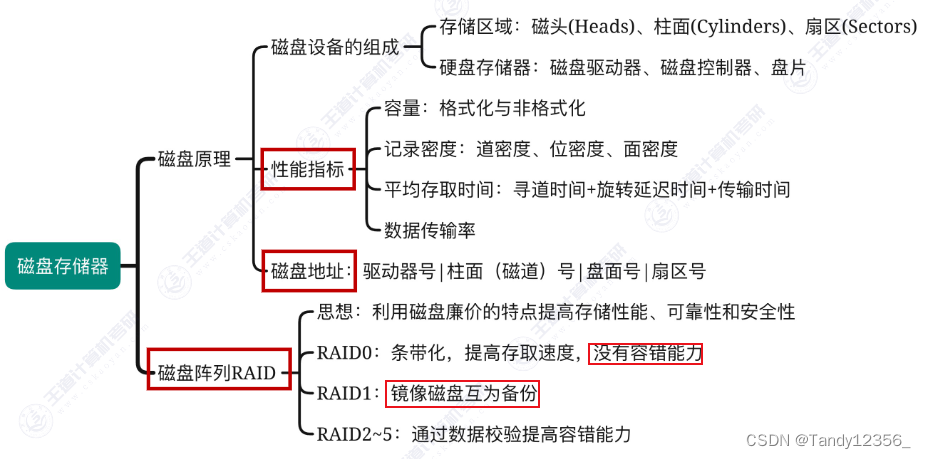

外存?

格式化:扇区A损坏了,就用扇区B来顶替?

固态硬盘?

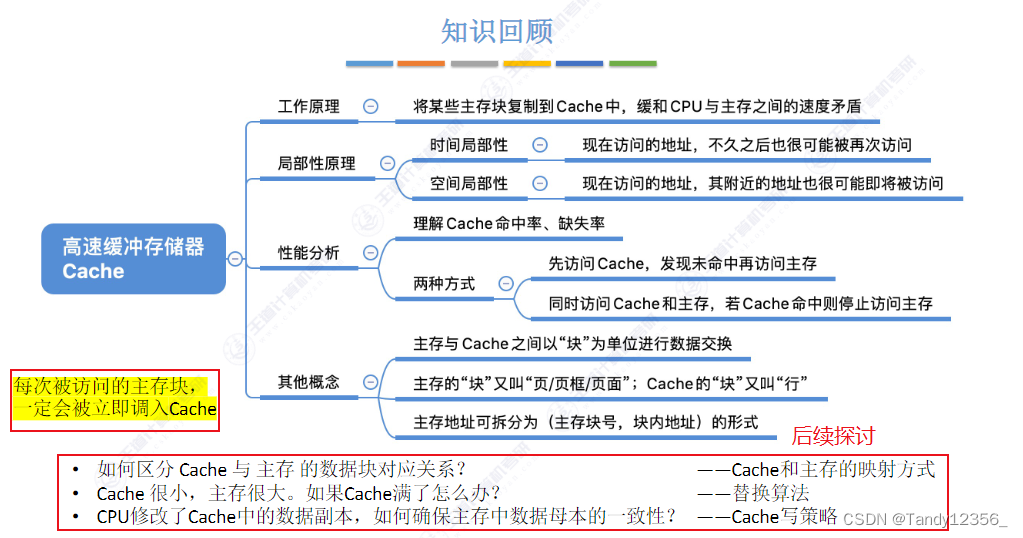

Cache的工作原理?

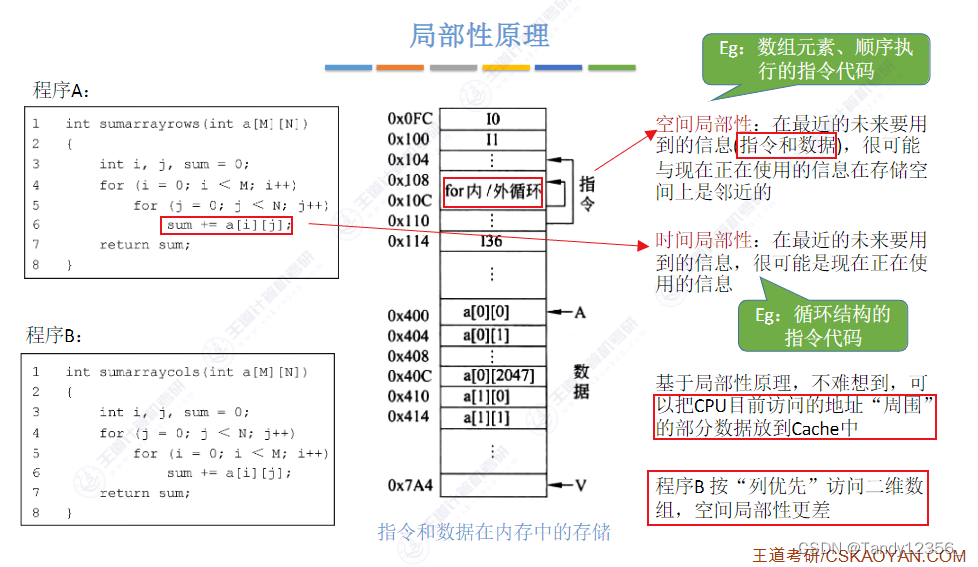

局部性原理?

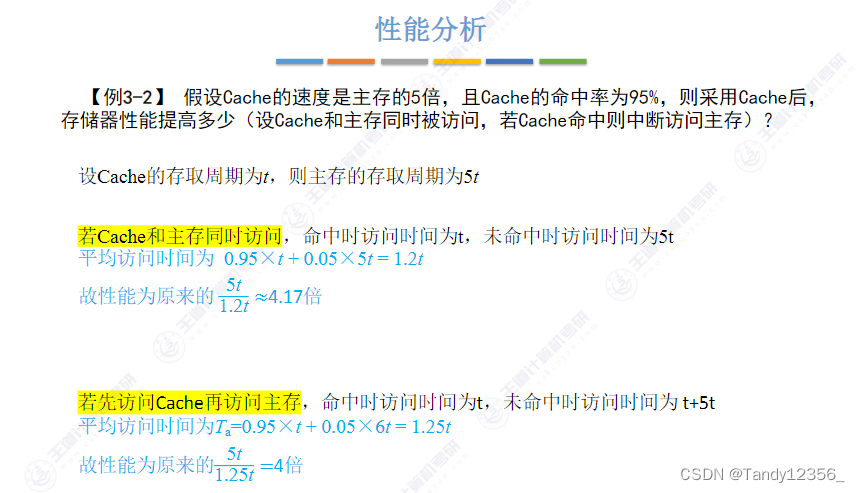

命中率H:CPU欲访问的信息已经在cache当中的比率

缺失(未命中)率M=1-H?

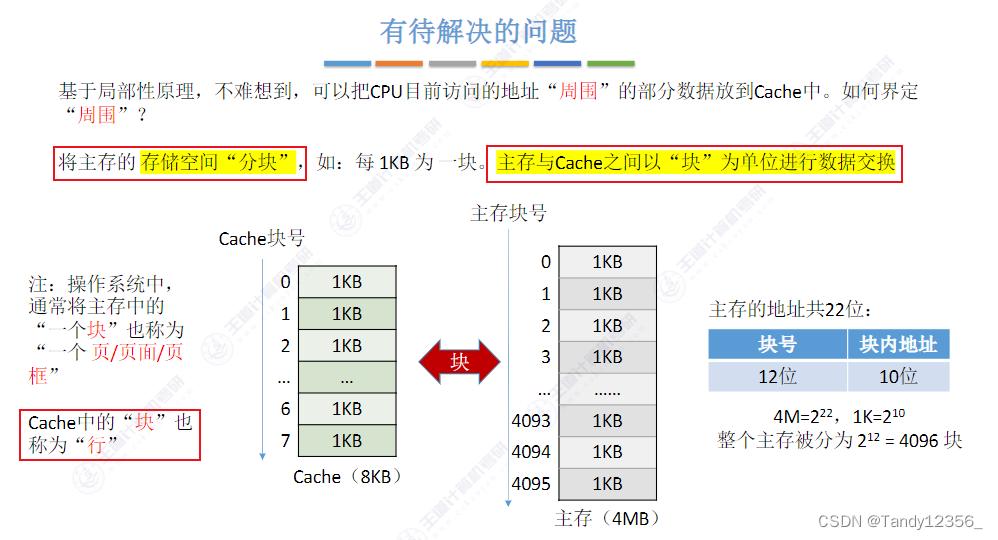

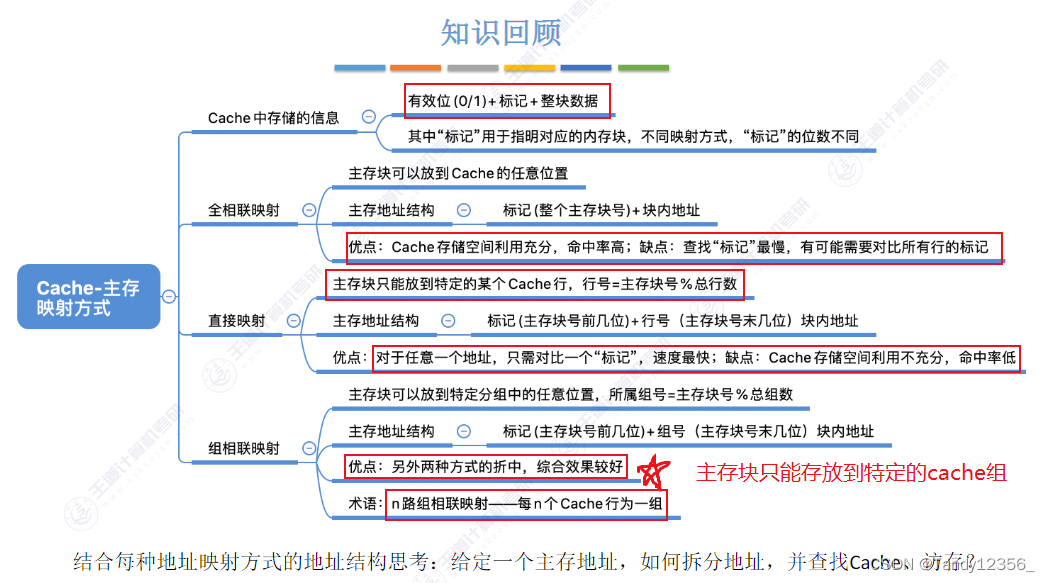

Cache和主存的映射关系

解决的问题就是主存块应当放到cache的什么位置

最终的目的就是我给你一个物理地址,怎样找到它在cache当中对应的位置!

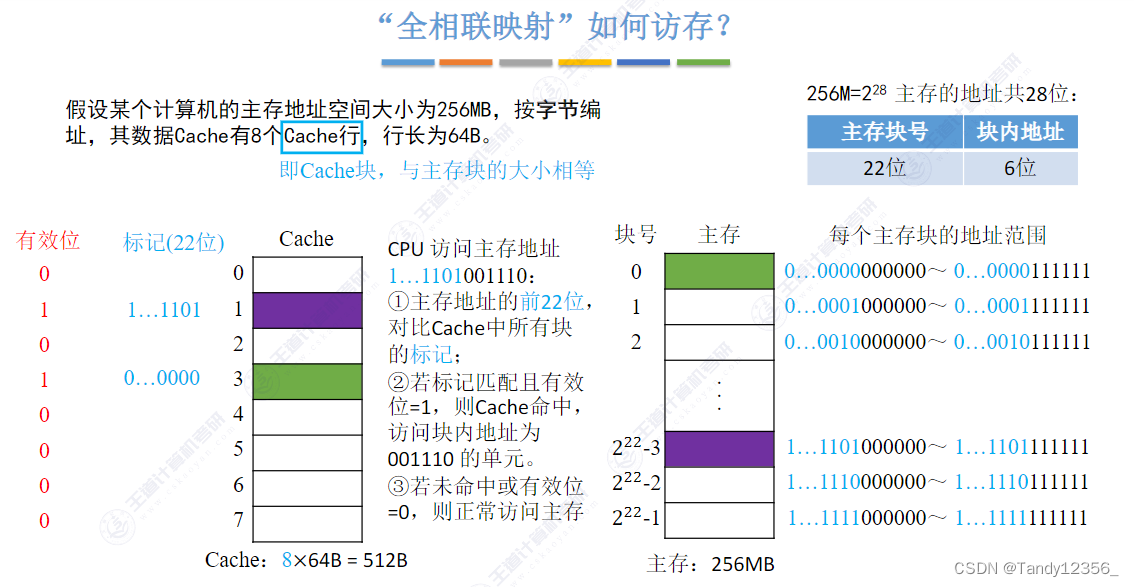

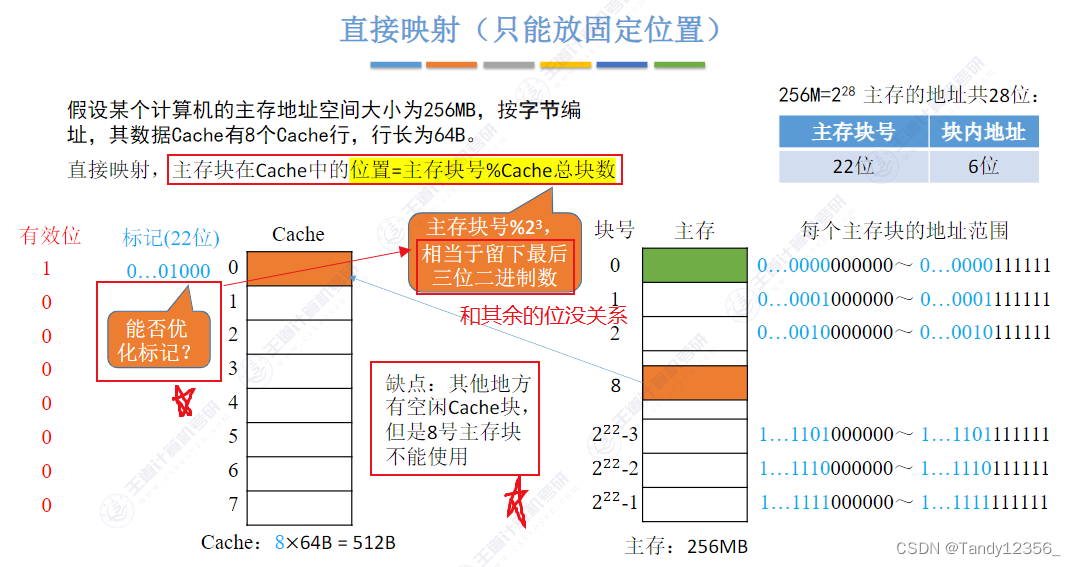

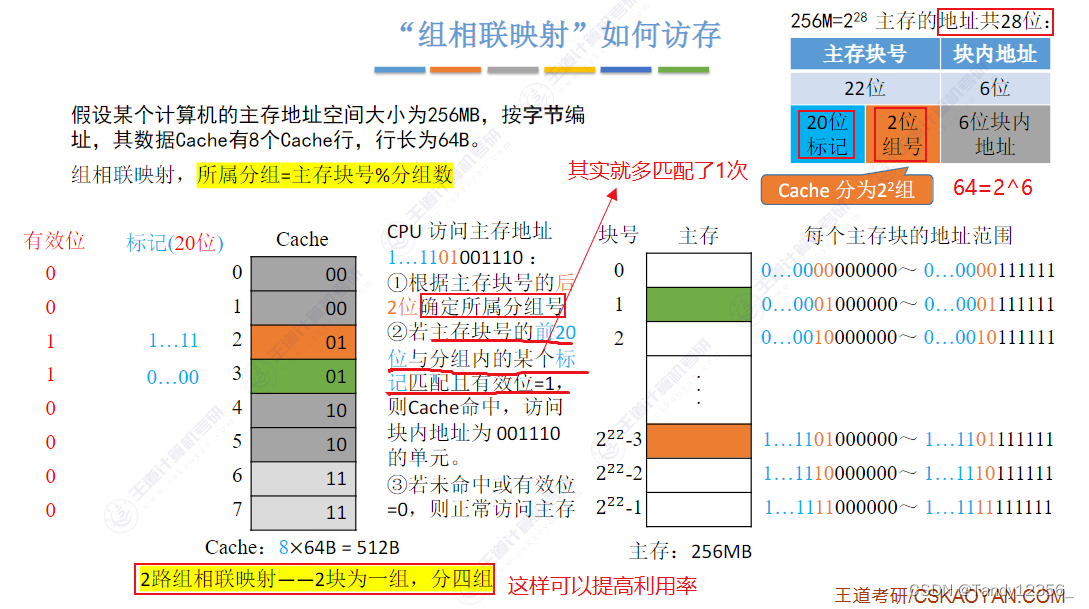

全相联映射、组相联映射、直接映射

组相联映射:映射到特定的组之后就不管了(组内哪个空闲就把哪一块分配出去)?

使用硬件实现:cache块的"标记",用于记录存储的主存块号;cache的有效位,表示是否存储主存块号

根据主存地址的块号来匹配cache的标记位

有效位:不能用标记为0来代表没有映射关系,所以要加一位有效位

全相联映射

随意放到cache的任意位置

直接相联映射

什么是标记?》标记就是主存的"短号",你标记匹配了,主存块号也就匹配了

通过物理地址里面的行号直接找到cache对应的行,然后只需要通过比较一次"标记",就可以访问对应的内容了?

组相联映射

每2个cache块为一组,总共8个cache块,一共分成4组

2路组相联映射:2块为一组,一组有2块

组相联是组号,直接映射是行号

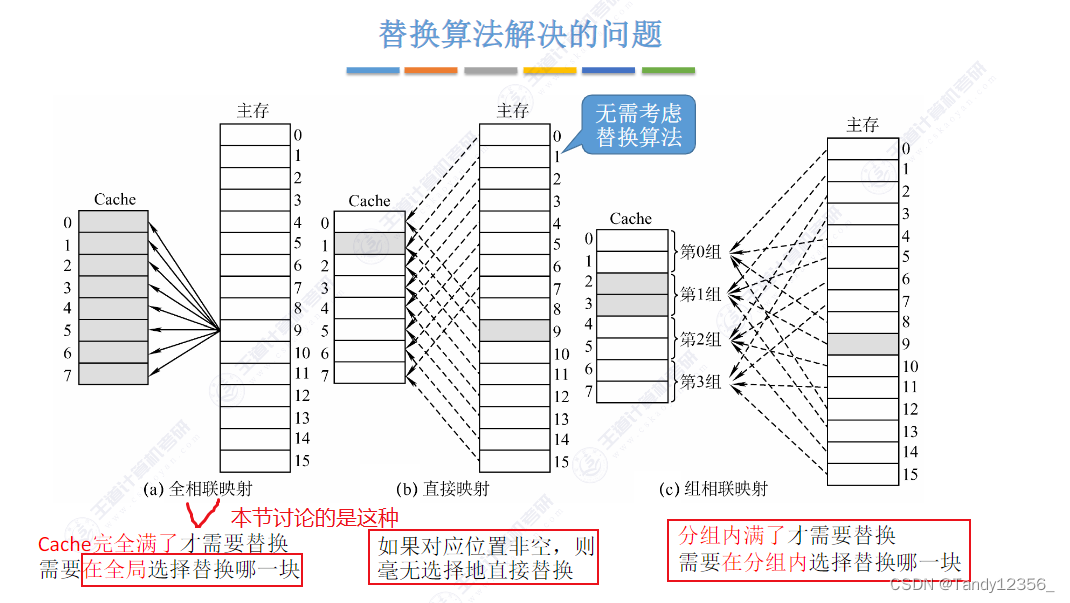

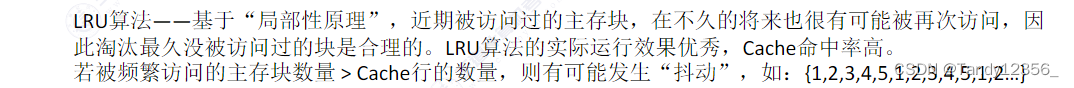

Cache替换算法?

颠簸现象:刚换出的块又被换入

cache的总块数为2^n,则只需要n位用于计数器即可

如果是组相连映射:肯定是从组内淘汰一个cache块呀!??

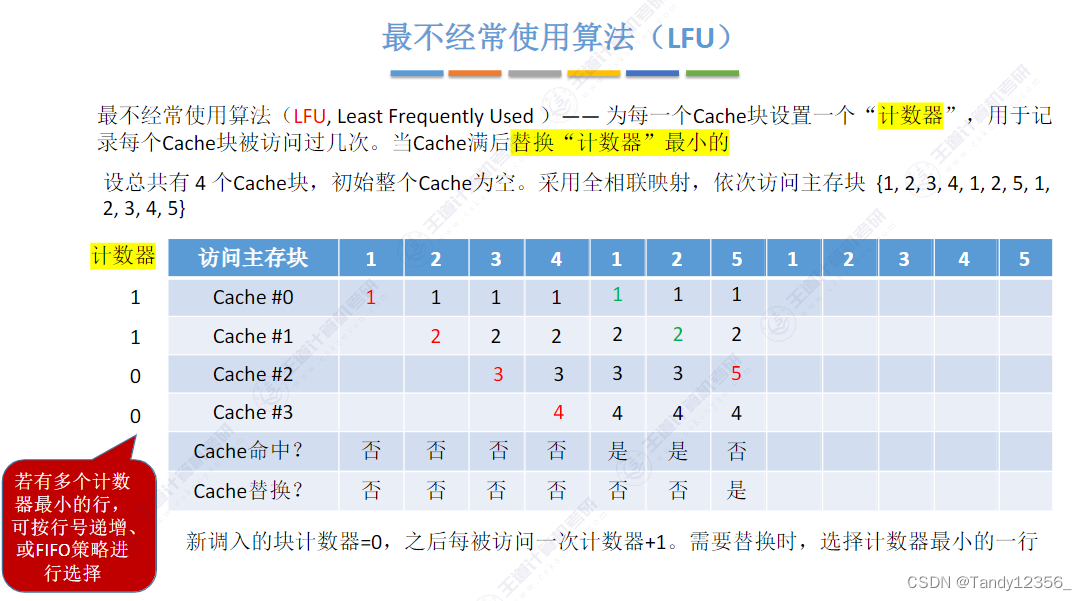

LFU:微信视频结束之后,对应的块的计数器已经很大了,在很长的时间内不会被淘汰

了解即可:

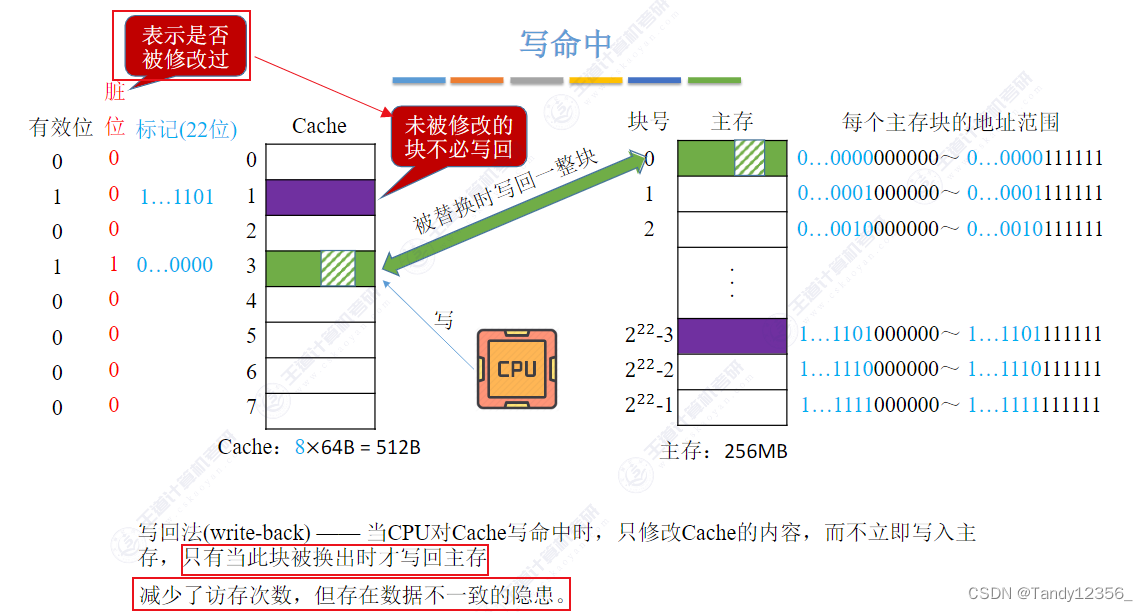

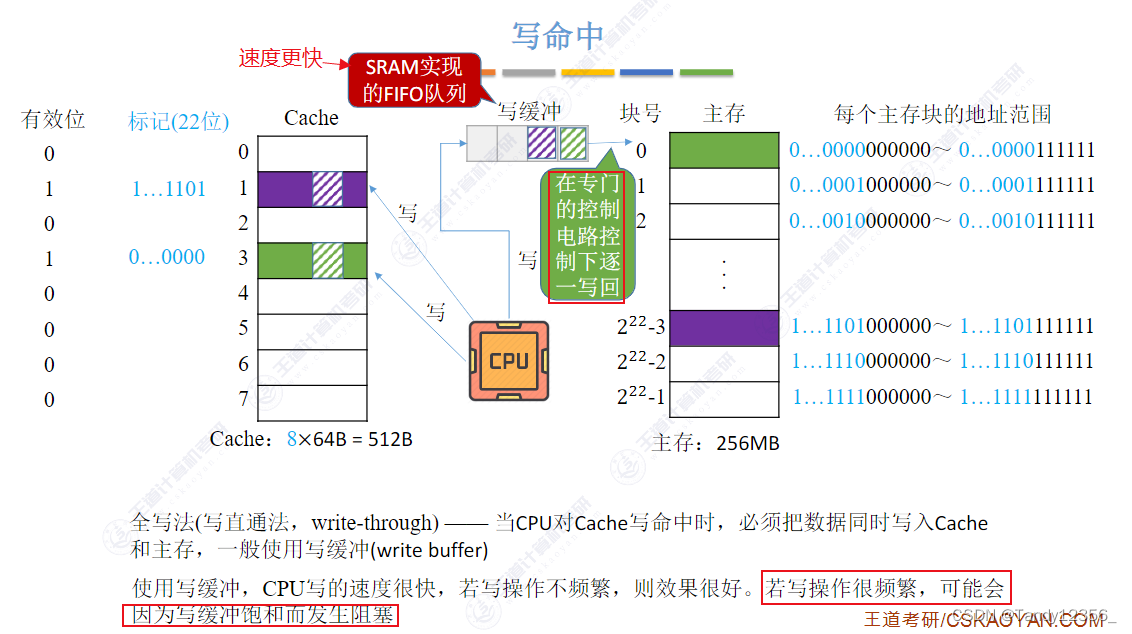

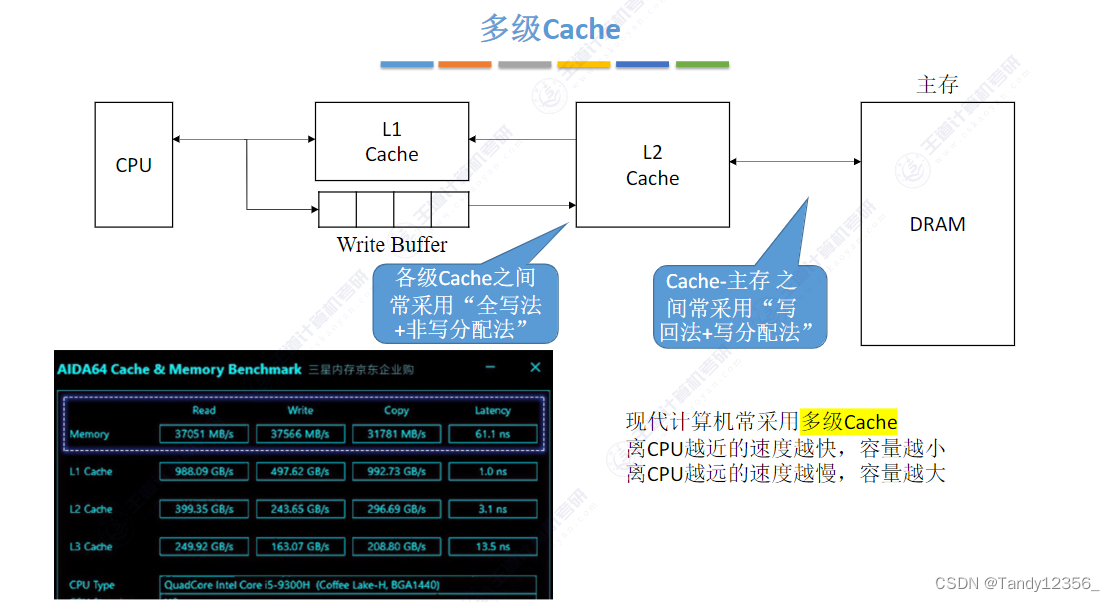

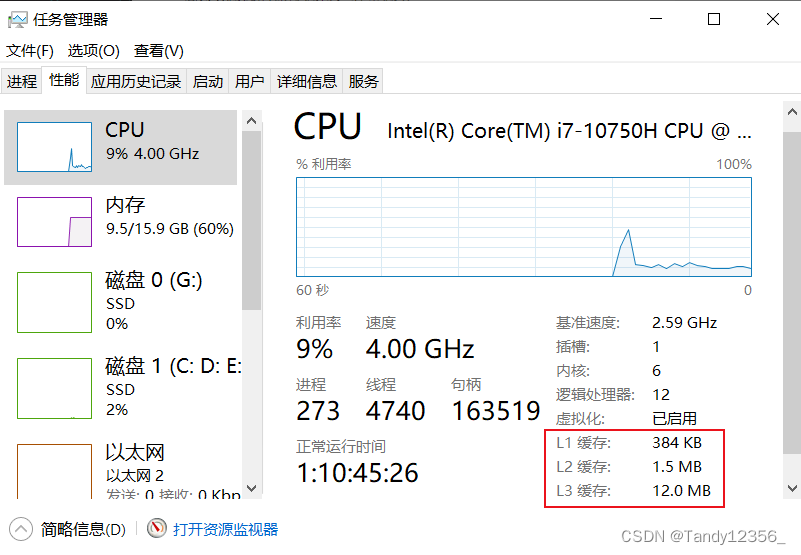

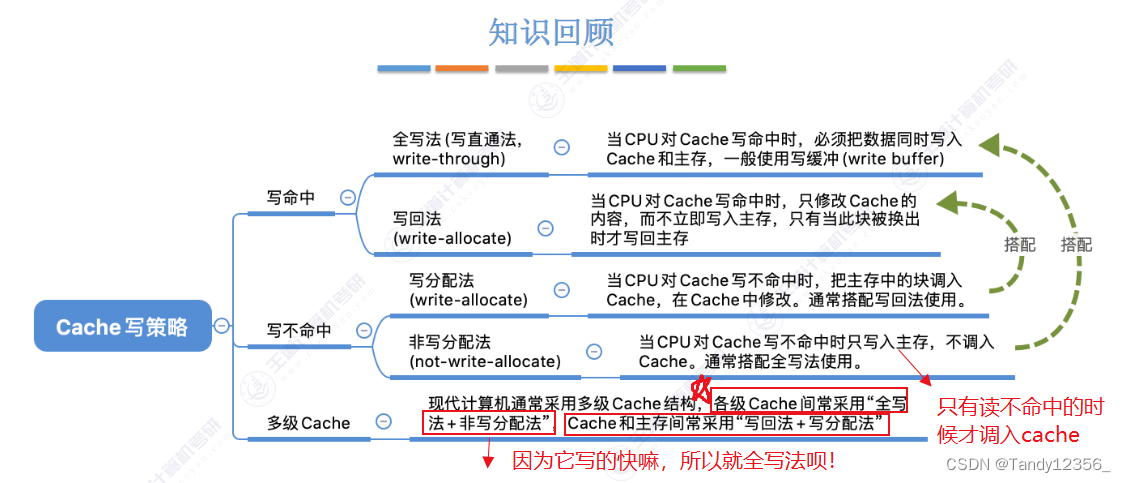

cache的写策略:CPU修改了cache当中的内容如何同步到主存当中?

当cache行被淘汰的时候才会把修改后的整个cache行写回到主存:减少了访存次数,但是存在数据不一致的隐患(由于主存的数据没有及时和cache同步,而导致主存《》磁盘交换错误的信息)

使用脏位来表示cache块的内容有没有被修改过,没有修改的块就不需要写回了

回写:

类似消息队列

直写:

?

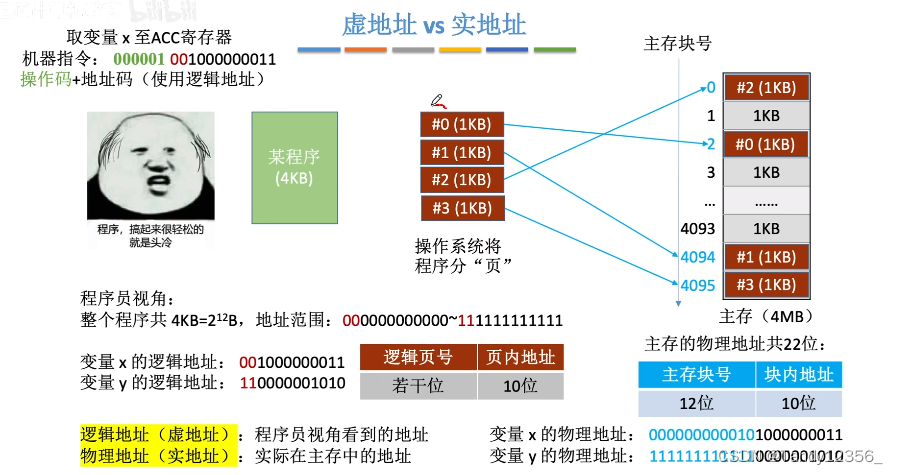

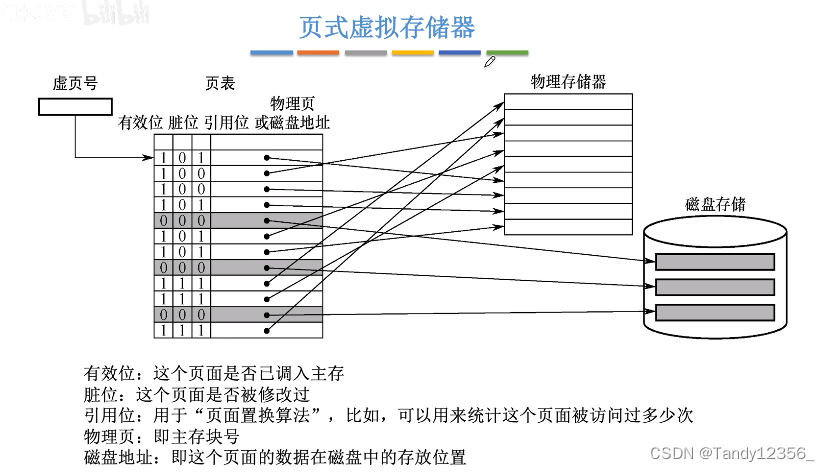

逻辑地址转换

程序员能看到的地址都是虚拟地址,都是假的

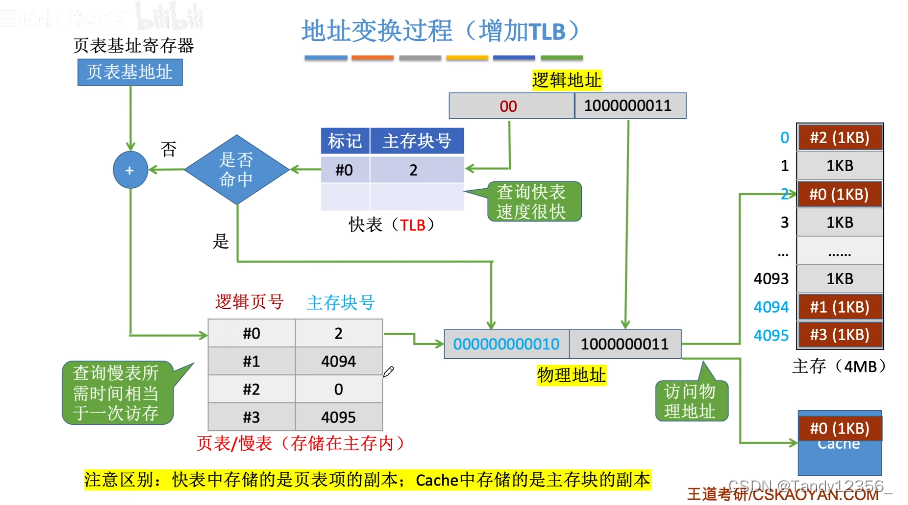

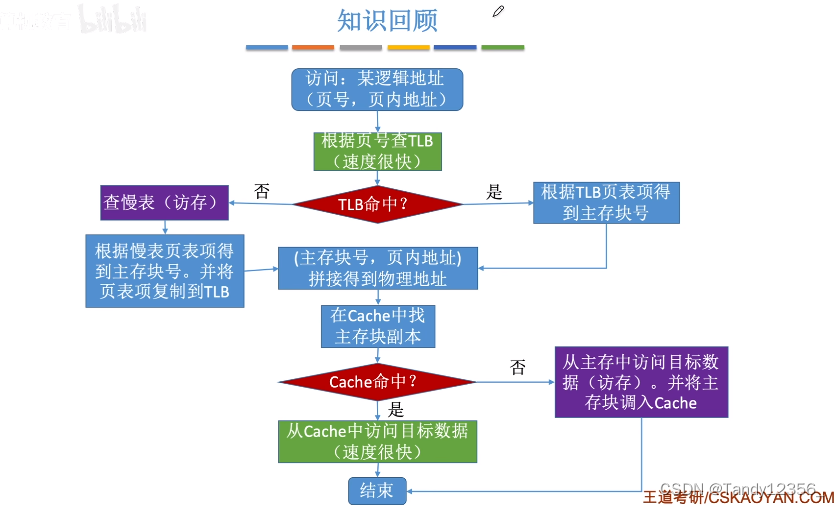

快表和cache起作用的阶段也不一样,快表TLB是在地址变换的过程中起到了加速的作用,而cache是在最终得到物理地址并访问地址的时候起到了加速的作用

所有的程序只需要调用一部分数据就可以了

打游戏的时候loading比较慢:需要将游戏地图等数据加载到内存当中

?段表要添加一个段长度字段,因为每个段的长度是不一样的。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 分析一个项目(微信小程序篇)一

- 基于LSTM的视频分类及其Matlab代码实现

- 线程Thread源代码思想学习1

- C单片机关键字extern、static 和 const

- Facebook新注册账号频被封?如何预防封号?

- 亚信安慧AntDB-S流式数据库实现企业数智化转型

- 乳腺癌预测_EDA_Models

- P5461 赦免战俘题解

- (2023|NIPS,邻域分布预测,Wasserstein 距离)通过上下文预测改进基于扩散的图像合成

- Vscode安装Eslint扩展后无法实现保存自动修复